# 数字电子学

(英文版·原书第4版)

# **Digital Electronics**

(美) 詹姆斯·比格内尔(James Bignell) 著 罗伯特·多诺万(Robert Donovan)

### 时代教育・国外高校优秀教材精选

# 数字电子学

(英文版・原书第4版)

#### **Digital Electronics**

(美) 詹姆斯·比格内尔 (James Bignell) 著 罗伯特·多诺万 (Robert Donovan)

机械工业出版社

James Bignell, Robert Donovan: Digital Electronics, 4nd Edition

(ISBN 0-7668-03287-7)

Original Edition Copyright © 2000 by Delmar. Delmar is a division of Thomson Learning. All rights reserved.

Reprinted for People's Republic of China by Thomson Learning Asia and China Machine Press under the authorization of Thomson Learning.

No part of this book may be reproduced in any form without the express written permission of Thomson Learning Asia and China Machine Press.

981 - 243 - 783 - 5

本书英文影印版由汤姆森学习出版集团 授权机械工业出版社独家出版。未经出版者书面许可,不得以任何方式抄袭、复制或节录本书的任何部分。

100

版权所有,侵权必究。

北京市版权局著作权合同登记号:图字:01-2003-2273号

#### 图书在版编目(CIP)数据

数字电子学: Digital Electronics: 第 4 版/(美) 比格内尔 (Bignell, J.), (美) 多诺万 (Donovan, R.) 著. 一北京: 机械工业出版社, 2003.6

(时代教育・国外高校优秀教材精选)

ISBN 7-111-12403-0

I. 数... □ ①比... ②多... □ . 数字电路一电子学一高等学校一教材 Ⅳ.TN79

中国版本图书馆 CIP 数据核字 (2003) 第 046409 号

机械工业出版社(北京市百万庄大街 22 号 邮政编码 100037)

责任编辑:周 娟 苏颖杰 封面设计:鞠 杨

责任印制:付方敏

北京铭成印刷有限公司印刷・新华书店北京发行所发行

2003年8月第1版第1次印刷

1000mm×1400mm 1/24・31.333 印张・2 插页・895 千字

定价: 76,00元

凡购本书,如有缺页、倒页、脱页,由本社发行部调换

本社购书热线电话 (010) 68993821、88379646

封面无防伪标均为盗版

## 国外高校优秀教材审定委员会

主任委员:

杨叔子

委员 (按姓氏笔画为序):

王先逵 王大康 白峰杉 史荣昌 朱孝禄 张润琦 张 策 陆启韶 张三慧 张福润 张延华 吴宗泽 吴 麒 宋心琦 李俊峰 佘 远 斌 陈文楷 陈立周 瑜 俞正光 范 翁海珊 龚光鲁 章栋恩 黄永畅 赵汝嘉 谭泽光

## 出版说明

随着我国加入 WTO, 国际间的竞争越来越激烈,而国际间的竞争实际上也就是人才的竞争、教育的竞争。为了加快培养具有国际竞争力的高水平技术人才,加快我国教育改革的步伐,国家教育部近来出台了一系列倡导高校开展双语教学、引进原版教材的政策。以此为契机,机械工业出版社拟于近期推出一系列国外影印版教材,其内容涉及高等学校公共基础课,以及机、电、信息领域的专业基础课和专业课。

引进国外优秀原版教材,在有条件的学校推动开展英语授课或双语教学,自然也引进了先进的教学 思想和教学方法,这对提高我国自编教材的水平,加强学生的英语实际应用能力,使我国的高等教育尽 快与国际接轨,必将起到积极的推动作用。

为了做好教材的引进工作,机械工业出版社特别成立了由著名专家组成的国外高校优秀教材审定委员会。这些专家对实施双语教学做了深入细致的调查研究,对引进原版教材提出许多建设性意见,并慎重地对每一本将要引进的原版教材一审再审,精选再精选,确认教材本身的质量水平,以及权威性和先进性,以期所引进的原版教材能适应我国学生的外语水平和学习特点。在引进工作中,审定委员会还结合我国高校教学课程体系的设置和要求,对原版教材的教学思想和方法的先进性、科学性严格把关,同时尽量考虑原版教材的系统性和经济性。

这套教材出版后,我们将根据各高校的双语教学计划,举办原版教材的教师培训,及时地将其推荐 给各高校选用。希望高校师生在使用教材后及时反馈意见和建议,使我们更好地为教学改革服务。

机械工业出版社 2002年3月

Digital Electronics 4<sup>th</sup>ed 是一本人门性教科书,不论是从应用还是从自学方面来看,对初学者都是很有帮助的教材,适用于计算机、电子信息与自动化类专业本科生使用。本书在写作风格上由浅入深,注意从应用的角度组织全书的教学内容,只要求学生具有直流和交流电路(DC/AC)的知识。本书的前3版已经以不同方式与计算机课程教学配合,一般在第一学期学习DC/AC 电路,第二学期开设本课,也可在第一学期与 DC/AC 电路同步开课;或者将数字电子学和计算机课合在一起,分成微机原理(II)、微机原理(II)作为微机硬件电路在第二、第三两个学期使用。本书不涉及晶体管和门电路的内部结构,非常适合学生自学。

本书在第 4 版的编写上突出了以下几个特点:更大程度上强调的是开发技能方面的训练,在每章都增加了技能训练内容,包括在实际应用中碰到的实际问题的处理原则。其次,每一章都增加了新的 EWB 实验,这些实验都是在电路中嵌入了故障的基础上,训练学生用 EWB 分析和解决问题,教给他们解决问题的原理、思想和方法,以及熟练地掌握 EWB 工具软件和开发技巧。第三是把可编程逻辑器件 (PLD)的内容也融合到各章内容之中,以便使 PLD 内部结构的学习循序渐进,以讨论和练习的方式学习。每章都有 PLD 应用的问题。另外,每一章都增加了数字电路在工业设计方面的应用。因此,本书可供学习数字电子技术参考。

陈文楷 北京工业大学 2003 年 4 月

## Preface

Digital Electronics, Fourth Edition, is a streamlined, no-nonsense text that is ideal for the community college, Associate of Science degree student who needs a solid, introductory background in digital electronics. No previous knowledge in digital electronics is necessary, although a good working knowledge of dc circuits helps the student feel more comfortable with the concepts of voltage, current, and resistance. Students who complete this course are well prepared for the hardware encountered in a course in microprocessors.

#### **Text Organization**

This book is organized into sixteen chapters, one for each week of a full semester. Each chapter ends with laboratory exercises that closely correlate with the chapter material. It is in these labs that the theory comes alive and practical hands-on skills are learned; a balance is struck between theory and practice. The fourth edition is organized as follows:

**Number Systems**

Binary, hexadecimal, and binary-coded decimal number systems are covered in Chapter 1, along with binary addition.

#### **Basic Gates**

Basic gates and exclusive-Ors are covered in Chapters 2 through 4. Symbols, inverted-logic symbols, Boolean expressions, truth tables, enable/inhibit and gate expansion are stressed. Shift-counter and delayed-clock waveforms are used to introduce waveform analysis. Boolean algebra and Karnaugh map methods are used to implement given truth tables. Exclusive-OR gates are used as parity generators and parity checkers and as magnitude comparators.

#### Adders

1's and 2's complement method of subtraction is introduced in Chapter 5, along with binary-coded-decimal addition, and signed 2's complement numbers. 1's complement and 2's complement adder/subtractor circuits and binary-coded-decimal adder circuits are created by using the basic gates in conjunction with 4-bit full adders.

**Specifications**

Totem-pole and open-collector outputs are contrasted in Chapter 6. TTL and CMOS subfamily characteristics and parameters are contrasted. Emitter-coupled logic is introduced.

#### Flip-Flops

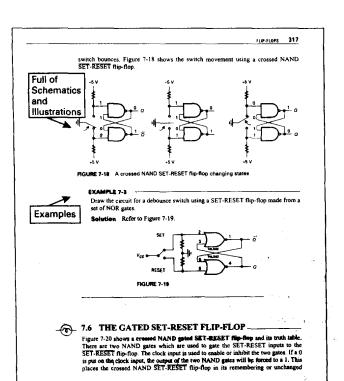

A progression of flip-flops is studied in Chapters 7 and 8, beginning with crossed NAND and progressing through gated, transparent, data, master-slave, and JK flip-flops. JK flip-flops and gates are used to create shift-counter and delayed-clock waveforms.

#### **Digital Communications**

Integrated circuit serial and parallel shift registers are presented in Chapter 9. The RS-232 standard and ASCII code are studied and a serial receiver is created from flip-flops and gates. In a "human-relations" lab exercise, four students work as a team to create a serial receiver from flip-flops and gates and shift register integrated circuits. The system includes shift-counter and delayed-clock circuits studied in Chapter 8. The lab is complete when each member of the group is able to receive and decode the RS-232 ASCII signals from a computer.

#### **Timing Circuits**

Decode-and-clear and synchronous counters are presented in Chapter 10. Both integrated circuit counters and counters created from flip-flops and gates are studied. The student learns to design and create synchronous counters that count in any sequence.

Schmitt-trigger gates are introduced in Chapter 11. Schmitt-trigger gates, 555 timers, CMOS gates, and crystals are used to create a variety of clock circuits.

Triggerable and non-retriggerable one-shot circuits are covered in Chapter 12. Both integrated circuit one-shots and one-shots created from Schmitt-trigger gates and 555 timers are studied.

#### **Interface Circuits**

Chapter 13 begins a sequence of topics concerned with interfacing digital control circuits with the external world.

Digital-to-analog and analog-to-digital converters are covered in Chapter 13. Count-up and compare, flash converters, and successive approximation converters are created with flip-flops, gates, and voltage comparators. The successive approximation circuit begins with shift-counter and delayed-clock circuits developed in Chapter 8. Integrated circuit converters are presented.

In Chapter 14, the concept of decoding is expanded into multiplexers and demultiplexers. Integrated circuit multiplexers and demultiplexers are presented. LED and liquid crystal seven-segment displays are introduced.

Chapter 15 introduces tri-state gates and bus drivers. Examples are given of interfacing control circuits to high-current, high-voltage devices.

#### Introduction to Microcomputers

Chapter 16 is a bridge from digital electronics into microcomputers. The basic parts of a microcomputer are discussed. Memory-integrated circuits are presented.

#### **Appendixes**

Appendix A contains plans and schematics for construction of a lab trainer. Appendix B contains a list of materials needed to construct the lab circuits. Pinouts for the integrated circuits used in the lab exercises are shown in Appendix C. Although handy, these pinouts are no substitute for good TTL and CMOS specification manuals (data books). It is recommended that data books be obtained from one or more of the major integrated circuit manufacturers.

#### How to Use the Book

- 1. An Outline and a list of Key Terms begins each chapter highlighting main topics and new terms the students will learn.

- 2. The Objectives for each chapter identifies the skills that the student will acquire after reading the material.

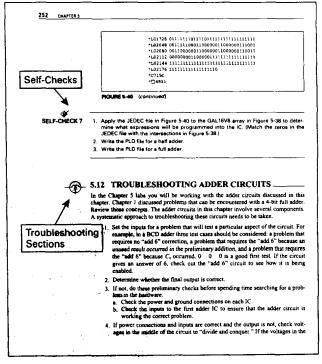

- 3. Each chapter contains Self-Check questions to keep the students focused on the material and to provide immediate feedback on their progress. The answers to the Self-Checks are included at the back of the book.

- 4. Examples are given to enhance the presentation of new material and to guide the student in solving problems.

eting the repairs, the technician notices that the stepper motor does not

After competing the repears, me rechancian notices that me support moves over a change squoids, when the high speed button is pressed. Instead of switching to the higher speed, the motor is erratic and returns to the lower speed when the high speed button is released. Measuring the voltages on the pins of the SET-RESET flip-flop, he finds that pin 5 of Ul is always low. This pin should only be low when the low speed

FLIP-FLOPS 335

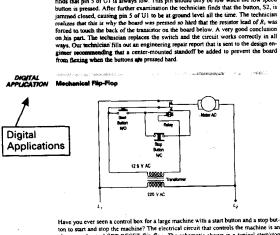

ton to start and stop the machine? I he electrical circuit had control me trialcrine is an electromechanical SET-RESET fill-riflop. The schematic shown is a typical start/stop circuit for a large machine, such as a large compressor for an air conditioner. The circuit uses a relay which can be lacked on by pushing the start button (SET input) and delatched by pushing the stop button (RESET). The relay contacts can har-dle the large as currents needed to turn the large machine on and off, but the current needed to run the relay coil is small, do you think you could design a digital circuit using NAND gates to run the relay?

- 5. A Chapter Summary lists pertinent facts for quick review and reinforcement.

- 6. End-of-chapter *Questions and Problems* offer review of material and practice at putting the material to work. The answers to odd-numbered problems are included at the back of the book.

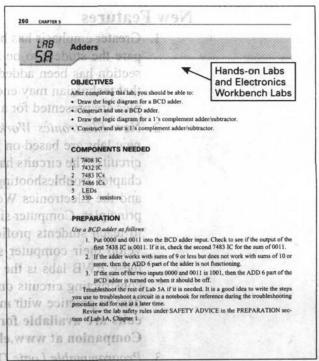

- 7. Two Labs are included at the end of each chapter. The first is a hands-on construction project and the second is an Electronics Workbench analysis and troubleshooting project. Troubleshooting competence is developed by wiring and troubleshooting the lab circuits in the first lab and then by analyzing and troubleshooting the Electronics Workbench circuits in the second lab. By using both types of labs, a balance is struck between physically constructing a circuit and analyzing/troubleshooting circuits using computer simulation tools, such as Electronics Workbench. Students need to experience both approaches to fully understand circuit problems.

- 8. Many of the words and phrases used in this text are briefly defined in the *Glossary*. Refer to it often to familiarize yourself with the terminology.

- 9. A concise, easy-to-read style presents fundamental digital concepts in clear, understandable terms.

- 10. A comprehensive text accompanied by schematics and illustrations to help clarify material.

#### **New Features**

- 1. Greater emphasis has been placed on developing troubleshooting skills to prepare the student to be more productive in the workforce. A *Troubleshooting* section has been added to each chapter, which includes real-world scenarios that technician may encounter in the field. Guidelines, techniques, and examples are presented for a logical approach to troubleshooting.

- 2. New Electronics Workbench Labs have been added to each chapter. These new labs are based on analyzing and troubleshooting Electronics Workbench circuits. The circuits have built-in faults that the student will have to find. The chapter troubleshooting sections teach troubleshooting principles and ideas and the Electronics Workbench labs provide a practical application of those principles. Computer simulation using Electronics Workbench has been added to teach students proficiency in using computer simulation tools and to develop their computer skills. Another important advantage of incorporating these EWB labs is the time saved by providing pre-built circuits rather than constructing circuits on protoboard. This presents an opportunity for the student to practice with many more circuits. (The Electronics Workbench circuits are available for download through the Digital Electronics' Online Companion at www.electronictech.com.)

- 3. Programmable Logic Devices have been integrated into the fourth edition. Beginning with Chapter 3, a section dealing with programmable logic devices has been added to each chapter. In industry, more systems are using PLDs to replace numerous integrated circuits. This new coverage on PLDs provides a starting place for the student to become aware of these new devices and an introduction to the technology behind them.

These sections are cumulative, beginning with discussions and exercises involving the internal architecture of a programmable logic device and the development of a source file (\*.PLD) to program the internal logic into the desired combinatorial logic circuit. CUPL (Compiler for Universal Programmable Logic) software from Logical Devices, Inc. is used to compile the source file into a JEDEC file (\*.JED). The JED file can then be used by an IC programming system (hardware and software) to program the actual integrated circuit. Each chapter presents an application of a PLD that is correlated to the material in the chapter.

A Universal IC Programmer/Tester by Hi-Lo Systems was used to perform the PLD exercises in this text. The software and hardware used can be purchased from any electronics components catalog, such as Jameco (www.jameco.com). Other equivalent compilers and programmers can be used to program the PLDs.

4. A Digital Application section has been added to each chapter. The applications present industry-designed circuits and scenarios to illustrate the chapter's content.

- 5. Additional Questions and Problems give the student more opportunity to review and apply concepts just learned.

- 6. Based on reviewer feedback, additional content revisions include:

- Math coverage of 1's complement subtraction and 2's complement subtraction has been moved to Chapter 5 to present material more logically.

- Applications of DeMorgan's theorems have been simplified using a three step process.

- Specification of low voltage CMOS subfamilies has been added to Chapter 6.

- Added coverage of insulated gate bipolar transistors (IGBTs) in Chapter 15

exposes students to more of these common circuits. The new section on

IBGTs demonstrates the use of digital signals to control high-current and

high-voltage devices.

- An introduction to microcontrollers and the Motorola 68HC11 has been added to Chapter 16.

- Added description of more integrated circuits throughout the text gives the student broader knowledge of available ICs.

#### **Course Options**

This text has been used three different ways at Manatee Community College.

- 1. Digital Electronics was originally written to be used as a second semester text for students who had completed DC/AC circuits during their first semester. This worked well except, with digital being introduced in the second semester, only semesters three and four remained for microprocessor-based course work.

- In order to introduce digital electronics earlier in the curriculum, it was moved

to the first semester and taught concurrently with DC/AC circuits. Both formats worked well, but digital electronics was offered only to Electronics Engineering Technology majors.

- 3. A new format has now evolved, offering a survey of digital and microprocessors to networking and programming students. This fourth edition text is used as one of two books in a two-semester sequence, Digital/Microprocessors I and II. In the first course, Digital/Micro I, number systems, gates, and flip-flops (Chapters 1 through 5, 7, and 8) are covered during the first half of the semester. Assembly language programming of a microprocessor, associated hardware, and interfacing are taught during the second half of that first semester. Students majoring in electronics return for Digital/Micro II and

study the rest of *Digital Electronics* (Chapters 6 and 9 through 14) and additional microprocessor work, including interfacing processors to serial ports, parallel ports, programmable counters, and stepper motors. This new format is working well at Manatee Community College.

#### **Supplementary Package**

The majority of our students find this text refreshing, and challenging and are excited about continuing their studies in electronics. To augment the learning process we now offer these useful supplements to accompany *Digital Electronics*.

- 1. The Laboratory Manual contains additional activities to supplement the lab exercises contained in the text. For each chapter of Digital Electronics the Laboratory Manual contains three lab exercises. The first two contain circuits to be constructed on a protoboard and analyzed. The third lab is based on Electronics Workbench Student Edition, Version 5.12, ISBN: 0-7668-0330-9. These labs are well correlated with the text material.

- 2. The *Instructor's Guide* offers teaching hints for the text and lab manual and the answers to all text and lab manual questions and problems, ISBN: 0-7668-03295.

- 3. The Digital Electronics' Online Companion at www.electronictech.com includes the downloadable Electronics Workbench circuit files required in this text and lab manual, along with text updates, online quizzes, and more.

#### Acknowledgments

We gratefully acknowledge the contributions of the following reviewers, whose valuable comments helped shape this revision:

Reviewers

Joe Baker DrVry Institute of Technology

Stanley Beima Cuiller Career Center

Ray Beets Iowa Central Community College

Gary Cauble ECPI College of Technology

R. Mark Cotner Central Vo-Tech

Donnin G. Custer Western Iowa Tech

R. Ted Etter University of Montana

Jim Farley James Rumsey Technical Institute

James Green San Juan College

Peter Kerkhoff DeVry Institute of Technology

Bill Kist New England Institute

Bill Kostas Topeka Technical College—Education America

Roger Peterson Northland Community and Technical College

Technical Accuracy Reviewers

Richard Rouse Victor Herson DeVry Institute of Technology Southeast College of Technology

We would like to thank the following companies for use of schematics: National Semiconductor Corporation, Lattice Semiconductor Corporation, and Precise Power Corporation.

#### **Market Feedback**

The authors can be reached for questions, comments, or suggestions at the following e-mail addresses. Robert Donovan can be contacted at donovar@bc.mcc.cc.fl.us and James Bignell can be contacted at biggy01@aol.com. We hope you enjoy using this text as much as we do.

James Bignell Robert Donovan October 1999

# Contents

| 出版说        | 明 iv                                                               |      |                                      | - Spine |

|------------|--------------------------------------------------------------------|------|--------------------------------------|---------|

| 序          | v                                                                  |      |                                      |         |

| Preface xi |                                                                    | 2.7  | Data Control Enable/Inhibit 63       |         |

|            |                                                                    | 2.8  | AND Gate Enable/Inhibit 63           |         |

|            |                                                                    | 2.9  | NAND Gate Enable/Inhibit 64          |         |

| 2868899 1. | · 1998年1997 - 1998年 - 11998年1998年1998年1998年1998年1998年1998年199      | 2.10 | OR Gate Enable/Inhibit 65            |         |

| 1          | NUMBER SYSTEMS 1                                                   | 2.11 | NOR Gate Enable/Inhibit 66           |         |

| 1.1        | Binary Number System 3                                             | 2.12 | Summary Enable/Inhibit 67            |         |

| 1.2        | Binary to Decimal Conversion 4                                     | 2.13 | NAND as an Inverter 68               |         |

| 1.3        | Decimal to Binary Conversion 6                                     | 2.14 | NOR as an Inverter 68                |         |

| 1.4        | Octal Number System 9                                              | 2.15 | Expanding an AND Gate 68             |         |

| 1.5        | Binary to Octal Conversion 11                                      | 2.16 | Expanding a NAND Gate 69             |         |

| 1.6        | Octal to Binary Conversion 12                                      | 2.17 | Expanding an OR Gate 69              |         |

| 1.7        | Hexadecimal Number System 13                                       | 2.18 | Expanding a NOR Gate 69              |         |

| 1.8        | Binary to Hexadecimal Conversion 14                                | 2.19 | Troubleshooting Gates 70             |         |

| 1.9        | Hexadecimal to Binary Conversion 15                                |      | Digital Application 71               |         |

| 1.10       | Binary-Coded Decimal (BCD) 16                                      |      | Summary 72 Questions and Problems 74 |         |

| 1.11       | Binary Addition 20                                                 |      | Lab 2A Gates 78                      |         |

| 1.12       | Binary Subtraction 22                                              |      | Lab 2B Gates 82                      |         |

| 1.13       | Troubleshooting a 4-Bit Adder 24                                   |      |                                      |         |

|            | Digital Application 26                                             |      |                                      |         |

|            | Summary 27                                                         |      |                                      | 1990    |

|            | Questions and Problems 28                                          | 3    | WAVEFORMS AND BOOLEAN                |         |

|            | Lab 1A 7483 4-Bit Full Adder 30<br>Lab 1B 4008 4-Bit Full Adder 36 |      | ALGEBRA                              | 85      |

|            | Lau 1B 4008 4-Bit Full Addel 30                                    | 3.1  | Waveform Analysis 87                 |         |

|            |                                                                    | 3.2  | Delayed-Clock and Shift-Counter      |         |

| •          |                                                                    |      | Waveforms 90                         |         |

| 2          | LOGIC GATES 41                                                     | 3.3  | Combinational Logic 98               |         |

| 2.1        | Gates 43                                                           | 3.4  | Boolean Theorems 100                 |         |

| 2.2        | Inverters 43                                                       | 3.5  | DeMorgan's Theorems 107              |         |

| 2.3        | OR Gates 45                                                        | 3.6  | Designing Logic Circuits 112         |         |

| 2.4        | AND Gates 50                                                       | 3.7  | AND-OR-Invert Gates 123              |         |

| 2.5        | NAND Gates 55                                                      | 3.8  | Reducing Boolean Expressions Using   |         |

| 2.6        | NOR Gates 59                                                       |      | Karnaugh Maps 126                    |         |

| vi         |                                                                    |      |                                      |         |

| 3.9<br>3.10 | Programmable Logic Devices 128 Troubleshooting Combinational Logic |              | 5.6     | 2's Complement Adder/Subtractor<br>Circuit 226 |

|-------------|--------------------------------------------------------------------|--------------|---------|------------------------------------------------|

|             | Circuits 132                                                       |              | 5.7     | Signed 2's Complement Numbers 232              |

|             | Digital Application 134                                            |              | 5.8     | Binary-Coded-Decimal Addition 238              |

|             | Summary 135                                                        |              | 5.9     | Binary-Coded-Decimal Adder Circuit 240         |

|             | Questions and Problems 137                                         |              | 5.10    | Arithmetic Logic Unit (ALU) 243                |

|             | Lab 3A Boolean Algebra 146                                         |              | 5.11    | Programming a GAL 245                          |

|             | Lab 3B Logic Converter 150                                         |              | 5.12    | Troubleshooting Adder Circuits 252             |

|             |                                                                    |              |         | Digital Application 254                        |

|             |                                                                    | - 12/4/86/34 |         | Summary 254                                    |

| 4           | EXCLUSIVE-OR GATES                                                 | 153          |         | Questions and Problems 256                     |

| 4.1         | Exclusive-OR 155                                                   |              |         | Lab 5A Adders 260                              |

| 4.2         | Enable/Inhibit 158                                                 |              |         | Lab 5B Adder Circuits 262                      |

| 4.3         | Waveform Analysis 159                                              |              |         | •                                              |

| 4.4         | Exclusive-NOR 160                                                  |              | 1262034 | ·                                              |

| 4.5         | Parity 162                                                         |              | 6       | SPECIFICATIONS AND                             |

| 4.6         | Even-Parity Generator 164                                          |              | v       | OPEN-COLLECTOR GATES 265                       |

| 4.7         | Even/Odd-Parity Generator 166                                      |              | 6.1     | TTL Subfamilies 267                            |

| 4.8         | Parity Checker 168                                                 |              | 6.2     | TTL Electrical Characteristics 267             |

| 4.9         | 9-Bit Parity Generator/Checker 170                                 |              | 6.3     | TTL Supply Currents 273                        |

| 4.10        | Comparator 175                                                     |              | 6.4     | TTL Switching Characteristics 274              |

| 4.11        | Programmable Logic Devices 181                                     |              | 6.5     | TTL Open-Collector Gates 278                   |

| 4.12        | Troubleshooting Exclusive-OR                                       |              | 6.6     | Open-Collector Applications 280                |

|             | Circuits 193                                                       |              | 6.7     | CMOS 282                                       |

|             | Digital Application 194 Summary 195                                |              | 6.8     | CMOS Subfamilies 282                           |

|             | Questions and Problems 196                                         |              | 6.9     | CMOS Specifications 285                        |

|             | Lab 4A Exclusive-Or 200                                            |              | 6.10    | Interfacing TTL to CMOS 288                    |

|             | Lab 4B Parity Generator/Checker                                    | 202          | 6.11    | Low Voltage CMOS 291                           |

|             |                                                                    |              | 6.12    | Emitter Coupled Logic (ECL) 293                |

| ann         |                                                                    | <b>5</b> 3 5 | 6.13    | Interfacing ECL to Other Logic                 |

| 5           | ADDERS                                                             | 205          |         | Families 295                                   |

|             |                                                                    | 200          | 6.14    | Surface Mount Technology 296                   |

| 5.1         |                                                                    |              | 6.15    | GAL Specifications 298                         |

| 5.2         | Full Adder 208  Pinary 1's Complement Subtraction                  | 216          | 6.16    | Troubleshooting TTL and CMOS                   |

| 5.3         | Binary 1's Complement Subtraction 1's Complement Adder/Subtractor  | 210          |         | Devices 299 Digital Application 300            |

| 5.4         | Circuit 218                                                        |              |         | Digital Application 300 Summary 302            |

| 5.5         |                                                                    | 223          |         | Questions and Problems 302                     |

| 0.0         |                                                                    |              |         | -                                              |