# 7th Symposium on Computer Arithmetic

Proceedings 1985 The papers appearing in this book comprise the proceedings of the meeting mentioned on the cover and title page. They reflect the authors' opinions and are published as presented and without change, in the interests of timely dissemination. Their inclusion in this publication does not necessarily constitute endorsement by the editors, IEEE Computer Society Press, or the Institute of Electrical and Electronics Engineers. Inc.

Published by IEEE Computer Society Press 1109 Spring Street Suite 300 Silver Spring, MD 20910

Copyright and Reprint Permissions: Abstracting is permitted with credit to the source. Libraries are permitted to photocopy beyond the limits of U.S. copyright law for private use of patrons those articles in this volume that carry a code at the bottom of the first page, provided the per-copy fee indicated in the code is paid through the Copyright Clearance Center, 29 Congress Street, Salem, MA 01970. Instructors are permitted to photocopy isolated articles for noncommercial classroom use without fee. For other copying, reprint or republication permission, write to Director, Rublishing Services, IEEE, 345 E. 47 St., New York, NY 10017. All rights reserved. Copyright © 1985 by The Institute of Electrica: and Electronics Engineers, Inc.

IEEE Catalog Number 85CH2146-9 Library of Congress Number 85-60193 IEEE Computer Society Order Number 632 ISBN 0-8186-0632-0 (Paper) ISBN 0-8186-4632-2 (Microfiche) ISBN 0-8186-8632-4 (Casebound)

Order from: IEEE Computer Society

Post Office Box 80452

Worldway Postal Center

Los Angeles, CA 90080

IEEE Service Center 445 Hoes Lane Piscataway, NJ 08854

THE INSTITUTE OF ELECTRICAL AND ELECTRONICS ENGINEERS, INC.

### **foreword**

The 7th Symposium on Computer Arithmetic (ARITH-7) was held at the University of Illinois in Urbana, Illinois, on June 4-6, 1985. A total of 47 papers were accepted for presentation. These papers covered theoretical foundations, arithmetic algorithms, processor architectures, hardware and software implementations, error controls and advanced applications of high-speed and high-accuracy arithmetic systems in modern digital computers. This year's symposium is divided into 11 technical sessions. The sessions include efficient adders and ALU designs, fast multipliers and dividers, floating-point arithmetic, systolic arithmetic schemas, directions in computer arithmetic, elementary function evaluation, rational and residue arithmetic, signal and image processing, large-scale scientific computations, fault-tolerant arithmetic, and new arithmetic systems.

Contributions to this Proceedings were made by 82 authors from almost all parts of the world. However, the majority of the papers received were from North America. All the previous symposia on computer arithmetic were held in the U.S.; however, ARITH-6 was held in Aarhus, Denmark in 1983. The interval between successive meetings in the series has been reduced from three years to two years in the last three meetings (1981, 1983, and 1985). This prompts us to suggest that the future symposia will be held alternately between North America and other continents every two-year period.

We would like to thank all the authors, referees, and program committee members for their contributions and timely efforts in promoting the scientific quality of this Symposium. Listed below are the referees and individuals whose efforts should be particularly acknowledged.

| Agrawal, D.P.<br>Aiso, Hideo |

|------------------------------|

| Atkins, Daniel E.            |

| Avižienis, Algirdas          |

| Bohlender, Gerd              |

| Brent, R.P.                  |

| Capello, Peter R.            |

| De Mori, Renato              |

| Despain, Alvin               |

| Ercegovac, Milos D.          |

| Farhanz, Massoud             |

| Fisher, P.D.                 |

| Flynn, Michael J.            |

| Garner, Harvey L.            |

| Hennessy, John L.   |

|---------------------|

| Irwin, Mary Jane    |

| Jayakumar, R.       |

| Kong, Vivian        |

| Kornerup, Peter     |

| Kulisch, Ulrich     |

| Kung, H.T.          |

| Li, H.F.            |

| Matula, David       |

| Milutinovic, Velkjo |

| Ni, Lionel M.       |

| Ong, Shauchi        |

| Osteeby, Ole        |

| Piestrak, Stanislaw |

| *                   |

| Ramakrishnan, I.V.<br>Rao, T.R.N.<br>Robertson, James |

|-------------------------------------------------------|

| Swartzlander Jr., Earl                                |

| Tanimoto, Steven L.                                   |

| Taylor, Fred J.                                       |

| Torng, H.C.                                           |

| Tseng, Ping-Shing                                     |

| Tu, Paul                                              |

| Uhr, Leonard                                          |

| Ullman, Jeffrey D.                                    |

| Wakerly, John F.                                      |

| Woo, Bob Y.                                           |

| Xu, Zhiwei                                            |

Thanks are also due to the IEEE Computer Society, the Technical Committee on Computer Architecture, and the University of Illinois for sponsoring and hosting this symposium. With the consent of the Program Committee, we dedicate the Proceedings of the 7th Symposium on Computer Arithmetic to Professor James E. Robertson for his pioneering and continuing contributions to this area. We believe that the various generations of his students and all participants of this symposium will join us in wishing Professor Robertson good health and many happy returns to join us in the future symposia on computer arithmetic.

Kai Hwang University of Southern California Daniel D. Gajski Ahmed Sameh University of Illinois

### Conference Committee

### General Chairman:

Daniel D. Gajski, University of Illinois

### General Cochairman:

Ahmed Sameh, University of Illinois

### **Publicity Chairwoman:**

Mary J. Irwin, Pennsylvania State University

### **Program Chairman:**

Kai Hwang, University of Southern California

### **Program Committee:**

Hideo Aiso, Keio University Daniel Atkins, University of Michigan Algirdas Avižienis, University of California, Los Angeles Milos Ercegovac, University of California, Los Angeles Michael Flynn, Stanford University Harvey Garner, University of Pennsylvania Mary Irwin, Pennsylvania State University Peter Kornerup, Aarhus University Ulrich Kulisch, University of Karlsruhe H.T. Kung, Carnegie-Mellon University David W. Matula, Southern Methodist University Lionel Ni, Michigan State University T.R. Rao, University of Southwestern Louisiana Earl Swartzlander, Jr., TRW Fred Taylor, University of Florida D.P. Agrawal, North Carolina State University Bob Y. Woo, Weitek Corporation

# History of IEEE Meetings on Computer Arithmetic

| 1. June 16, 1969    | One-day workshop<br>preceding the IEEE Computer Group Conference<br>Minneapolis, MN<br>Organized by R.R. Shively                        |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 2. May 15-16, 1972  | One-and-a-half day symposium<br>University of Maryland, College Park, MD<br>Organized by H.L. Garner and D.E. Atkins                    |

| 3. Nov. 19-20, 1975 | Two-day symposium<br>Southern Methodist University, Dallas, TX<br>Organized by T.R.N. Rao and D.W. Matula                               |

| 4. Oct. 25-27, 1978 | Two-and-a-half day symposium<br>UCLA, Los Angeles, CA<br>Organized by A. Avižienis and M.D. Ercegovac                                   |

| 5. May 18-19, 1981  | Two-day symposium plus tutorial<br>University of Michigan, Ann Arbor, MI<br>Organized by K.S. Trivedi and D.E. Atkins                   |

| 6. June 20-22, 1983 | Three-day symposium Aarhus University Aarhus, Denmark Organized by T.R.N. Rao and P. Kornerup                                           |

| 7. June 4-6, 1985   | Two-and-a-half day symposium<br>University of Illinois<br>Urbana, Illinois<br>Organized by Kai Hwang, Daniel D. Gajski, and Ahmed Sameh |

### **Table of Contents**

| Fore | eword                                                                                                                            | iii |

|------|----------------------------------------------------------------------------------------------------------------------------------|-----|

| Con  | ference Committee                                                                                                                | ٧   |

| Hist | ory of IEEE Meetings on Computer Arithmetic                                                                                      | vii |

|      | sion 1: Efficient Adders and ALU Designs<br>air: Daniel Atkins)                                                                  |     |

|      | ·                                                                                                                                | 2   |

|      | Some Optimal Schemes for ALU Implementation in VLSI Technology                                                                   | 2   |

|      | Regular, Area-Time Efficient Carry-Lookahead Adders TF. Ngai, Stanford University, and M.J. Irwin, Pennsylvania State University | 9   |

|      | A Multioperand Two's Complement Addition Algorithm                                                                               | 16  |

|      | Improved Normalization Results for Digit On-Line Arithmetic                                                                      | 20  |

| 1.5  | Efficient Serial-Parallel Arrays for Multiplication and Addition                                                                 | 28  |

| Ses  | sion 2: Fast Multipliers and Dividers                                                                                            |     |

| (Ch  | air: Earl Swartzlander, Jr.)                                                                                                     |     |

| 2.1  | Design of a Fast Inner Product Processor                                                                                         | 38  |

| 2.2  | Design for a Recursive Parallel Multiplier                                                                                       | 44  |

| 2.3  | A Division Algorithm with Prediction of Quotient Digits                                                                          | 51  |

| 2.4  | Fast Multipliers for Two's-Complement Numbers in Serial Form                                                                     | 57  |

| 2.5  | Radix 16 SRT Dividers with Overlapped Quotient Selection Stages                                                                  | 64  |

| Ses  | sion 3: Floating-Point Arithmetic                                                                                                |     |

| (Ch  | air: William Kahan)                                                                                                              |     |

| 3.1  | Axiomatizations of Floating Point Arithmetics                                                                                    | 74  |

| 3.2  | High-Speed Computation of Unary Functions                                                                                        | 82  |

| 3.3  | Floating-Point Arithmetic on a Reduced-Instruction-Set Processor                                                                 | 86  |

| 3.4  | VLSI Floating-Point Processors                                                                                                   | 93  |

|      | A Family of CMOS Floating Point Arithmetic Chips                                                                                 | 101 |

| Ses               | sion 4: Systolic Arithmetic Schemas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| (Ch               | air: Daniel Gajski)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|                   | Systolic Polynomial Evaluation and Matrix Multiplication with Multiple Precision J. Schaeffer and D. Makarenko, <i>University of Alberta, Canada</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|                   | A Systolic Algorithm for Integer GCD Computation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 118 |

| 4.4               | Expansion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|                   | E.T. Chow and D.I. Moldovan, University of Southern California                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|                   | sion 5: Panel Discussions on Directions in Computer Arithmetic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| Ger<br>Uni<br>Uni | oderator: Kai Hwang; Panelists: U. Kullsch, University of Karlsruhe,<br>many; J. Robertson, University of Illinois; D. Matula, Southern Methodist<br>iversity; E. Swartzlander, TRW Defense Systems Group; H. Aiso, Keio<br>iversity, Japan; B. Woo, Weitek Corp.; M. Ercegovac, University of<br>ifornia, Los Angeles; and L. Dadda, Politecnico di Milano, Italy)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|                   | sion 6: Elementary Function Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| (Ch               | air: Mary J. Irwin)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|                   | The Modified Cordic Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|                   | Polynomial Transformer T. Kurokawa and H. Aiso, Keio University, Japan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|                   | The VLSI Implementation of a Square Root Algorithm  J. Bannur and A. Varma, University of Southern California, Los Angeles  A Biratina Architecture for Council Control of Council Control of Council Control of Council Control of Council |     |

|                   | A Pipeline Architecture for Computing Cumulative Hypergeometric Distributions X. Li, Wichita State University, and L.M. Ni, Michigan State University                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| 0.5               | Squarers for Binary Numbers in Serial Form                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1/3 |

| Ses               | sion 7: Rational and Residue Arithmetic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|                   | pair: Fred J. Taylor)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|                   | Multi-Input Residue Arithmetic Utilizing Read-Only Associate Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|                   | Binary Paradigm and Systolic Array Implementation for Residue Arithmetic  D.Y.Y. Yun and C.N. Zhang, Southern Methodist University  Rationally Biased Arithmetic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|                   | W.E. Ferguson, Jr., and D.W. Matula, Southern Methodist University  VLSI Residue Multiplier Modulo a Fermat Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 194 |

| 7.4               | I.S. Reed, T.K. Truong, University of Southern California, Los Angeles, J.J. Chang, H.M. Shao, and I.S. Hsu, Jet Propulsion Laboratory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 203 |

| <b>7.</b> 5       | Finite-Precision Lexicographic Continued Fraction Number Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 207 |

| Ses               | sion 8: Arithmetic in Signal/Image Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| (Ch               | nair: Peter Kornerup)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|                   | Three-Dimensional IC's and an Application to High Speed Image Processor<br>K. Taniguchi, Toshiba Corp., Japan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 8.2               | Arithmetic for High Speed FFT Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 223 |

| 8.3 The Design of a Vector-Radix 2DFFT Chip                                                                             | 31              |

|-------------------------------------------------------------------------------------------------------------------------|-----------------|

| 8.4 PAPIA: Pyramidal Architecture for Parallel Image Analysis                                                           |                 |

| 8.5 A More Efficient Residue Arithmetic Implementation of the FFT                                                       | 43              |

| Session 9: Large-Scale Scientific Computations                                                                          |                 |

| (Chair: Ahmed Sameh)                                                                                                    |                 |

| 9.1 On the Structure of Parallelism in a Highly Concurrent PDE Solver                                                   |                 |

| 9.2 A Parallel Method for Computing the Generalized Singular Value Decomposition 26 F.T. Luk, Cornell University        |                 |

| 9.3 Multiprocessors for Evaluating Compound Arithmetic Functions                                                        |                 |

| 9.4 A Fast Algorithm for the Symmetric Eigenvalue Problem                                                               | :/6             |

| Session 10: Fault-Tolerant Arithmetic                                                                                   |                 |

| (Chair: Irving Reed)                                                                                                    |                 |

| <ul><li>10.1 Multiple Error Correction and Additive Overflow Detection with Magnitude Indices in Residue Code</li></ul> | !78             |

| 10.2 Arithmetic Algorithms for Operands Encoded in Two-Dimensional Low-Cost Arithmetic Error Codes                      | :85             |

| 10.3 A Class of A(N+C) Codes and Its Properties                                                                         |                 |

| 10.4 Maximal Redundancy Signed-Digit Systems                                                                            | !9 <del>6</del> |

| Session 11: New Arithmetic Systems                                                                                      |                 |

| (Chair: Harvey Garner)                                                                                                  |                 |

| 11.1 Higher Order Computer Arithmetic                                                                                   |                 |

| 11.2 DRAFT: A Dynamically Reconfigurable Processor for Integer Arithmetic                                               | 309             |

| 11.3 ACRITH: High-Accuracy Arithmetic—An Advanced Tool                                                                  | 340             |

| for Numerical Computation                                                                                               | 518             |

| 11.4 Anomalies in the IBM ACRITH Package                                                                                | <b>32</b> 2     |

| 11.5 Complex Interval Division with Maximum Accuracy                                                                    | 332             |

| Author Index                                                                                                            | 242             |

# Session 1 Efficient Adders and ALU Designs

**Chair** Daniel Atkins

# SOME OPTIMAL SCHEMES FOR ALU IMPLEMENTATION IN VLSI TECHNOLOGY

Vojin G. Oklobdzija and Earl R. Barnes

IBM T.J.Watson Research Center P.O.Box 218 Yorktown Heights, NY 10598

### **ABSTRACT**

An efficient scheme for carry propagation in an ALU implemented in n-MOS technology is presented. An algorithm that determines the optimum division of the carry chain of a parallel adder for various data path sizes is developed. This yields an implementation of a fast ALU which due to its regular structure occupies a modest amount of silicon. The speed of the implementation described is comparable to the carry look-ahead scheme. Our method is based on the optimization of the carry path implemented in n-MOS technology but the results can be applied to other technologies.

### 1. INTRODUCTION

An efficient implementation of an ALU in VLSI technology depends on many parameters. We consider an efficient implementation to be one which is fast, of a small and regular area, and low power. In many VLSI designs achieving the ultimate speed is not always important goal especially if this is achieved by consuming excessive area and power. Therefore Carry-Lookahead (CLA) scheme is not very attractive for VLSI implementations where area, regularity of structure and power are important. Also the determining factor, in case of an ALU, is wheather it is part of a critical path or not.

In this paper we considered Carry-Skip (CSA) scheme [1],[2],[3],[4] because it met our objective of reasonable performance achieved with a relatively small and regular area. This adder is in essence a Carry Lookahead for which the carrygenerate portion which consumes a large amount of logic, has been eliminated. As in a Carry Lookahead adder the bits to be added are divided into groups. A circuit is provided for detecting when a carry signal entering a group will ripple through the group.

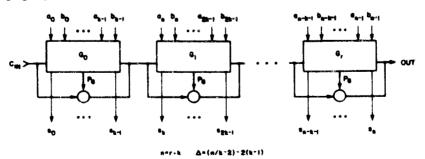

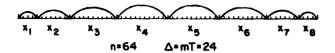

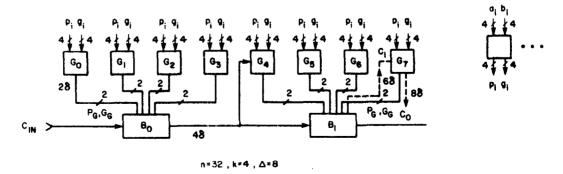

When this condition is detected, the carry is allowed to skip over the group. Carry-Skip Adder (CSA) does not require excessive amount of logic (area) and the "skip" portion of the logic can be added to the existing carry chain of Ripple-Carry Adder (RCA), therefore not disturbing the inherently regular bit-slice implementation of an RCA (Fig.1).

The power requirements of a CSA are considerably lower than that of a CLA-ALU. In this paper we show how the carry chain in a CSA can be optimized to yield better speed which in the case of a multi-level optimized CSA-ALU can even outperform the speed of a CLA divided into the groups of constant size

Lehman and Burla [3] studied a design of a CSA and suggested varying the size of the groups. By varying the sizes of the groups one can influence the maximum delay a carry signal can experience in propagating through the adder. Lehman and Burla [3] posed the problem of determining the optimal group sizes for minimizing the maximum delay [9]. They gave a heuristic method for obtaining economical group sizes. However, they did not solve the problem of determining optimal group sizes. For example, for a 48 bit adder they gave the group sizes 4 5 6 7 8 8 7 6 5 4 yielding the maximum delay of 14 [3]. We show that, under the same assumptions an optimal subdivision results in a delay of

They also discussed the problem of achieving even faster addition by allowing carry signals to skip over blocks of groups. The problem of optimizing the carry chain is now complicated by having to choose both the optimal number of blocks and the optimal sizes of groups within blocks. Some rules for choosing economical block and group sizes are given [3]. However, the problem of determining the optimal sizes remains unsolved.

In this paper we consider the problem of designing a carry-skip adder in FET technology and give some optimal solutions. Actually, our solutions are more general in that we generally assume

Fig.1 Carry-Skip Adder

that the time required for a carry signal to skip over a group of bits is longer than the time required for the carry to ripple through a single bit. This assumption is relevant for adders designed in n-MOS technology. Lehman and Burla assumed their adder to be designed using discrete components where these two times are equal. Our analysis will include their problem as a special case.

# 2. DIVIDING THE ADDER INTO GROUPS

Let n denote the number of bits in a carry skip adder and let m denote the number of groups into which the bits are divided. Let  $x_1, \ldots, x_m$  denote the sizes of the groups beginning with the most significant bit. Let T denote the time required for a carry signal to skip over a group of bits. To be precise we should write T = T(x) to indicate that T depends on the size x of the group over which the carry is skipped. However, T changes very slowly with x over the range of group sizes that concern us. So we assume that T is constant.

For a given n, the following three-step procedure gives an optimal way of dividing an n bit adder into groups of bits.

### Procedure 2:

2(i) Let m be the smallest positive integer such that

$$n \le m + \frac{1}{2}mT + \frac{1}{4}m^2T + (1 - (-1)^m)\frac{T}{8}.$$

(1)

2(ii) Let

$$y_i = \min\{1 + iT, 1 + (m+1-i)T\}, i = 1, ..., m$$

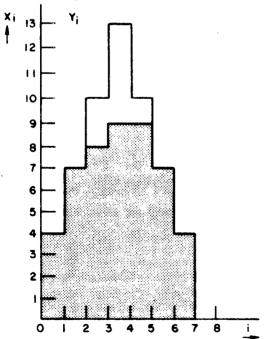

and construct a histogram whose i-th column has height  $y_i$ . For example, for T=3 and n=48, we have m=7 and the following histogram.

Fig. 2. Histogram of segments  $y_i$ ,  $x_i$

2(iii) It is easily verified that the area of the histogram in (ii) is

$$m + \frac{1}{2}mT + \frac{1}{4}m^2T + (1 - (-1)^m)\frac{T}{8} \ge n$$

so these are at least n unit squares in the histogram. Starting with the first row, shade in n of the squares, row by row. Let  $x_i$  denote the number of shaded squares in column i of the histogram,  $i = 1, \ldots, m$ .

Then  $x_1, \ldots, x_m$  is an optimal division of the adder. The maximum delay of a carry signal is mT.

Example 1. For a 48 bit adder we have, from Figure 2.  $x_1 = x_7 = 4$ ,  $x_2 = x_6 = 7$ ,  $x_3 = 8$  and  $x_4 = x_5 = 9$ .

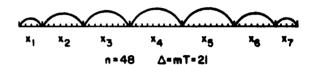

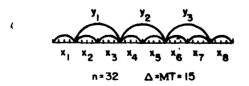

Fig.3. Carry chain of a 48-bit adder: n=48, mT=21

The maximum delay is experienced by a signal generated in the second bit position and terminating in the 47th bit position. The delay is mT = 21.

Example 2. Consider a 54 bit adder. From 2(i) we see that again m = 7. If we shade 54 squares in Figure 2, we see that

$$x_1 = x_7 = 4$$

,  $x_2 = x_6 = 7$ ,  $x_3 = x_5 = 10$  and  $x_4 = 12$

yields an optimal division of the adder. Again the maximum delay is mT = 21.

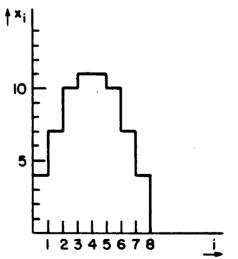

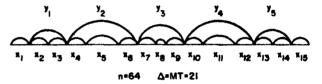

**Example 3.** Consider a 64 bit adder. From 2(i) we compute m = 8. The corresponding histogram is shown in Figure 4. The optimal group sizes are:

$$x_1 = x_8 = 4$$

,  $x_2 = x_7 = 7$ ,  $x_3 = x_6 = 10$ ,  $x_4 = x_5 = 11$ .

Fig.4. Segment histogram for a 64-bit adder: m=8

Fig.5. Carry chain of a 64-bit adder: m=8, mT=24

The delay of the longest signal is mT = 24.

Proof of Optimality We are going to prove optimality of the division of the carry chain described in 2(i)-(iii). First we need a lemma.

**Lemma 1.** When the bits of a carry skip adder are grouped according to the scheme (i)-(iii), the maximum propagation time of a carry signal is mT

**Proof.** The carry generated at the 2nd bit position and terminating at the (n-1) clearly has propagation time mT. We must show that any other signal has propagation time smaller than or equal to mI. Consider a signal originating in the ith group and terminating in the jth, i < j. Denote its propagation time by P. Clearly

$$P \le (x_i - 1) + (j - i - 1)T + (x_i - 1).$$

By construction,  $x_i \le \min\{1 + iT, 1 + (m+1-i)T\}$  for each is

$$P \le \min\{1 + iT, 1 + (m+1-i)T\}$$

+  $\min\{1 + jT, 1 + (m+1-j)T\} + (j-i-1)T - 2$

There are three cases to consider.

### 1. First assume

$$\min\{1+iT,\ 1+(m+1-i)T\}=1+iT$$

and

$$\min\{1+jT, \ 1+(m+1-j)T\}=1+jT.$$

In this case  $1 + jT \le 1 + (m + 1 - j)T \Rightarrow 2jT - T \le mT$ . It follows that

$$P \le 1 + iT + 1 + jT + (j - i - 1)T - 2$$

=  $2jT \cdot T \le mT$ .

### 2. Now assume that

$$\min\{1+iT, 1+(m+1-i)T\}=1+iT$$

and

$$\min\{1+jT,\ 1+(m+1-j)T\}=1+(m+1-j)T.$$

In this case we have

$$P \le 1 + iT + 1 + (m + 1 - j)T + (j - i - 1)T - 2 = mT$$

3. Finally, assume that

$$\min\{1+iT,\ 1+(m+1-i)T\}=1+(m+1-i)T$$

and

$$\min\{1+jT,\ 1+(m+1-j)T\}=1+(m+1-j)T.$$

It follows that

$$P \le 1 + (m+1-i)T + 1 + (m+1-j)T + (j-i-1)T - 2$$

=  $2mT - (2iT-T) \le 2mT - mT = mT$ .

This completes the proof of the lemma.

**Lemma 2.** Let  $\Delta$  denote the maximum delay of a carry signal in a n bit carry skip adder with group sizes chosen optimally. Then

$$(m-1)T \leq \Delta \leq mT$$

.

**Proof.** Since we have exhibited a division of the carry chain into groups in such a way that the maximum delay of a carry signal is mT we clearly have  $\Delta \leq mT$ .

Let  $x_1, x_2, \ldots, x_r$  denote the optimal group sizes corresponding to  $\Delta$ . For the moment assume that r = 2k is even. By considering carries originating in group i and terminating in group r - i + 1,  $i = 1, \ldots, k$ , we deduce the following system of inequalities.