Proceedings

IEEE

INTERNATIONAL

CONFERENCE ON

CIRCUITS AND

COMPUTERS

**ICCC 82**

COMPUTER SOCIETY PRESS

IEEE CATALOG NO. 82CH1813-5 LIBRARY OF CONGRESS 82-82292 IEEE COMFUTER SOCIETY ORDER NO. 429

5506711

Order from: IEEE Computer Society Fost Office Box 80452 Worldway Postal Center Los Angeles, CA 90080 IEEE Service Center 445 Hoes Lane Piscataway, NJ 08854

THE INSTITUTE OF ELECTRICAL AND ELECTRONICS ENGINEERS, INC.

5506711

#### Published by IEEE Computer Society Press 1109 Spring Street Silver Spring, MD 20910

The papers appearing in this book comprise the proceedings of the meeting mentioned on the cover and title page. They reflect the authors' opinions and are published as presented and without change, in the interests of timely dissemination. Their inclusion in this publication does not necessarily constitute endorsement by the editors, IEEE Computer Society Press, or the Institute of Electrical and Electronics Engineers, Inc.

Copyright and Reprint Permissions: Abstracting is permitted with credit to the source. Libraries are permitted to photocopy beyond the limits of U.S. copyright law for private use of patrons those articles in this volume that carry a code at the bottom of the first page, provided the per-copy fee indicated in the code is paid through the Copyright Clearance Center, 21 Congress Street, Salem, MA 01970. Instructors are permitted to photocopy isolated articles for noncommercial classroom use without fee. For other copying, reprint or republication permission, write to Director, Publishing Services, IEEE, 345 E. 47 St., New York, NY 10017. All rights reserved. Copyright © 1982 by The Institute of Electrical and Electronics Engineers, Inc.

IEEE Catalog No. 82CH1813-5 Library of Congress No. 82-82292 IEEE Computer Society Order No. 429

Order from: IEEE Computer Society

Post Office Box 80452 Worldway Postal Center Los Angeles, CA 90080 IEEE Service Center 445 Hoes Lane Piscataway, NJ 08854

The Institute of Electrical and Electronics Engineers, Inc.

# **Foreword**

On behalf of the Conference Committee we would like to extend a special welcome to the Second International Conference on Circuits and Computers—ICCC-82. The first conference, organized by Guy Rabbat and held at the Rye Town Hilton Inn in Port Chester, New York, was very successful. Several suggestions from that meeting have been incorporated into this year's conference.

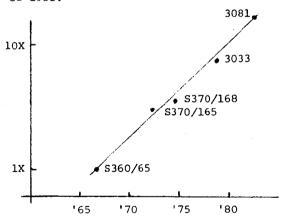

History has shown that the complexity of ICs has doubled every 1½ to 2 years. This increase in complexity to include very large scale integrated (VLSI) and very high-speed integrated (VHSI) circuits supported by improved fabrication techniques has emphasized the need for new circuit architectures and revolutionary design and testing methods. In addition, the availability of these complex ICs has presented new challenges to system designers to efficiently utilize the expanded signal processing capability.

ICCC-82 highlights topics associated with development and application of VLSI circuits to large-scale systems. While several workshops and conferences emphasize many different aspects of VLSI circuits, this conference is the only conference sponsored jointly by the IEEE Computer Society and Circuits and Systems Society and emphasizes three interdependent areas that characterize emerging VLSI technology: semiconductor technology, CAD design systems, and computing technology.

We would like to express our appreciation to the Technical Program Committee for the outstanding conference program. The response to the call for papers was overwhelming. The committee had a monumental task in reducing the approximately five hundred abstracts submitted for consideration by about two-thirds. Although many good papers could not be included, the 140 papers contained in the program are intended to describe some of the latest and most important accomplishments in the field. The international character of the conference is emphasized by the fact that one-third of the papers in the technical program are from overseas.

Special thanks are also extended to the Mid-Hudson and New York Sections of IEEE for publicity, local arrangements and assistance with the visual aids presentations.

C. W. Gwyn General Conference Chairman

J.J. Golembeski Technical Program Chairman

## **Conference Committee**

General Chairman

Charles W. Gwyn

Sandia National Laboratories

**Technical Program Chairman**

John Golembeski

Bell Laboratories

Local Arrangements

V.L. Gani

Chairman, Mid-Hudson IEEE

Section

IBM Corporation

Treasurer

Marvin E. Daniel

Sandia National Laboratories

Special Sessions

Guy Rabbat

IBM Corporation

**Publicity and Publications**

Merlin G. Smith

T.J. Watson Research Center

Secretary

Jack Goetz

Mid-Hudson Section

**Workshop Coordinator**

Bernie De Marinis

Booz Allen & Hamilton

# **Technical Committee**

**Technical Program Chairman**

John J. Golembeski Bell Laboratories

Kenneth R. Anderson

Siemens Corp. CRT

Frank Boesch

Stevens Institute of Technology

A.K. Bose

Bell Laboratories

Claude Davis

IBM Laboratories

Robert Dutton

Stanford University

Ivan Frisch

Network Analysis Corp

Ian Getreu

Textronix Inc.

Keural Goksel

Bell Laboratories

Shlomo Karni

University of New Mexico

R.H. Krambeck

Bell Laboratories

Saul Levy

Rutgers University

Paul Losleben

DARPA/IPTO

W.J. McCalla

Hewlett Packard Corp.

B.T. Murphy

**Bell Laboratories**

D.O. Pederson

University of California

Guy Rabbat

IBM Laboratories

Ronald Rohrer

G E Microelectronic Center

Daniel G. Schweikert

United Technologies

Charles P. Thacker

XEROX Corp.

Timothy Trick

University of Illinois

# **Table of Contents**

| Session  | on 1: IC Performance Limits and Trends (P. Losleben, Moderator)                                                                           |     |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

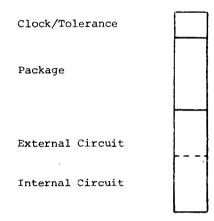

| 1.1      | The Key to High Performance Processors—Packaging                                                                                          | 2   |

| 1.2      | VLSI Approaching Cost-Performance Saturation                                                                                              | 6   |

| 1.3      | Application of GaAs Integrated Circuits for High Speed Computers                                                                          | 7   |

| Sessio   | on 2: Microprocessor Design Techniques I (S. Law, Moderator)                                                                              |     |

|          | An Externally Microprogrammable 32-Bit VLSI Processing System  R. Gunderson                                                               | 12  |

| 2.2      | Hierarchical Design Methodology for a Single Chip 32 Bit Microprocessor  D.E. Blahut, R.H. Krambeck, H.F.S. Law, H. Shichman, and H.C. So | 16  |

| 2.3      | A 370 Emulator Chip                                                                                                                       | 21  |

| Sessio   | on 3: Large Scale Multilevel Simulation and Analysis (A. Ruehli, Moderator)                                                               |     |

| 3.1      | Multilevel Simulation in VISTA: Architecture and Performance  R.I. Gardner, J.W. Grundmann, D.S. Pass, and K.C. Swanson                   | 26  |

| 3.2      | Electrical Consistency in Schematic Simulation                                                                                            | 30  |

| 3.3      | A Prediction-Relaxation-Based Simulator for MOS Circuits                                                                                  | 34  |

| 3.4 (    | Circuit Analysis, Logic Simulation and Symbolic Design for VLSI Synthesis                                                                 | 38  |

| 3.5 [    | LOGMOS: A Transistor Oriented Logic Simulator with Assignable Delays                                                                      | 42  |

| 3.6 I    | mplementation Issues in Multiple Delay Switch Level Simulation                                                                            | 46  |

| Sessio   | n 4: Topics in Computer Organization I (S. Levy, Moderator)                                                                               |     |

| 4.1 /    | A Dynamically Reconfigurable Computation Network for Flexible and High-Speed Signal Processing                                            | 52  |

| 4.2 A    | T. Ohkami, N.B. Iijima, T. Sakamoto, T. Hirai, A. Iwase, and C. Tanaka  A Data Flow Language and Interpreter for a Reconfigurable         |     |

|          | Distributed Data Processor                                                                                                                | 56  |

|          | mplementation of a Fully Reconfigurable Multimicroprocessor                                                                               | 60  |

|          | oward the Liveness Analysis of Data Flow Program Graphs                                                                                   | 63  |

|          | A Self-Routing Recirculating Shuffle-Exchange Network for Multiprocessors and Packet-Switching                                            | 67  |

|          | A. Shimor and S. Ruhman                                                                                                                   |     |

| 4.6 A    | A Bit Flow Processor Module for Distributed Computing Systems                                                                             | 71  |

|          | 1 5: Computer Communication Networks I (I. Frisch, Moderator)                                                                             |     |

|          | analytical Model of Dynamic Routing in Virtual Circuit acket-Switching Network                                                            | 76  |

| 5.2 B    | A. Gershi asic Transport Protocol Formalization by Means of Finite State Machines                                                         | 81  |

| <i>-</i> | S. Alfonzetti and S. Casale                                                                                                               |     |

|          | erminal-Pair Reliability Analysis of the Probabilistic Bridge Network y a New Recursive Approach                                          | 851 |

|          | C. Lisboa, P.M. Lin, and B.L. Leon                                                                                                        |     |

|                                                                        | The Use of Stochastic Control in Parallel Communication Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 89                                            |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 5.5                                                                    | A.D. Klappholz and A. Kershenbaum  Survivable Computer Communication Routing Using Decentralized Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 93                                            |

| 5.5                                                                    | K. Brayer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7.5                                           |

| 5.6                                                                    | The XPC—A VLSI Link-Level Controller for X.25 LAPB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 98                                            |

| Sess                                                                   | ion 6: Microprocessor Design Techniques II (S. Law, Moderator)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                               |

| 6.1                                                                    | 16b CPU Design by a Hierarchical Polycell Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 102                                           |

|                                                                        | ion 7: Timing Methodologies (R.H. Krambeck, Moderator)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                               |

|                                                                        | A Clocking Discipline for Two-Phase Digital Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 108                                           |

| 7.2                                                                    | Electrical Design of BELLMAC-32A Microprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 112                                           |

|                                                                        | ion 8: Topics in Computer Organization II (S. Levy, Moderator)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                               |

|                                                                        | Reconfigurable Parallel Pipelines for Fault Tolerance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 118                                           |

| 8.2                                                                    | General Purpose Reconfigurable Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 122                                           |

| Sess                                                                   | ion 9: Computer Communications Networks II (I. Frisch, Moderator)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                               |

| 9.1                                                                    | M-Graph Approach for Protocol Validation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 128                                           |

| 9.2                                                                    | A Statistical Mechanics of Distributed Computer Communication Mechanisms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 133                                           |

| Sess                                                                   | ion 10: Plenary Session                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                               |

|                                                                        | el Session 11: An Industry View of VLSI Directions (S. Teicher, D. Toombs, T.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                               |

|                                                                        | ngo, G.P. Parker, K. Kurokawa, K. Kataoka, P. Low, and G. Tooker: Panelists)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                               |

| Socci                                                                  | ion 12: High Speed Arithmetic (I.E. Getreu, Moderator)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                               |

|                                                                        | Relaxed Pinout Constraints Yield Improved Parallel Adders for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                               |

|                                                                        | Relaxed Fillout Collectionits field improved faranci Adders to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                               |

|                                                                        | VLSI-Based Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 142                                           |

|                                                                        | VLSI-Based Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 142<br>147                                    |

|                                                                        | VLSI-Based Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                               |

|                                                                        | VLSI-Based Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 147                                           |

| 12.3<br>Sessi                                                          | VLSI-Based Systems  A.C. Erdal and P.D. Fisher  On Fast Binary Addition in MOS Technologies  J. Vuillemin and L. Guibas  A 16-Bit CMOS/SOS Multiplier-Accumulator  J. Iwamura, K. Suganuma, S. Taguchi, M. Kimura, and K. Maeguchi  ion 13: PLA Generation (R. Newton, Moderator)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 147<br>151                                    |

| 12.3<br><b>Sessi</b><br>13.1                                           | VLSI-Based Systems  A.C. Erdal and P.D. Fisher  On Fast Binary Addition in MOS Technologies  J. Vuillemin and L. Guibas  A 16-Bit CMOS/SOS Multiplier-Accumulator  J. Iwamura, K. Suganuma, S. Taguchi, M. Kimura, and K. Maeguchi  ion 13: PLA Generation (R. Newton, Moderator)  A Fully Automatic, Technology-Independent PLA Macrocell Generator  M. W. Stebnisky, M.J. McGinnis, J.C. Werbickas, R.N. Putatunda, and A. Feller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 147<br>151<br>156                             |

| 12.3 <b>Sessi</b> 13.1                                                 | VLSI-Based Systems  A.C. Erdal and P.D. Fisher  On Fast Binary Addition in MOS Technologies  J. Vuillemin and L. Guibas  A 16-Bit CMOS/SOS Multiplier-Accumulator  J. Iwamura, K. Suganuma, S. Taguchi, M. Kimura, and K. Maeguchi  ion 13: PLA Generation (R. Newton, Moderator)  A Fully Automatic, Technology-Independent PLA Macrocell Generator  M.W. Stebnisky, M.J. McGinnis, J.C. Werbickas, R.N. Putatunda, and A. Feller  PLA Design for the BELLMAC-32A Microprocessor  HF.S. Law and M. Shoji                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 147<br>151<br>156<br>161                      |

| 12.3 <b>Sessi</b> 13.1                                                 | VLSI-Based Systems  A.C. Erdal and P.D. Fisher  On Fast Binary Addition in MOS Technologies  J. Vuillemin and L. Guibas  A 16-Bit CMOS/SOS Multiplier-Accumulator  J. Iwamura, K. Suganuma, S. Taguchi, M. Kimura, and K. Maeguchi  ion 13: PLA Generation (R. Newton, Moderator)  A Fully Automatic, Technology-Independent PLA Macrocell Generator  M.W. Stebnisky, M.J. McGinnis, J.C. Werbickas, R.N. Putatunda, and A. Feller  PLA Design for the BELLMAC-32A Microprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 147<br>151<br>156                             |

| 12.3<br>Sessi<br>13.1<br>13.2<br>13.3<br>Sessi                         | VLSI-Based Systems  A.C. Erdal and P.D. Fisher  On Fast Binary Addition in MOS Technologies  J. Vuillemin and L. Guibas  A 16-Bit CMOS/SOS Multiplier-Accumulator  J. Iwamura, K. Suganuma, S. Taguchi, M. Kimura, and K. Maeguchi  ion 13: PLA Generation (R. Newton, Moderator)  A Fully Automatic, Technology-Independent PLA Macrocell Generator  M.W. Stebnisky, M.J. McGinnis, J.C. Werbickas, R.N. Putatunda, and A. Feller  PLA Design for the BELLMAC-32A Microprocessor  HF.S. Law and M. Shoji  Some Theoretical Results on the Optimal PLA Folding Problem  M. Luby, U. Vazirani, V. Vazirani, and A. Sangiovanni-Vincentelli  ion 14: VLSI Circuit Analysis and Simulation (D. Agnew, Moderator)                                                                                                                                                                                                                                                                                                                 | 147<br>151<br>156<br>161<br>165               |

| 12.3<br>Sessi<br>13.1<br>13.2<br>13.3<br>Sessi<br>14.1                 | VLSI-Based Systems  A.C. Erdal and P.D. Fisher  On Fast Binary Addition in MOS Technologies  J. Vuillemin and L. Guibas  A 16-Bit CMOS/SOS Multiplier-Accumulator  J. Iwamura, K. Suganuma, S. Taguchi, M. Kimura, and K. Maeguchi  ion 13: PLA Generation (R. Newton, Moderator)  A Fully Automatic, Technology-Independent PLA Macrocell Generator  M. W. Stebnisky, M.J. McGinnis, J.C. Werbickas, R.N. Putatunda, and A. Feller  PLA Design for the BELLMAC-32A Microprocessor  HF.S. Law and M. Shoji  Some Theoretical Results on the Optimal PLA Folding Problem  M. Luby, U. Vazirani, V. Vazirani, and A. Sangiovanni-Vincentelli  ion 14: VLSI Circuit Analysis and Simulation (D. Agnew, Moderator)  Circuit Simulation on Vector Processors  A. Vladimirescu and D.O. Pederson                                                                                                                                                                                                                                    | 147<br>151<br>156<br>161                      |

| 12.3<br>Sessi<br>13.1<br>13.2<br>13.3<br>Sessi<br>14.1                 | VLSI-Based Systems  A.C. Erdal and P.D. Fisher  On Fast Binary Addition in MOS Technologies  J. Vuillemin and L. Guibas  A 16-Bit CMOS/SOS Multiplier-Accumulator  J. Iwamura, K. Suganuma, S. Taguchi, M. Kimura, and K. Maeguchi  ion 13: PLA Generation (R. Newton, Moderator)  A Fully Automatic, Technology-Independent PLA Macrocell Generator  M. W. Stebnisky, M.J. McGinnis, J.C. Werbickas, R.N. Putatunda, and A. Feller  PLA Design for the BELLMAC-32A Microprocessor  HF.S. Law and M. Shoji  Some Theoretical Results on the Optimal PLA Folding Problem  M. Luby, U. Vazirani, V. Vazirani, and A. Sangiovanni-Vincentelli  ion 14: VLSI Circuit Analysis and Simulation (D. Agnew, Moderator)  Circuit Simulation on Vector Processors  A. Vladimirescu and D.O. Pederson  CAMUS—A Mixed-Mode Network Analysis Program                                                                                                                                                                                       | 147<br>151<br>156<br>161<br>165               |

| 12.3<br>Sessi<br>13.1<br>13.2<br>13.3<br>Sessi<br>14.1<br>14.2         | VLSI-Based Systems  A.C. Erdal and P.D. Fisher  On Fast Binary Addition in MOS Technologies  J. Vuillemin and L. Guibas  A 16-Bit CMOS/SOS Multiplier-Accumulator  J. Iwamura, K. Suganuma, S. Taguchi, M. Kimura, and K. Maeguchi  ion 13: PLA Generation (R. Newton, Moderator)  A Fully Automatic, Technology-Independent PLA Macrocell Generator  M. W. Stebnisky, M.J. McGinnis, J.C. Werbickas, R.N. Putatunda, and A. Feller  PLA Design for the BELLMAC-32A Microprocessor  HF.S. Law and M. Shoji  Some Theoretical Results on the Optimal PLA Folding Problem  M. Luby, U. Vazirani, V. Vazirani, and A. Sangiovanni-Vincentelli  ion 14: VLSI Circuit Analysis and Simulation (D. Agnew, Moderator)  Circuit Simulation on Vector Processors  A. Vladimirescu and D.O. Pederson  CAMUS—A Mixed-Mode Network Analysis Program  G. Mancini and N. Rumin                                                                                                                                                              | 147<br>151<br>156<br>161<br>165               |

| 12.3<br>Sessi<br>13.1<br>13.2<br>13.3<br>Sessi<br>14.1<br>14.2         | VLSI-Based Systems  A.C. Erdal and P.D. Fisher  On Fast Binary Addition in MOS Technologies  J. Vuillemin and L. Guibas  A 16-Bit CMOS/SOS Multiplier-Accumulator  J. Iwamura, K. Suganuma, S. Taguchi, M. Kimura, and K. Maeguchi  ion 13: PLA Generation (R. Newton, Moderator)  A Fully Automatic, Technology-Independent PLA Macrocell Generator  M.W. Stebnisky, M.J. McGinnis, J.C. Werbickas, R.N. Putatunda, and A. Feller  PLA Design for the BELLMAC-32A Microprocessor  HF.S. Law and M. Shoji  Some Theoretical Results on the Optimal PLA Folding Problem  M. Luby, U. Vazirani, V. Vazirani, and A. Sangiovanni-Vincentelli  ion 14: VLSI Circuit Analysis and Simulation (D. Agnew, Moderator)  Circuit Simulation on Vector Processors  A. Vladimirescu and D.O. Pederson  CAMUS—A Mixed-Mode Network Analysis Program  G. Mancini and N. Rumin  Solution of Piecewise Linear Ordinary Differential Equations Using Waveform                                                                                  | 147<br>151<br>156<br>161<br>165<br>172        |

| 12.3<br>Sessi<br>13.1<br>13.2<br>13.3<br>Sessi<br>14.1<br>14.2<br>14.3 | VLSI-Based Systems  A.C. Erdal and P.D. Fisher  On Fast Binary Addition in MOS Technologies  J. Vuillemin and L. Guibas  A 16-Bit CMOS/SOS Multiplier-Accumulator  J. Iwamura, K. Suganuma, S. Taguchi, M. Kimura, and K. Maeguchi  ion 13: PLA Generation (R. Newton, Moderator)  A Fully Automatic, Technology-Independent PLA Macrocell Generator  M.W. Stebnisky, M.J. McGinnis, J.C. Werbickas, R.N. Putatunda, and A. Feller  PLA Design for the BELLMAC-32A Microprocessor  HF.S. Law and M. Shoji  Some Theoretical Results on the Optimal PLA Folding Problem  M. Luby, U. Vazirani, V. Vazirani, and A. Sangiovanni-Vincentelli  ion 14: VLSI Circuit Analysis and Simulation (D. Agnew, Moderator)  Circuit Simulation on Vector Processors  A. Vladimirescu and D.O. Pederson  CAMUS—A Mixed-Mode Network Analysis Program  G. Mancini and N. Rumin  Solution of Piecewise Linear Ordinary Differential Equations Using Waveform  Relaxation and Laplace Transforms  R.J. Kaye and A.L.M. Sangiovanni-Vincentelli | 147<br>151<br>156<br>161<br>165<br>172<br>176 |

| 12.3<br>Sessi<br>13.1<br>13.2<br>13.3<br>Sessi<br>14.1<br>14.2<br>14.3 | VLSI-Based Systems  A. C. Erdal and P.D. Fisher  On Fast Binary Addition in MOS Technologies  J. Vuillemin and L. Guibas  A 16-Bit CMOS/SOS Multiplier-Accumulator  J. Iwamura, K. Suganuma, S. Taguchi, M. Kimura, and K. Maeguchi  ion 13: PLA Generation (R. Newton, Moderator)  A Fully Automatic, Technology-Independent PLA Macrocell Generator  M. W. Stebnisky, M.J. McGinnis, J.C. Werbickas, R.N. Putatunda, and A. Feller  PLA Design for the BELLMAC-32A Microprocessor  HF.S. Law and M. Shoji  Some Theoretical Results on the Optimal PLA Folding Problem  M. Luby, U. Vazirani, V. Vazirani, and A. Sangiovanni-Vincentelli  ion 14: VLSI Circuit Analysis and Simulation (D. Agnew, Moderator)  Circuit Simulation on Vector Processors  A. Vladimirescu and D.O. Pederson  CAMUS—A Mixed-Mode Network Analysis Program  G. Mancini and N. Rumin  Solution of Piecewise Linear Ordinary Differential Equations Using Waveform  Relaxation and Laplace Transforms                                             | 147<br>151<br>156<br>161<br>165<br>172        |

| 14.6  | R. Putatunda                                                                  | 19.                                     |

|-------|-------------------------------------------------------------------------------|-----------------------------------------|

| Seco  | ion 15: Design for Testability (V.D. Agrawal, Moderator)                      |                                         |

|       | Testability Enhancement of VLS! Using Circuit Structures                      | 198                                     |

| 15.1  | V.G. Oklobdzija and M.D. Ercegovac                                            | • • • • • • • • • • • • • • • • • • • • |

| 15.2  | The Use of Rademacher-Walsh Spectrum in Testing and Design                    |                                         |

| 13.2  | of Digital Circuits                                                           | 202                                     |

|       | TC. Hsiao and S.C. Seth                                                       | 202                                     |

| 153   |                                                                               | 20.                                     |

| 15.3  | A Novel Approach to Fault-Tolerant Sequential Circuits                        | 206                                     |

|       | Y. Takefuji, Y. Adachi, and H. Aiso                                           |                                         |

| 15.4  | A Testable Regular Design                                                     | 210                                     |

|       | C.C. Timoc, J.M. Favennec, and C. Le Blanche                                  |                                         |

| 15.5  | Testing Feedback Bridging Faults Among Internal, Input and Output             |                                         |

|       | Lines by Two Patterns                                                         | 214                                     |

|       | S. Xu and S.Y.H. Su                                                           |                                         |

| Saca  | ion 16: Topics in Computer Organization III (C. Davis, Moderator)             |                                         |

|       | Mean Time to System Disappointment—Generalization of                          |                                         |

| 10.1  |                                                                               | 220                                     |

|       | Mean Time Between Failures                                                    | 220                                     |

|       | Y. Min, Y.K. Malaiya, and S.Y.H. Su                                           |                                         |

| 16.2  | New Design Methodologies and Circuits Needed for Parallel VLSI Supercomputers | 224                                     |

|       | R.B. Lee and A.L. Wiemann                                                     |                                         |

| 16.3  | An Array Architecture for Parallel FFT Processing                             | 232                                     |

|       | T.J. Chou                                                                     |                                         |

| 16.4  | Titanic: A VLSI Based Content Addressable Parallel Array Processor            | 236                                     |

|       | C. Weems, S. Levitan, and C. Foster                                           |                                         |

| 16.5  | Distributed Memory Management for Multiprocessor                              | 240                                     |

| 10.5  | F. Briggs and B.A. Parvin                                                     | 240                                     |

|       |                                                                               |                                         |

|       | ion 17: New Routing Techniques and Applications (J. Wisniewski, Moderator)    |                                         |

| 17.1  | On the Routability and Channel Routing Order of a General Cell Approach       | 246                                     |

|       | WT. Liu and D.E. Atkins                                                       |                                         |

| 17.2  | Bounds on Channel Width and a Routing Algorithm for a Classical               |                                         |

|       | Channel Configuration                                                         | 250                                     |

|       | M.S. Chandrasekhar and M.A. Breuer                                            |                                         |

| 17.3  | A New Area Router, The LRS Algorithm                                          | 256                                     |

|       | L.R. Smith, T. Saxe, J. Newkirk, and R. Mathews                               |                                         |

| 17 4  | A Channel Router Having Layer Assignment Capability for                       |                                         |

| 17.4  |                                                                               | 200                                     |

|       | Arbitrarily-Sized Rectangular Building Blocks                                 | 260                                     |

|       | M. Ishii, N. Harada, S. Ido, M. Koyama, and T. Inoue                          |                                         |

| 17.5  | Spatial Distribution of Wires in Master-Slice VLSI                            | 265                                     |

|       | M. Burstein, S.J. Hong, and R. Nair                                           |                                         |

| 17.6  | A Rerouting Scheme for Single-Layer Printed Wiring Boards                     | 270                                     |

|       | S. Futagami, I. Shirakawa, and H. Ozaki                                       |                                         |

| Sessi | on 18: Silicon Computers (C. Yu, Moderator)                                   |                                         |

|       | The Structure of a Silicon Compiler                                           | 272                                     |

| 10.1  | D.D. Gajski                                                                   | 212                                     |

| 10.3  |                                                                               | 077                                     |

| 18.2  | The Siclops Silicon Compiler                                                  | 277                                     |

|       | T.S. Hedges, K.H. Slater, G.W. Clow, and T. Whitney                           |                                         |

| 18,3  | SLAP—A Methodology for Silicon Layout                                         | 281                                     |

|       | S.P. Reiss and J.E. Savage                                                    |                                         |

| Sessi | on 19: Device Analysis and Processing Aids (R.W. Dutton, Moderator)           |                                         |

|       | An Analysis of MOSFETs' Narrow-Channel Effects                                | 286                                     |

|       | R. Dang, N. Shigyo, T. Wada, S. Onga, and M. Konaka                           | _00                                     |

| 10.2  | PRIDE—A Handheld Tool for IGFET Process and Device Design                     | 290                                     |

| 17,2  |                                                                               | 270                                     |

| 10.2  | J.R. Pfiester and J.D. Meindl                                                 | 204                                     |

| 17.5  | Automated Wafer Processing                                                    | 294                                     |

|       | I. Gililland and A. Liotenhero                                                |                                         |

| 19.4 FABRICS II: A Statistical Simulator of the IC Fabrication Process                                                    | 298         |

|---------------------------------------------------------------------------------------------------------------------------|-------------|

| Session 20: Topology Extraction and Reduction (F. Boesch, Moderator)                                                      |             |

| 20.1 Precise Device Recognition Technique for Bipolar IC/LSI                                                              | 304         |

| 20.2 LAS: Layout Pattern Analysis System With New Approach                                                                | 308         |

| Y. Okamura, Y. Muraishi, T. Sato, and Y. Ikemoto                                                                          |             |

| 20.3 PARADISE: A Circuit Diagram Generating System From LSI Mask Patterns                                                 | 312         |

| 20.4 PSL—Pattern Analyzer to Circuit Simulator Linker                                                                     | 316         |

| T. Watanabe, T. Sugawara, and K. Komuro                                                                                   | 510         |

| 20.5 A General Solution for Design Verification                                                                           | 320         |

| P.H. Munch and K.H. Munch                                                                                                 |             |

| 20.6 Logic Function Extraction for NMOS Circuits                                                                          | 324         |

| R.M. Apte, NS. Chang, and J.A. Abraham  20.7 A Logic Expression Generator for MOS Circuits                                | 328         |

| D. Saab and I. Hajj                                                                                                       | 320         |

| Session 21: Test Application I (J. Coleman, Moderator)                                                                    |             |

| 21.1 A System for Testing LSI Multi-Chip Modules Using Through-the-Pins Testing                                           | 334         |

| H.D. Schnurmann, R.M. Peters, and L.J. Vidunas                                                                            | 241         |

| 21.2 VLSI Testing, Diagnostics and Qualification                                                                          | 341         |

| 21.3 Testing for Delay Faults in a PLA                                                                                    | 346         |

| K. Son and D.K. Pradhan                                                                                                   |             |

| Session 22: Digital Signal Processing Applications I (W.K. Jenkins, Moderator)                                            |             |

| 22.1 Advanced Radar Signal Processing—A Challenge for VLS1                                                                | 352         |

| R. Klemm                                                                                                                  |             |

| 22.2 A Single Chip Digital Signal Processor                                                                               | 356         |

| M. Cand, P. Le Scan, and A. Roset  22.3 A Building Block for Digital Signal Processing: The Digital Operational Amplifier | 360         |

| T. Thong and R. G. Sparkes                                                                                                |             |

| 22.4 High Speed Signal Processing Functional Unit                                                                         | 363         |

| B. Hiatt, H. Bussey, and H. Spaanenburg                                                                                   |             |

| Session 23: Computational Algorithms (A. Mukhopadhyay, Moderator)                                                         |             |

| 23.1 A VLSI Device for Fast Exponentiation in Finite Fields                                                               | 368         |

| B. Fam and J. Kowalchuk  23.2 VLSI Algorithms for Doolittle's, Crout's and Cholesky's Methods                             | 372         |

| L. Johnsson                                                                                                               | 312         |

| 23.3 Decoupled Solution of Circuit Matrices on Pipelined Processors                                                       | 377         |

| D.A. Calahan                                                                                                              |             |

| 23.4 A Processor Array for Factorization of Unstructured Sparse Matrices                                                  | 380         |

| 23.5 Hardware Algorithms for a Class of Problems Defined by Recurrence Relations                                          | 384         |

| S. Wakabayashi, T. Kikuno, and N. Yoshida  23.6 A DC Iteration Algorithm for Difficult-to-Converge VLSI Circuits          | 388         |

| P. Yang                                                                                                                   | .,00        |

| Session 24: Physical Design (D.G. Schweikert, Moderator)                                                                  |             |

| 24.1 Structured Wiring Organization in Automatic VLS1 Layout Design                                                       | 394         |

| 24.2 Optimal Layer Assignment for Interconnect                                                                            | 398         |

| R. Y. Pinter  24.3 The Complexity of Two-Dimensional Compaction of VLSI Layouts                                           | 402         |

| S. Sastry and A. Parker                                                                                                   | TU2         |

| 24.4 Graph Search With a Systolic Multiqueue                                                                              | <b>4</b> 07 |

| ·                                                                                                                         |             |

| 24.:  | 5 Employing a Distributed Array Processor in a Dedicated                      |             |

|-------|-------------------------------------------------------------------------------|-------------|

|       | Gate Array Layout System                                                      | 411         |

|       | H.G. Adshead                                                                  |             |

| 24.6  | 6 Automatic Placement and Routing Program for Logic VLSI Design Based on      |             |

|       | Hierarchical Layout Method                                                    | 415         |

|       | H. Terai, M. Hayase, T. Ishii, C. Miura, T. Kozawa, K. Kishida, and Y. Nagao  |             |

| 24.   | 7 A Hierarchical Layout Description for Artwork Analysis of VLSI IC           | 419         |

|       | M. Marek-Sadowska and W. Maly                                                 |             |

| Par   | nel Session 25: The University Role in VLSI Research and Education            |             |

|       | A.J. Steckl, Moderator; N. Masnari, J.A.G. Jess, F. Branin, R. Shuey,         |             |

|       | . Sumney, and D.O. Pederson: Panelists)                                       |             |

|       | sion 26: Timing Analysis and Logic Simulation (S. Karni, Moderator)           |             |

|       | Path Delay Computation for Integrated Systems                                 | 426         |

| 20.   | H.K. Al-Hussein and R. W. Dutton                                              | 420         |

| 26.1  | 2 Modeling of MOS Transistors in a Logic Simulator                            | 421         |

| 20.2  |                                                                               | 431         |

| 26.5  | G.D. Jordan and R.M. Apte                                                     | 435         |

| 20    | 3 User Interface for an Interactive MOS Simulator                             | 435         |

| 26    | R. Willoner                                                                   | 420         |

| 20.4  | Accurate Multiple Delay Calculations for MOS Circuits                         | 439         |

| 26.6  | V.B. Rao and T.N. Trick                                                       | 443         |

| 20    | 5 Design Verification of Large Scale LSI Computers                            | 443         |

| 26.6  | Y. Ohno, M. Miyoshi, Y. Kazama, O. Tada, and T. Sakai                         | 4.45        |

| 20.0  | S Electronic Rule Checking for Structured VLSI Physical Design                | 447         |

|       | T. Akino, T. Kajita, A. Tanaka, H. Miyamoto, and Y. Mitsuyasu                 |             |

| Sess  | ion 27: Test Generation and Testability Analysis (M.C. Graf, Moderator)       |             |

|       | Automatic Test Generation for VLSI                                            | 452         |

|       | P.J. Miller and G.E. Taylor                                                   |             |

| 27.2  | A Class of Test Generators for Built-in-Testing                               | 456         |

|       | E.M. Aboulhamid and E. Cerny                                                  | -, -        |

| 27.3  | An Information Flow Approach to Functional Testability Measures               | 460         |

|       | H.S. Fung and J.Y.O. Fong                                                     |             |

| 27.4  | Automatic Test Generating Using a Matrix Model of Digital Systems             | 464         |

|       | C.F. Acken                                                                    |             |

| 27.5  | A Deductive Method for Non Classical Logic Fault Simulation                   | 468         |

|       | N. Giambiasi, M. Sigal, and J.C. Rault                                        |             |

| 27.6  | Fault Location in Combinational Logic Networks by Multistage                  |             |

|       | Binary Tree Classifier                                                        | 471         |

|       | S.R. Das, W.B. Jones, Z. Chen, A.K. Nath, and T.T. Lee                        |             |

| Sess  | ion 28: Digital Signal Processing and Applications II (T.N. Trick, Moderator) |             |

|       | A Digital Signal Processor for Real Time Adaptive Transform Coding of         |             |

|       | Audio Signals up to 20 kHz Bandwidth                                          | 474         |

|       | KH. Brandenburg, G.G. Langenbucher, H. Schramm, and D. Seitzer                | 7/4         |

| 28.2  | The Simulation Results and Hardware Implementation of a New                   |             |

|       | Time Domain Speech Scrambling Algorithm                                       | 478         |

|       | LS. Lee and YP. Hung                                                          | 470         |

| 28.3  | A High Speed CCD Interpolator Filter                                          | <b>18</b> 2 |

| _     | S. Law, G.C. Temes, T.M. Ngo, and A. Ibrahim                                  | 402         |

| Speni |                                                                               |             |

| 30 I  | ion 29: Digital Signal Processing Architecture.I (T. Thong, Moderator)        | 466         |

| ۷7. I | FIR Digital Filters for VLSI Implementation  Y. Neuvo and S.K. Mitra          | 488         |

| 29.2  |                                                                               | 406         |

| £7.L  | New Concepts for Digital Signal Processors  L. Gazsi                          | 492         |

| 20.3  | Stored-Product Techniques of Digital Signal Processing                        | 40.4        |

| J     | W. Steenaart, D. Dubois, O. Monkewich, and T. Tiahiadi                        | 494         |

|       | 77. SECCHAUL, D. DUDOS, O. MONKENICH, AND I. HANIAA                           |             |

|       | ion 30: Design Entry (J.A.G. Jess, Moderator)                                     |     |

|-------|-----------------------------------------------------------------------------------|-----|

| 30.1  | Aids for VLSI Design Entry and Partitioning                                       | 500 |

| 30.2  | Schematic Entry System With a Query Feature                                       | 503 |

| 30.3  | The Making of Scheme-81                                                           | 507 |

|       | ion 31: CAD Systems (J. Crawford, Moderator)                                      |     |

| 31.1  | Integrated Design Automation System for Custom and                                |     |

|       | Gate Array VLSI Design                                                            | 512 |

| 31.2  | An Integrated Custom VLSI Design System                                           | 516 |

|       | K. Sato, M. Kakinuma, T. Yahara, and SI. Murai                                    |     |

| 31.3  | Interactive Database Management for Integrated Circuit Design                     |     |

|       | on the UNIX Operating System                                                      | 520 |

|       | E. de Doncker, P. Dewilde, J. Fokkema, R. Sennema, and K.J. Singh                 |     |

| Sessi | ion 32: Interactive Design Aids (R. Rohrer, Moderator)                            |     |

|       | Hierarchical Analysis Tools in an Interactive Environment                         | 526 |

| 32.2  | VLSI Hierarchical Design Verification                                             | 530 |

|       | S.E. Bello, J.L. Hoffman, Jr., R.I. McMillan, and J.A. Ludwig                     |     |

| 32.3  | WISE—An Interactive Symbolic Editor with Connectivity Maintenance                 | 534 |

|       | D. Gibson, D. Pantle, and N. Pierman                                              |     |

| 32.4  | TESS: A Topological Evaluator Tool                                                | 539 |

|       | R. Reis                                                                           |     |

| 32.5  | A Modified Objective Function and a Fast Algorithm for Design Centering  D. Agnew | 543 |

| Sessi | on 33: Test Applications II (K. Anderson, Moderator)                              |     |

|       | Automatic Test Generation for Electron-Beam Testing of VLSI Circuits              | 548 |

| 33.2  | Internal Testing of an 8 Bit Single Chip CMOS/SOS Microcomputer                   |     |

|       | Using an Electron Beam Tester                                                     | 552 |

|       | H. Koike, K. Doi, J. Iwamura, K. Maeguchi, T. Sato, and H. Tango                  |     |

| 33.3  | Characterizing the LSI Yield Equation from the Chip Test Data                     | 556 |

|       | S.C. Seth and V.D. Agrawal                                                        |     |

|       | A Pattern Recognition Based Method for IC Failure Analysis                        | 560 |

| 33.5  | Fault Characterization of VLSI MOS Circuits                                       | 564 |

| Sessi | on 34: Digital Signal Processing Architecture II (S.K. Mitra, Moderator)          |     |

|       | Bit-Level Fixed-Flow Architectures for Signal Processing                          | 570 |

| 34.2  | A Parallel VLSI Architecture for a Digital Filter of Arbitrary Length Using       |     |

| - ··- | Fermat Number Transforms                                                          | 574 |

|       | T.K. Truong, I.S. Reed, CS. Yeh, and H.M. Shao                                    |     |

| 34.3  | Overflow Detection in Self-Checking Residue Number Digital Processors             | 579 |

|       | W.K. Jenkins                                                                      |     |

| 34.4  | A VLSI Binary Multiplier Using Residue Number Systems                             | 583 |

|       | F. Barsi and A. Di Cola                                                           |     |

| 34.5  | A Large-Scale Data-Flow Computer for Parallel Signal Processing                   | 590 |

|       | F.S. Wong and M.R. Ito                                                            |     |

| 34.6  | On the VLSI Implementation of a Data Flow Signal Processor                        | 594 |

|       | K. Kronlöf, I. Hartimo, and O. Simula                                             |     |

| Session 35: Hardware Description Language (A. Parker, Moderator)                      |    |

|---------------------------------------------------------------------------------------|----|

| 35.1 LOGAL+—A Hardware Description Language for Hierarchical Design                   |    |

| and Multilevel Simulation 6                                                           | 00 |

| G.M. Nurie                                                                            |    |

| 35:2 ELLA: A Hardware Description Language 6                                          | 04 |

| J.D. Morison, N.E. Peeling, and T.L. Thorp                                            |    |

| 35.3 Hardware Description System Development 6                                        | 08 |

| D. Ackley, J. Carnegie, and E.B. Hassler, Jr.                                         |    |

| 35.4 The Sandia Micro Artwork Generation for Integrated Circuits (SMAGIC) System      |    |

| and the Hierarchical Artwork (HAT) Language 6                                         | 12 |

| B.D. Richard                                                                          |    |