## DIGITAL ELECTRONIC CIRCUITS

Glenn M. Glasford

### DIGITAL ELECTRONIC CIRCUITS

### Glenn M. Glasford

Professor of Electrical and

Computer Engineering

Syracuse University

PRENTICE HALL, Englewood Cliffs. NJ 07632

Library of Congress Cataloging-in-Publication Data

GLASFORD, GLENN M.

Digital e'ectronic circuits.

Includes bibliographies and index.

1. Digital electronics. 1. Title.

TK7868.D5G58 1987

621.3815'3

ISBN 0-13-211954-4

87-12576

Editorial/production supervision and interior design: ELENA LE PLKA Cover design: 20/20 SERVICES, INC. Manufacturing buyer: GORDON OSBOURNE

© 1988 by Prentice Hali A Division of Simon & Schuster Englewood Cliffs, New Jersey 07632

All rights reserved. No part of this book may be reproduced, in any form or by any means, without permission in writing from the publisher.

Printed in the United States of America 10 9 8 7 6 5 4 3 2 1

ISBN 0-13-211954-4 025

Prentice-Hall International (UK) Limited, London Prentice-Hall of Australia Pty. Limited, Sydney Prentice-Hall Canada Inc., Toronto Prentice-Hall Hispanoamericana, S.A., Mexico Prentice-Hall of India Private Limited, New Delhi Prentice-Hall of Japan, Inc., Tokyo Simon & Schuster Asia Pte Lid., Singapore Editora Prentice-Hall do Brasil, Ltda., Rio de Janeiro

28944111

### **PREFACE**

The study of electronic circuits, which involves both discrete and integrated structures, is usually divided into two separate but related parts, analog circuits and digital circuits. A third part, encompassing nonlinear and switching operations, particularly analog-digital conversion processes, may be incorporated with either or both parts or may be treated separately, as indeed it should be for a comprehensive treatment. Unfortunately, it is often neglected entirely.

Analog circuits and digital circuits can be treated pedagogically in either order following an appropriate treatment of device theory and circuit modeling, which may be more or less common to both parts. This philosophy is carried out in this and in a companion volume, Analog Electronic Circuits. Each volume begins with three chapters devoted to the mathematical and electronic circuit modeling of semiconductor device characteristics, based upon the physical or structural parameters as derived from basic device physics. This lays the groundwork for determining important device parameters for discrete-device or integrated-circuit design. In this book the three introductory chapters parallel and partly duplicate similar material in the companion volume, but with a different emphasis. The material on incremented models is abridged, while the material on switching characteristics and switching speeds is expanded.

Inasmuch as the basic building block for digital systems is the logic gate, three chapters are devoted to the details of the structure of basic logic families: (1) those employing transistors which operate in a saturated mode, with examples being diode-transistor logic (DTL), transistor-transistor logic (TTL), and integrated injection logic (I<sup>2</sup>L), including high-speed and Schottky variations, (2) those employing transistors in a nonsaturating mode, such as emitter coupled logic (ECL) and various structures which can be derived from it, and (3) those involving field-effect transistors, both junction and insulated-gate types, including metal-semiconductor junctions. The three chapters dealing with the

anatomy of logic gates cover the basic design principles of both discrete and integrated structures, based upon the use of structural device parameters as related to semiconductor physics (discussed extensively in the first three chapters). The approach is to show the evolution of the more-or-less standard logic families from the simplest forms in order to illustrate successive steps in design leading to improved performance, and then to show the reverse process of simplification, leading to structures suitable for large-scale and very large scale integration.

Chapter 7 is devoted to analysis of variation of the basic AND, NAND, NOR, OR gates, such as the AOI gate, the exclusive-OR, and the half-adder, as well as the principles of intertacing of logic families which operate at different voltage levels.

Chapter 8 deals entirely with the evolution of all forms of bistable circuits, symmetrical and nonsymmetrical, including the principles of standard R-S, J-K, and master-slave flip-flops as well as Schmitt triggers and comparators, with application to counters, shift registers, sequence generators, and static and dynamic memories.

Chapters 9 and 10 relate digital to analog circuits. Chapter 9 is a brief introduction to important analog circuits such as the operational amplifier, sampling gates, analog switches, sampled data transmission, and signal quantization, while Chapter 10 is devoted to digital/analog and analog/digital conversion principles. These two chapters are somewhat analogous to the two concluding chapters of *Analog Electronic Circuits*, which offer a brief introduction to switching and digital circuits followed by a less extensive chapter on analog/digital and digital/analog conversion processes.

The first three chapters (devoted to device principles) and the last two (which relate digital and analog circuits) make each volume self-contained and allow digital and analog circuits to be studied in either order without any important gaps in required background knowledge.

This book is adaptable to both classroom instruction and self-study and reference use at various levels ranging from upper division under-graduate and graduate-level students in electrical and computer engineering to practicing engineers and scientists who need to improve their fundamental knowledge of the principles of discrete and integrated digital circuits.

The author is grateful to many colleagues throughout his professional career with whom the sharing of information and experiences has contributed to his knowledge and his point of view and thus contributed substantially although indirectly to this book. They are far too many to acknowledge individually. Thanks are also due to editors at Prentice Hall, particularly Tim Bozik, Engineering Editor, for his continued encouragement and cooperation and to Elena Le Pera, Production Editor, for her efforts and meticulous care taken in the many stages of production.

For the preparation of this book, particular thanks are due to Bertha Fancher for her skill in typing the final manuscript as well as a number of preliminary drafts.

This book would not have been possible without the advice and continuous encouragement of my wife. Ethel. I am eternally grateful for the inspiration she has been to me.

Glenn M. Glasford

### CONTENTS

|   | PREF       | ACE                                                                                                          | ΧI |

|---|------------|--------------------------------------------------------------------------------------------------------------|----|

| ! |            | TIC AND DYNAMIC PROPERTIES EMICONDUCTOR JUNCTIONS                                                            | 1  |

|   | 1.1        | Semiconductor Properties, 2                                                                                  |    |

|   | 1.2        | Semiconductor Junction Properties, 7                                                                         |    |

|   | 1.3        | Voltage—Current Relationships at Semiconductor Junctions, 13                                                 |    |

|   | 1.4        | Metal-Semiconductor Contacts, 20                                                                             |    |

|   | 1.5        | The PN Junction Diode, 21                                                                                    |    |

|   | 1.6        | PN Junction Diode Dynamics, 28                                                                               |    |

|   | 1.7        | Diode Switching Characteristics, 34                                                                          |    |

|   | 1.8        | Approximate Temperature Characteristics of PN  Junctions, 39                                                 |    |

|   |            | Problems, 42                                                                                                 |    |

|   |            | References, 46                                                                                               |    |

| 2 | BIPC       | DLAR JUNCTION TRANSISTORS                                                                                    | 47 |

|   | 2.1<br>2.2 | Structures, Terminology, and General Characteristics, 47 Basic Mathematical Model for the NPN Transistor, 49 |    |

|   |            |                                                                                                              |    |

3

### Contents

| 2.3  | The PNP Transistor, 54                                                      |     |

|------|-----------------------------------------------------------------------------|-----|

| 2.4  | The Common-Emitter Connection for Transistors, 55                           |     |

| 2.5  | Extraction of Ebers-Moll Parameters from Measurements, 61                   |     |

| 2.6  | Structural Parameters and Nonlinearities, 65                                |     |

| 2.7  | Effects of Temperature Variations on Transistor Parameters, 74              |     |

| 2.8  | Dynamic Transistor Models at Low Voltages, 76                               |     |

| 2.9  | Piecewise Sequential Model for Switching Operations 81                      |     |

| 2.10 | Incrementally Linear (Small-Signal) Circuit Models, 88                      |     |

| 2.11 | High-Frequency Circuit Models, 94                                           |     |

| 2.12 | The Variational Nature of Incremental Parameters, 97                        |     |

|      | Problems, 100                                                               |     |

|      | References, 106                                                             |     |

|      |                                                                             |     |

|      | CTION AND INSULATED GATE<br>D-EFFECT TRANSISTORS                            | 108 |

| 3.1  | Basic n-Channel Junction-Gate FET Structures, 108                           |     |

| 3.2  | Basic Equations for n-Channel JFET, 109                                     |     |

| 3.3  | Semi-Empirical Models for the Saturation Region, 114                        |     |

| 3.4  | The p-Channel Junction Field-Effect Transistor, 116                         |     |

| 3.5  | The Insulated-Gate Field-Effect Transistor, 117                             |     |

| 3.6  | Basic Equations for IGFET Operation in the Low-Voltage (Triode) Region, 119 |     |

| 3.7  | Approximate IGFET Models for the Saturation Region, 125                     |     |

| 3.8  | IGFET (MOSFET) Symbols, 127                                                 |     |

| 3.9  | Incremental (Small-Signal) Circuit Models, 128                              |     |

| 3.10 | Nonlinear Characteristics of FET Capacitances, 131                          |     |

| 3.11 | Gain-Bandwidth Product and Figure of Merit, 134                             |     |

| 3.12 | A Brief Look at FET Switching Speeds, 135                                   |     |

| 3.13 | Temperature Dependence of Field-Effect Transistors, 138                     |     |

|      | Problems, 138                                                               |     |

|      | References, 142                                                             |     |

5

Contents

| 4.1  | Diodes and Transisters as Switches, 145                                                                                              |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.2  | Simple Concept of Diode and Diode-Transistor Logic Gate, 148                                                                         |     |

| 4.3  | Diode-Transistor Logic Gate with Self-Bias, 149                                                                                      |     |

| 4.4  | Evolution of Standard Diode-Transistor Logic (DTL) Gates, 152                                                                        |     |

| 4.5  | Evolution of Transistor-Transistor Logic (TTL) from DTL, 159                                                                         |     |

| 4.6  | Origins of Design Parameters for Basic TTL, 163                                                                                      |     |

| 4.7  | Switching-Speed Limitations of Basic TTL Gates, 165                                                                                  |     |

| 4.8  | Improved Recovery Time Using Transistor as Load, 174                                                                                 |     |

| 4.9  | Further Improvement in Speed by Faster Removal of Base<br>Charge (Active Pull-Down), 179                                             |     |

| 4.10 | Typical High-Speed TTL Gates, 181                                                                                                    |     |

| 4.11 | Saturation Control in Transistors, 186                                                                                               |     |

| 4.12 | Schottky Diodes and Transistors in TTL and DTL, 187                                                                                  |     |

| 4.13 | TTL/DTL Modifications for Integrated Structures, 189                                                                                 |     |

| 4.14 | Direct-Coupled Transistor Legic (DCTL) and<br>Resistor-Transistor Legic (RTL), 192                                                   |     |

| 4.15 | " F '                                                                                                                                |     |

| 4.16 | Integrated Implementation of Current-Source DCTL (Integrated Injection Logic, <sup>12</sup> L; or Merged Transistor Logic, MTL), 198 |     |

| 4.17 | Alternative Shottky Transistor Logic Structures, 201                                                                                 |     |

|      | Problems, 203                                                                                                                        |     |

|      | References. 2!i                                                                                                                      |     |

|      |                                                                                                                                      |     |

| MON  | ISATURATING BIPOLAR TRANSISTOR LOGIC GATES                                                                                           | 213 |

| 5.1  | Direct-Coupled Emitter-Follower Logic, 213                                                                                           |     |

| 5.2  | Emitter-Follower-Common-Base Logic Gate: A Basic Form of Emitter-Coupled Logic, 219                                                  |     |

| 5.3  | Elements of Standard Emitter-Coupled Logic (ECL), 224                                                                                |     |

| 5.4  | Some Variations in ECL Gates and Performance, 227                                                                                    |     |

vii

| <b>riii</b> | Contents |

|-------------|----------|

|             |          |

|   | viii       |                                                                   | Contents |

|---|------------|-------------------------------------------------------------------|----------|

|   | 5.5<br>5.6 | Evolution of ECL for LSI and VLSI Systems, 230                    |          |

|   | 5.0        | Temperature Limitations and Compensation, 237 Problems, 244       |          |

|   |            | References, 251                                                   |          |

| 6 | LOG        | IC-GATE STRUCTURES USING FIELD-EFFECT TRANSISTORS                 | 252      |

|   | 6.1        | Characteristics of MOSFETs as Switches and Loads, 253             |          |

|   | 6.2        | NMOS Logic Gates, 258                                             |          |

|   | 6.3        | PMOS Logic Gates, 263                                             |          |

|   | 6.4        | Active Loads for MOS Switches, 265                                |          |

|   | 6.5        | Switching Speeds for MOS Gates, 266                               |          |

|   | 6.6        | Switching Inverters Using Complementary Structures, 272           |          |

|   | 6.7        | CMOS Logic Gates, 273                                             |          |

|   | 6.8        | Switching Speed of CMOS Gates, 276                                |          |

|   | 6.9        | Junction-Gate FETs (JFETs) for Logic Gates, 278                   |          |

|   | 6.10       | Forward-Bias (Enhancement) Mode Operation for JFETs, E-JFETs, 279 |          |

|   | 6.11       | I ogic-Gate Structures Using E-JFETs, 282                         |          |

|   | 6.12       | Depletion Mode JFETs for Logic Gates, 285                         |          |

|   |            | Problems, 289                                                     |          |

|   |            | References, 294                                                   |          |

| 7 |            | IC-GATE EXPANSIONS, EXTENSIONS, AND<br>RCONNECTIONS               | 295      |

|   | 7.1        | Modified Gate Structures and Expanded Functions, 295              |          |

|   | 7.2        | The Transmission Gate, 302                                        |          |

|   | 7.3        | Three-State (Tri-State) Logic Gates, 304                          |          |

|   | 7.4        | The Exclusive-OR Function and the Half-Adder, 306                 |          |

| • | 7.5        | Interfacing of Logic Families, 311                                |          |

|   |            | Problems, 317                                                     |          |

|   |            | References, 326                                                   |          |

| 8 | BIST       | ABLE CIRCUITS: THEORY, DESIGN, AND APPLICATIONS                   | 327      |

|   | 8.1        | Simple Bistable Circuits and Conditions for Bistability, 327      |          |

|   | 8.2        | Bistable Circuits Using Bipolar Junction Transistors, 332         |          |

|   |            | - ·                                                               |          |

### Contents

| 8.3 | Changing the | State of a | Bistable Circuit; | "Triggering," | 333 |

|-----|--------------|------------|-------------------|---------------|-----|

|-----|--------------|------------|-------------------|---------------|-----|

- 8.4 Unsymmetrical Bistable Circuits, 336

- 8,5 Emitter-Coupled Bistable Circuits with Increased Gain, 339

- 8.6 Flip-Flops Using Logic Gates: Evolution and Terminology, 343

- 8.7 Clocked R-S Flip-Flops, 347

- 8.8 J-K and Master-Slave Flip-Flops, 348

- 8.9 Type-D Flip-Flops as Time-Delay Circuits, Shift Registers, and Counters, 358

- 8.10 Toggle-Type Flip-Flops as Counters, Ripple Counter, 366

- 8.11 MOSFET Static and Dynamic Shift Registers, 374

- 8.12 Sequential Memories Using Shift Registers, 383

- 8.13 The Random-Access Memory, RAM (or Read/Write Memory), 384

- 8.14 Dynamic Ram (Read/Write) Cells, 390

- 8.15 The Read-Only Memory or ROM, 392

- 8.16 Comments on Semiconductor Memories, 395

Problems, 395

References, 410

### 9 ANALOG SIGNAL PROCESSING

- 9.1 Some Essential Characteristics of Operational Amplifiers, 412

- 9.2 Basic Anatomy of Operational Amplifiers, 416

- 9.3 Limiting, Clipping, and Clamping Circuits, 422

- 9.4 Transmission Gates, Analog Switches, and Elementary Applications, 427

- 9.5 Simple Bistable, Monostable, and Astable Circuits, 432

- 9.6 Voltage-Controlled Oscillators, 442

- 9.7 Periodic Voltage Waveform Generators, 447

- 9.8 Sawtooth Current Generators, 453

Problems, 459

References, 470

411

| 10    | AMAL | .OG-TO-DIGITAL AND DIGITAL-TO-ANALOG CONVERTERS,                        | 471 |

|-------|------|-------------------------------------------------------------------------|-----|

|       | 10.1 | Sampling Rate and Bandwidth Requirements, 472                           |     |

|       | 10.2 | Quantizing and Digitizing Analog Information, 476                       |     |

|       | 10.3 | Simple Implementation of A/D Converters Using Parallel Comparators, 480 |     |

|       | 10.4 | Counter Ramp A/D Converter, 483                                         |     |

|       | 10.5 | Digital-to-Analog Conversion Processes and Techniques, 488              |     |

|       | 10.6 | Analog/Digital Converters Using Digital/Analog Converters, 496          |     |

|       | 10.7 | High-Speed and High-Resolution D/A Converters, 497                      |     |

|       | 10.8 | General Comments on A/D and D/A Converter<br>Methods, 503               |     |

|       |      | Problems, 506                                                           |     |

|       |      | References, 512                                                         |     |

| Index |      |                                                                         | 513 |

# STATIC AND DYNAMIC PROPERTIES OF SEMICONDUCTOR JUNCTIONS

### INTRODUCTION

Most semiconductor devices that are important in solid state electronic circuits make use of the electrical properities of *junctions*—either of two semiconductor materials having different impurity concentrations or of a metal and a semiconductor. Therefore, as background for the analysis or synthesis of solid-state circuits, we need to understand quantitatively the properties of pure semiconductors and how such properties are modified by the introduction of specific types of impurities. A semiconductor modified by the addition of a particular type of impurity so that it conducts current primarily by the flow of excess electrons is referred to as an *n-type semiconductor*—while one which is modified so that it conducts by the movement of electron deficiencies, referred to as *holes*, which appears like the movement of positive charges, is referred to as a *perspec semiconductor*.

A properly processed pn junction that will conduct readily in one direction with one applied voltage polarity and almost not at all in the other direction with the opposite voltage polarity is referred to as a rectifying junction. The control of the movement of charge carriers (electrons or holes) across pn junctions is fundamental to the operation of most semiconductor devices.

The purpose of this chapter may be stated briefly as to itows. (1) to review basic properties of semiconductor materials as based on principles of solid-state physics, (2) to analyze thoroughly the essential properties of semiconductors, and (3) define analytically the characteristics of the semiconductor function diede, which is a pec-fic device making use of the rectifying function.

The properties of the pn junction and the junction diode are the basis or much more

complex devices involving two or more junctions in discrete and integrated circuits. Thus the chapter is an introduction to much of what follows in succeeding chapters, and the relationships/developed in it will be referred to extensively.

### 1.1 SEMICONDUCTOR PROPERTIES

A semiconductor is defined as a material which has an electrical conductivity somewhere between that of materials normally classfied as conductors (usually metals, such as aluminum and copper) and that of insulators (such as glass and various ceramics).

A metal conducts electric current primarily as a result of the movement of electrons in the conduction band that are freed from the outer shells of its atoms under the influence of an applied electric field. In a bar or rod the current density along its axis is given by

$$J = (nq)v \tag{1.1}$$

where *n* is the electron density (electrons/unit volume), *q* is the charge of an electron  $(1.602 \times 10^{-19} \text{ coulombs})$ , and *v* is the velocity of charge carriers, referred to as *drift velocity*. The (nq) product is the *charge density*. The drift velocity is proportional to the applied electric field intensity, being given by  $v_d = \mu_n \mathcal{E}$ , where  $\mu_n$  is defined as the electron mobility. Then the current density is

$$J = n\mu_n q \mathscr{E} = \sigma \mathscr{E} \tag{1.2}$$

where  $\sigma$  is defined as the conductivity.

In Eq. (1.2) if  $\mathscr{E}$  is in units of volts per meter (V/m), q is in coulombs, n is in electrons/m<sup>3</sup>, and  $\mu_n$  is in m<sup>2</sup>/volt-sec, the current density is in units of (coulombs/m<sup>2</sup>)(1/t) or amperes/m<sup>2</sup>.

The total current through a cross section of area A in  $m^2$  is I = JA amperes.

These relationships lead to Ohm's law:

$$I = \frac{V}{R} = \frac{\sigma A V}{L} \tag{1.3}$$

where L is the length of the conducting element and R is defined as its resistance in ohms given by  $R = L/\sigma A$ .

For a sheet of material of length L and area A = WT, where W is the width and T its thickness, the resistance can be expressed as

$$R = \frac{L}{W} \left( \frac{1}{\sigma T} \right)$$

The quantity  $1/\sigma T$  is referred to as the *sheet resistance*, which is the resistance of any size square sheet of the material and is designated by  $R_{\Box}$ , usually expressed in units of *Ohms per square*.

In a semiconductor, electron current is also given by Eq. (1.2). However, the mobility will be found to be a much smaller number. Typical semiconductors are ger-

manium and silicon, each having four valence electrons. Each valence electron in each atom is shared by one of its four adjacent atoms, and the structure of the material is represented conceptually as a tinker-toy-like array called a lattice of what are called covalent bonds, with the entire structure referred to as a crystal. At temperatures near absolute zero, all electrons remain tightly bound and the conductivity is near zero. As the temperature is increased, some of the covalent bonds are broken because of thermal energy supplied to the crystal, and electrons acquire sufficient energy to move from the valence band to the conducting band. Thus freed, they can move through the crystal, which accounts for a finite mobility. In addition, for each electron freed from an atom, there exists an electron deficiency called a hole, which gives the atom a net positive charge. An electron may move from an adjacent atom to fill the hole, and another hole is created by the departed electron. This movement of holes is equivalent to the movement of positive charges, which accounts for an additional component of current referred to as hole conduction. Hence the total current density at any point in a semiconductor is given by

$$J = \mu_n n q \mathscr{E} + \mu_p p q \mathscr{E} \tag{1.4}$$

where p is the hole density and  $\mu_p$  is defined as the mobility of holes, which is in general considerably smaller than the corresponding electron mobility. In a pure semiconductor there are an equal number of holes and electrons, each referred to as the *intrinsic-carrier* concentration,  $n = p = n_i$ , which is usually expressed as

$$n_i^2 = pn ag{1.5}$$

The intrinsic-carrier concentration is an increasing function of temperature in a complex manner, being proportional to  $T^{3/2}$ . It is often specified at a common reference temperature. For example, silicon at 300 K has an intrinsic-carrier concentration  $n_i \approx 1.45 \times 10^{10}/\text{cm}^3$ .

### Impurities in Semiconductors

The electrical properties of semiconductors are modified drastically by the introduction of atoms of other materials referred to as *impurities*, a process called *doping*. For example, adding only a very small percentage of material having more outer-shell electrons contributes additional electrons to increase the electrical conductivity. Usually pentavalent atoms such as arsenic or antimony are introduced into silicon or germanium, contributing one free electron for each atom introduced. Such atoms are called *donors*, and the electron density of such donors is symbolized as  $N_D$ . Usually  $N_D >> n_i$  and  $n \approx N_D$ . For example, silicon contains approximately  $5 \times 10^{22}$  atoms/cm<sup>3</sup> and hence, with  $n_i = 1.45 \times 10^{10}$ /cm<sup>3</sup>, contains approximately  $2.9 \times 10^{-13}$  free carriers per atom, while each impurity atom contributes one free carrier. The introduction of pentavalent atoms of  $N_D = 5 \times 10^{16}$  atoms/cm<sup>3</sup>, which is  $(5 \times 10^{16})/(5 \times 10^{22})$  or one impurity atom per  $10^6$  silicon atoms, yields  $N_D \approx 3.45 \times 10^6$   $n_i$ .

Adding trivalent atoms such as boron or indium creates electron difficiencies or holes into which electrons from the parent atoms are free to move, thus increasing

drastically the hole conduction. Such impurity atoms are called *acceptors*, and the acceptor density is  $N_A$ . Usually  $N_A >> n_i$ ; hence  $p \cong N_A$ .

A doped semiconductor in which the impurities are predominately acceptor atoms is called a *p-type semiconductor*, and one in which donor atoms predominate is called an *n-type semiconductor*.

From the energy-band theory based on Fermi-Dirac statistics, the laws of statistical mechanics, and the density-of-states function derived from quantum mechanics it can be shown that Eq. (1.5) is equally valid for doped semiconductors.

In the intrinisic semiconductor the holes and electrons are equal in number and the atoms are on the average electrically neutral. In a doped semiconductor electrical neutrality is still preserved in the aggregate, and, in general, assuming that the acceptors and donor are fully ionized (i.e., there is a negative charge on all acceptors and a positive charge on all donors), we can write

$$(N_A + n) = (N_D + p)$$

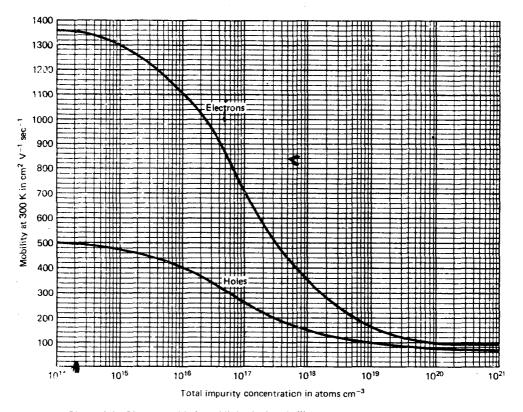

Figure 1.1 Electron and hole mobilities in doped silicon semiconductors at 300 K.

which, using

$$p = n_i^2/n$$

, can be written as

$$n = \frac{(N_D - N_A) + \sqrt{(N_D - N_A)^2 + 4n_i^2}}{2}$$

For an *n*-type semiconductor,  $N_D >> N_A$  and  $N_D >> n_i$ , so  $n \cong N_D$ . Then for an *n*-type semiconductor

$$p \cong \frac{n_i^2}{N_D} \tag{1.6}$$

Similarly for a p-type semiconductor

$$n \cong \frac{n_i^2}{N_A} \tag{1.7}$$

The conductivity of a semiconductor does not increase in direct proportion to the increase in free carriers as a result of doping, because carrier mobility is a decreasing function of impurity concentration. The reason is the random scattering of free electrons due to lattice vibrations, which result from energy imparted at elevated temperatures; this scattering impedes the motion of free carriers. The mobilities of holes and electrons at 300 K are shown in Figure 1.1 for silicon.

The impurity concentration in this figure is total impurity concentration  $N_D + N_A$ . However, usually only donors or acceptors are present, and the electron or hole mobilities are as shown for whichever impurities are present; i.e., the electron mobility is given for free electrons in either a p- or n-type semiconductor.

### Diffusion Current

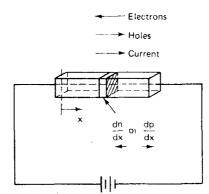

Drift current in a semiconductor due to an applied electric field, as given by Eq. (1.4), is not the only component of current if there is a gradient of free carriers dn/dx or dp/dxalong the axis of conduction, as indicated in Figure 1.2. The additional components ar

Figure 1.2 Charge-carrier flow in a emiconductor bar.

generated by the diffusion process and are referred to as diffusion currents. The total current densities along the axis are defined by the equations

$$J_{\rho_x} = q \mu_p p \mathcal{E}_x - q D_p \frac{dp}{dx} \tag{1.8}$$

$$J_{nx} = \underbrace{q\mu_{n}n\mathcal{E}_{x}}_{\text{drift}} + \underbrace{qD_{n}\frac{dn}{dx}}_{\text{diffusion}}$$

(1.9)

where  $D_n$  and  $D_p$  are called diffusion constants for electrons and holes, respectively, and  $\mathcal{E}_x$  is the component of electric field in the positive x direction.

Diffusion constants are related to mobilities by the Einstein relationship as derived from statistical mechanics, given by

$$\frac{D_n}{\mu_n} = \frac{D_p}{\mu_p} = \frac{kT}{q} \tag{1.10}$$

where T = temperature in Kelvins,  $q = 1.602 \times 10^{-19}$  coulombs, and k is Boltzmann's constant, given by  $1.38 \times 10^{-23}$  J/K. This equation permits Eqs. (1.8) and (1.9) to be expressed alternatively in terms of mobility or of diffusion constant alone.

The potential  $\phi$  at a distance x relative to x = 0 is defined by

$$\phi = -\int_0^x \mathscr{E}_x dx \tag{1.11}$$

or conversely

$$\mathscr{E}_{x} = -\frac{d\Phi}{dx} \tag{1.12}$$

An important equation used in the determination of voltage—current relationships in semiconductors is Gauss's law, which is expressed in one-dimensional form as

$$\frac{d\mathscr{C}}{dx} = \frac{\rho_x}{\varepsilon_o \varepsilon_r} \tag{1.13}$$

where  $\rho_x$  is the charge density at the point,  $\varepsilon_o$  is the permittivity of vacuum (8.854  $\times$  10<sup>-14</sup> F/cm), and  $\varepsilon_r$  is the relative dielectric constant for the particular semiconductor material (approximately 11.7 for silicon).

An alternative version, known as Peisson's equation, obtained from Eqs. (1.13) and (1.12) is

$$\frac{d^2\Phi}{dx^2} = \frac{-\rho_x}{\varepsilon_o \varepsilon_r} \tag{1.14}$$

Another important relationship is the continuity equation, which relates the time rate of change of charge carriers passing through an element area, as indicated in Figure