# 1957 IRE National Convention Record

### PART 3

Sessions Sponsored by IRE Professional Groups on

Broadcast and Television Receivers

**Electron Devices**

at

the IRE National Convention, New York, N. Y. March 18-21, 1957

249

The Institute of Radio Engineers

#### PART 3 - ELECTRON DEVICES: RECEIVERS

#### TABLE OF CONTENTS

|                                                                                                                                                                                                                                 | Page     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Session 8: Solid State Devices                                                                                                                                                                                                  | •        |

| (Sponsored by the Professional Group on Electron Devices)                                                                                                                                                                       | •        |

| A New High Frequency NPN Silicon Transistor A. B. Phillips and A. M. Intrator Noise Figures in Semiconductor Dielectric Amplifiers                                                                                              | 3        |

|                                                                                                                                                                                                                                 | 14       |

| H. C. Lin, and R. E. Crosby, Jr. An Alloy Type Medium Power Silicon Transistor H. G. Rudenberg and G. Franzen                                                                                                                   | 22<br>26 |

| A New Semiconductor Device                                                                                                                                                                                                      | 32       |

| A. Ramsa, F. Gordon, Jr., P. Newman, Jr., J. Handen and H. Jacobs                                                                                                                                                               | 40       |

| Session 16: Microwave Tubes                                                                                                                                                                                                     |          |

| (Sponsored by the Professional Group on Electron Devices)                                                                                                                                                                       |          |

| The Selection and Application of Traveling Wave Tubes A. H. Nielsen and N. W. Hansen                                                                                                                                            |          |

| X-Band Traveling Wave Tube Feedback Oscillator V. G. Price and C. T. Anderson A Light-Weight, Low Level Traveling Wave Tube for S-Band J. O. Bramick The Duplexer as a Means of Eliminating Interference from Nearby High-Power |          |

| Radar Systems                                                                                                                                                                                                                   | 71       |

| Linear Amplitude Modulation Systems                                                                                                                                                                                             | 82       |

| Behavior of a Backward Wave Oscillator with External Feedback F. L. Vernon                                                                                                                                                      | 91       |

|                                                                                                                                                                                                                                 |          |

| Session 33: Electron Tubes General (Sponsored by the Professional Group on Electron Devices)                                                                                                                                    |          |

| A Practical Design Theory for Minimization of Vibration Noise in Grid-Con-                                                                                                                                                      |          |

| trolled Vacuum Tubes                                                                                                                                                                                                            | 103      |

| Electrolytic Tank Measurements of Mesh Grid Characteristics                                                                                                                                                                     |          |

| Rare-Earth Oxide Cathodes L. J. Cronin, and J. H. Apelbaum                                                                                                                                                                      | 120      |

| Temperature Distribution in Anode Structure in Pulse mut                                                                                                                                                                        |          |

| A Positive Grid Voltage-Space Current Division Test the Bower Vacuum Tubes J. A. Jolly                                                                                                                                          | 129      |

| Electron Tubes for Critical Environments W. H. Kohl                                                                                                                                                                             | 141      |

| Section 99. Walandana I Gurdana D. A.                                                                                                                        | Page       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Session 23: Televisual Systems Devices (Sponsored by the Professional Groups on Electron Devices and Broadcast and Television Receivers)                     |            |

| The Development of 1100 Television Picture Tubes Having an Ion Trap Gun                                                                                      |            |

| Image Tube Utilizing Bombardment Induced Conductivity. R. W. Decker and R. J. Schneeberger New Developments in the Panel Light Amplifier (Abstract)          | 156<br>159 |

| Session 31: Transistor Applications (Sponsored by the Professional Group on Broadcast and Television Receivers)                                              |            |

| Circuit Considerations for High-Frequency Amplifiers Using Drift Transistors                                                                                 |            |

| Design Considerations in the First Stage of Transistor Receivers L. A. Freedman A Six-Transistor Portable Receiver Employing a Complementary Symmetry Output | 178<br>182 |

| Tetrajunction Transistor Receiver Circuits                                                                                                                   | 193        |

| Transistor Circuit Problems in TV Receiver Design                                                                                                            | 199        |

| E. M. Creamer, Jr., L. H. DeZube and J. P. McCallister                                                                                                       | 205        |

| Session 38: Color Television (Sponsored by the Professional Group on Broadcast and Television Receivers)                                                     |            |

| Developments in Color Television in Europe                                                                                                                   | 213        |

| Accuracy of Color Reproduction in the "Apple" System J. B. Chatten, and R. A. Gardner Recent Improvements in the Apple Beam-Indexing Color Tube              | 220<br>230 |

| An Advanced Color Television Receiver Using a Beam Indexing Picture Tube                                                                                     | 238        |

| R. A. Bloomsburgh, A. Hopengarten, R. C. Moore and H. H. Wilson, Jr.                                                                                         | 243        |

#### A NEW HIGH FREQUENCY NPN SILICON TRANSISTOR

by

A. B. Phillips and A. M. Intrator SEMICONDUCTOR PRODUCTS DEPARTMENT GENERAL ELECTRIC COMPANY Syracuse, New York

#### INTRODUCTION

In 1956, the Semiconductor Products Department of the General Electric Co., released for large-scale production the first of a new line of NPN silicon transistors.\* These transistors are designed for operation in either amplifier or switching circuit applications over an extended range of frequency and temperature. This newly-developed silicon transistor is made by a diffused-meltback process, developed by Dr. I. A. Lesk of the GE advanced Semiconductor Laboratory. This process offers a degree of uniformity and control in junction formation not seen by other known methods in use today. Furthermore, the process affords maximum economic utilization of costly single crystal silicon, since the base regions are formed directly in individually diced bars.

Using a combination of the principle of impurity segregation and solid-state diffusion, the diffused-meltback technique can produce base widths as thin as 2 microns with relative ease. The base layers are characterized with graded impurity distributions which enhances the frequency response by the drift-field effect. Alpha-cutoffs as high as 200 megacycles have been seen. Also, the collector region is characterized with a short high resistivity "Plateau" followed by a heavily-doped n-type region. This combination provides low output capacitances per unit area, high avalanche breakdown voltages, and virtually eliminates any "punch-thru"effects, without introducing high collector series resistances. One of the outstanding features of this silicon transistor is its low saturation resistance, which is nominally rated at 40 chms.

In the following sections of this paper, the electrical characteristics and a description of the diffused-meltback process and device fabrication are given. Also, the parameter variations with respect to frequency, bias, and temperature are presented.

#### TYPICAL ELECTRICAL CHARACTERISTICS

To properly describe the general performance characteristics of the silicon diffused-meltback transistor, designated as GE type LJDLA, it would be best to indicate the typical values of the more pertinent parameters for the production units. These are listed in Table I, grouped for both high-frequency and DC characteristics.

Under the high-frequency characteristics, the alpha-cutoff frequency distribution centers at 25 megacycles, with all units exceeding 15 megacycles. A good portion of the cut-off distribution is in excess of 50 megacycles. High-frequency power gain is measured in an unneutralized matched-input tuned-output circuit at a frequency of 5 megacycles. The typi il value is 13 decibels, measered at  $I_{\rm g}=-2$  ma. and  $V_{\rm G}=10$  volts. For those units having a betacutoff greater than 1 megacycles, the power gain is in excess of 15 db. The collector output capacitance,  $C_{\rm ob}$ , measured at 1 megacycle and  $V_{\rm G}=5$  volts, is typically 14 uuf. Lastly, the high-frequency reverse foltage feedback factor,  $h_{\rm rb}^{\prime}$ , is  $60 \times 10^{-3}$  at 1 megacycle.

For the DO characteristics, in Table I the typical common-emitter current gain is 30 measured at  $I_E$  = -2 ma. and  $V_C$  = 5 volts. This corresponds to an alpha of .968. All 4JD4A transistors are tested to assure a minimum current gain of 9, corresponding to an alpha of .9. Of utmost importance, particularly for switching applications, is the low series resistance of the collector for which 40 ohms is the typical value. This is measured in a forced-beta circuit, which puts the transistor well into saturation. reverse-biased collector current,  $I_{\rm CO}$ , measured at 5 volts, has a low nominal value of 10 millimicroamperes. Finally, all the breakdown voltages specified are limited by the avalanche effect and are measured at a current of 1 milliampere, which is well within the sharp breakdown region for silicon, Because of the unique impurity distribution of this transistor (to be described in a later section), the collectorjunction barrier spreading will extend much deeper into the collector, rather than into the base. This eliminates the occurrance of voltage "punch-thru", in spite of the extremely thin Emitter-to-base breakdown is nominally at 7 wolts and the distribution range is quite narrow. This relatively high voltage rating makes the transistor very suitable for switching applications, where it is required to turn off with large reverse voltages.

<sup>\*</sup>Developed under U.S. Air Force Contracts, Research and Development AF 33(600)17793 and Production Refinement AF 33(600)28956 issued out of AMC, Dayton, Ohio.

#### DIFFUSED-MELTBACK PROCESS

It has been rapidly recognized by the transistor industry, that the principle of solid-state diffusion of impurities offers the most promise of achieving uniformly the thin base regions necessary for very high frequency transistor performance. Because the diffusion cycle usually taked place over a period of several hours, the need for split-second accuracy is eliminated, thereby affording a high degree of process control. Moreover, by diffusing impurities which are already within the solid rather than on the surface, one gains another advantage in that the process is not affected by variations in surface properties and concentrations. It is for these reasons that the diffused-meltback process becomes so attractive as a means of making high-frequency NPN silicon transistors.

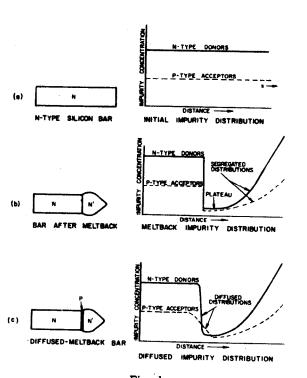

The process begins with the growth of a large single-crystal of silicon, which is intentionally doped with both n-type donor and p-type acceptor impurities. The doping concentrations are such that the crystal grows uniformly n-type of low resistivity, cor-responding to the emitter region of the final transistor. The crystal is then sawed into wafers and each wafer is then diced into bars approximately 1/8" long and .020" square. In (a) of Figure 1, the relative impurity concentrations within the bar of silicon are shown. At this step, the bar is everywhere homogenously n-type. One full-grown silicon crystal will yield thousands of these bars, each (after subsequent processing) corresponding to a unit transistor. The fact that almost all of the initial crystal is utilized, affords an economic advantage in that the silicon material costs are kept quite low.

The second step of the process is called "meltback", in which one end of the bar is remelted or melted-back, and then solidified again? This forms the tear-drop shape shown in (b) of Figure 1. Because the impurities are less soluble in the solid silicon than in the liquid, the impurities will segregate as the melted-portion freezes, forming the distributions shown in (b). Just at the liquid-solid interface, the initial impurity concentrations drops sharply to very low values determined by the concentrations and segregation coefficients of the initial impurities. In this region, the conductivity is still n-type, but the resistivity is much higher in the order of an ohm-cm or more. It should be noted that this high resistivity plateau extends only for a few thousandths of an inch, whereupon the resistivity drops quickly throughout the remainder of the meltback region. It should be emphasized that after melt-back, we have not as yet formed the base region, but simply a junction between two ntype regions of different resistivity.

The last step of the diffused-meltback process is when the base region is formed, thereby establishing the final npn transistor structure. This is accomplished by subjecting the melt-back bar to a long, high-temperature heating cycle, which lasts for many hours. Under the conditions, the impurities on the high concentration side of the meltback junction diffuse within the solid semiconductor into the "plateau" region of lower concentration. The final distribution of impurities after diffusion is shown in (c) of Figure 1, where the diffused distributions are given by the error-function relationship, viz.

$$C(z,t) = \frac{C_0}{2} \left[ 1 - \inf \left( \frac{z}{2\sqrt{Dt}} \right) \right] c_M^{-3}$$

(1)

In equation (1), C<sub>o</sub> is the net concentration difference of the respective impurities before diffusion, D is the diffusivity in cm<sup>2</sup>/sec for the impurity in silicon at the cycle temperature, and t is the diffusion cycle time in seconds. Thus, C(x, t)represents the final concentrations as a function of distance and time. The significant point to note here is that the p-type impurity has the property of diffusing almost 20 times faster than the n-type impurity in silicon. Therefore, on the "plateau" side of the junction, there results an excess of p-type impurities over the n-type, corresponding to a thin, p-type base region. By proper choice of the initial impurity concentrations and the time and temperature of the diffusion cycle, heavily-doped bases as thin as 2 microns are obtained with relative ease.

The final overall impurity distribution of the silicon diffused-meltback bar is shown in Figure 2, where the net impurity concentrations are plotted as a function of distance. The emitter region corresponds to the lowresistivity, undisturbed portion of the original silicon bar. Just at the emitter junction, the conductivity is slightly more n-type because of the depletion of the p-type impurities that diffused from the region. The junction from emitter-to-base is quite abrupt, since the diffusion of the n-type impurities is relatively negligible. This abrupt junction makes for good injection efficiency into the base. Because of the predominant diffusion of the p-type acceptors, the base layer is character-ized by a graded impurity distribution approximating an error function. This introduces a "built-in" drift field which decreases the minority-carrier transit time, thereby increasing alpha-cutoff? If we assume a minumum increase of at least a factor of two, then the theoretical alpha-cutoff is given by

$$\omega_{co} = 2\left(\frac{2.43D_{\rm nc}}{N^2}\right) \tag{2}$$

where D $_{\rm n}$  is the diffusion constant for electrons, and W is the base width. Letting D $_{\rm n}$  = 20 cm²/sec for p-type silicon and W = 2.5 microns, equation (2) yields an alpha-cutoff frequency equal to 248 megacycles. The effects of emitter and collector capacitances and base resistance, however, limit the measured frequency cutoffs to lower values.

Also, in reference to Figure 2, the effect of the higher resistivity "plateau" in the collector region adjacent to the base is to cause the collector space-charge barrier to spread more into the collector than into the base. As a result, it is a good assumption that both the collector barrier capacitance and breakdown voltage are determined primarily by the collector resistivity. Although the latter is in the order of an ohm-cm. or so, the overall series collector resistance is kept low because of the rapid decrease of resistivity beyond the "plateau".

#### DEVICE FABRICATION

After the diffusion cycle the silicon npm bars are usually covered with a p-type "skin" due to the diffusion of the p-type acceptors to the surface. This is removed easily by chemical etching (CP4), which also prepares the bar for lead attachment. Ohmic emitter and collector contacts are made to the bar by alloying donordoped gold at each end, backed up by metal ribbon for rigid mechanical support of the bar. The end lead configuration is clearly shown in the photograph of Figure 3, which is a view of the completed transistor before capping. The base connection consists of a thin, aluminum ribbon which is alloyed directly on the p-region. The aluminum, being an acceptor impurity, makes a p-type contact and therefore does not short out the transistor. Ribbon is used to provide a line contact for reduced base resistance, and great care is applied to minimize overlap on either side of the base. Figure 4 shows a photo-micrograph of a cross-sectioned silicon bar showing also the base connection. Note, in particular, the thick regrowth layer which represents recrystallized silicon, heavily doped with aluminum.

The 4JD4A silicon transistor is packaged in the new, round header shown in the photograph of Figure 3. This header has been designed in accordance with JATEC standards for case dimensions for automatic insertion into printed-board assemblies. The unit is completed with the welding of a steel cap to the header to assure a perfect hermetic seal. The final assembly is painted to withstand 200°C storage temperatures and a 96 hour salt-spray test.

#### HIGH FREQUENCY CHARACTERISTICS

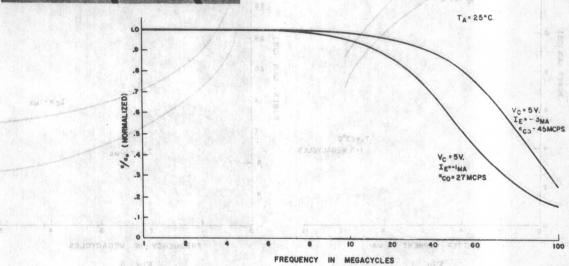

Two parameters with which the applications engineer are intimately concerned are the common base and common emitter current gains, h<sub>fb</sub> and h<sub>fe</sub> respectively. The frequency dependence of alpha is shown in Figure 5. The alpha variation is seen to be markedly dependent upon emitter bias. The greater fall off of alpha with frequency at the lower levels may be attributed to a reduction in the high frequency emitter efficiency due to the emitter junction capacitance. If the emitter efficiency at low frequencies is close to unity then it can be shown that the high frequency emitter efficiency is inversely related to the product of the emitter junction capacitance and AC emitter resistance, kT/qIg. Since the emitter resistance is also inversely proportional to emitter current, it would be expected that this degradation in emitter efficiency would be less pronounced as the current level is increased. However, as the current level is increased further the modulation of base resistivity significantly influences the emitter efficiency reducing it once more. The observed variation of alpha with frequency and emitter current behaves in the manner suggested by the above argument. This explains the behavior of the alpha cutoff frequency variation with emitter current which increases rapidly with current reaching a maximum in the range of from two to four milliamperes and then slowly falling off.

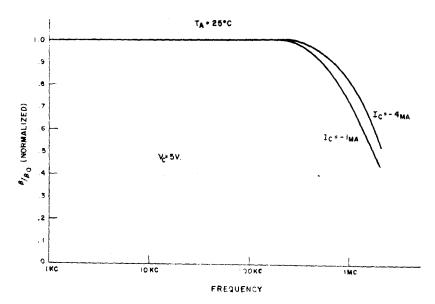

A typical variation of common emitter current gain, "beta", with frequency for different collector currents is shown in Figure 6. At increased bias currents the fall off of beta with frequency becomes less pronounced. This is understandable when one considers that the beta cut-off frequency is roughly proportional to the alpha cut off frequency divided by the de beta. As we have shown, fab increases with emitter current reaching a maximum in the neighborhood of 3 ma and then decreases fairly slowly as the collector current is increased further. Beta on the other hand decreases more rapidly with collector current above 3 ma. Consequently the frequency variation of beta becomes less pronounced with higher collector current.

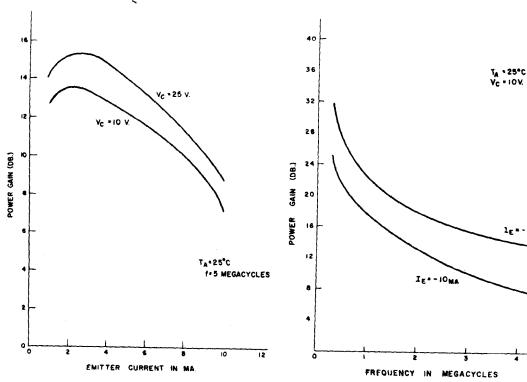

The behavior of common emitter power gain for both bias and frequency are shown in Figures 7 and 8. Figure 7 shows the dependence of power gain with emitter current. These are measurements made at 5 mc and at a collector voltage of 10 volts. The power gain peaks in a range of from 2 ma to 3 ma. As indicated earlier, the alpha cut off frequency maximized in the same range. It is known that the base spreading resistance, rb, decreases with emitter current as a result of the base crowding effect which takes place with increasing emitter current. Since the emitter resistance also

decreases with emitter current, both effects tend to increase power gain. However, the reduction in emitter efficiency at higher currents will appreciable affect the power gain and most likely accounts for the power gain reduction observed above 3 ma.

Figure 8 shows the variation of power gain with frequency. As indicated by the measurements above 1 mc. the common emitter power gain varied with frequency at a rate of about 4 db per octave. This is in good agreement with the theoretical behavior of common emitter power gain with frequency which was shown by R. L. Pritchard to be, for a grown junction transistor<sup>5</sup>

$$G_e = \frac{.2\omega_c^{\frac{1}{2}}}{\omega^{\frac{1}{2}h}C_c(\frac{h_c^{i}h_e}{h_e})^{\frac{1}{2}h}} \quad \text{and} \quad \frac{[h_c^{i}\omega]}{[h_c^{i}\omega]^{\frac{1}{2}}} > 1$$

Where w<sub>c</sub> = radian alpha cut off frequency

rb = base spreading resistance

r<sub>e</sub> = emitter resistance C<sub>ob</sub> = collector-base barrier capacitance

and corresponds to a 4.5 db variation per octave. The above expression also points out the important dependence of power gain with rg. The collector capacity, Cob, and the high frequency reverse voltage transfer ratio, hand provide an index of the frequency capabilities of the device. Measurements of has with frequency have shown it to be fairly linear with frequency in the one megacycle range. As a result of this linear behavior, it can be said to be proportional to the product of the base spreading resistance, rb, and collector capacity, Cob, and may be approximated by the expression

Substituting the typical values of 0.06 for hand 14 unf for Cob into the equation, ro is calculated to be in the order of 630 ohms. This value may be somewhat higher than desirable for optimum amplifier performance in that it can limit the power gain to be expected from the transistor. However, this is not an inherent limitation of the device for rocan be lowered by one of a number of techniques including heavier doping of the base region, or the widening of the base region.

In examining the distribution of parameters, the common emitter or beta cut-off frequency was found to center at approximately 700 kc. If the units are divided into two groups on the basis of their beta cut-off frequency, those with a tag greater than one megacycle and those equal to or less than one megacycle, then these sub-populations have two distinctly different centers

of distribution of power gain. The lower beta cut-off units have a power gain distribution centering about 12.5 db where-as the power gain of the higher beta cut off units centers about 16 db.

#### SMALL SIGNAL PARAMETERS -LOW FREQUENCY BEHAVIOR

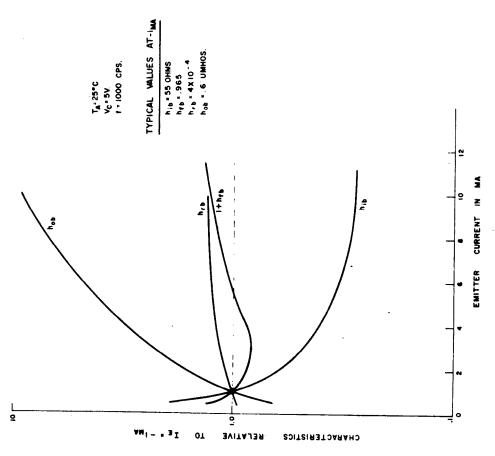

Typical values for the small-signal hybrid parameters are listed in Table II below. These include values for both the common emitter and common base configuration and represent data obtained from more than 1000 transistors. The measurements were made at one kilocycle.

#### TABLE II

| Parameter                                            |                                                                | Bias                                                                                                                                                                                                                                                                                                                  | Value                                                                                                        |

|------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| hib<br>hfb<br>hrb<br>hob<br>hrb<br>hie<br>hfe<br>hre | VCB=5V,<br>VCB=5V,<br>VCB=5V,<br>VCB=5V,<br>VCB=5V,<br>VCB=5V, | $I_{E^{w}} - 1$ ma, $f = 1$ KC $I_{E^{w}} - 2$ ma, $f = 1$ KC | 955<br>4 x 10 <sup>-4</sup><br>5 0.6 u mho<br>6 X 10 <sup>-2</sup><br>640 ohms<br>30<br>6 X 10 <sup>-4</sup> |

The variation of the common base hybrid parameters with emitter current is shown in Figure 9 in which the data was plotted relative to the value at an emitter current of 1 ma.

#### DC CHARACTERISTICS

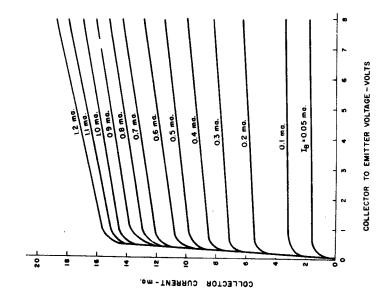

An important set of characteristics for any transistor are the collector characteristics shown by figure 10. This is a plot of the collector current with collector voltage for different levels of base current.

One of the very useful pieces of information which can be obtained from these characteristics is the series saturation resistance. This resistance, designated by the symbol  $R_{\rm SC}$ , is a measure of the collector to emitter voltage necessary to sustain a given collector current for some predetermined base current. R<sub>SC</sub> is generally defined as the slope of a line from the origin to a given intercept on the saturation region of the  $V_{0}-I_{0}$  characteristics. On many devices, particularly germanium and alloy transistors, the saturation region is fairly linear and does intercept the origin, thus providing a measure of saturation resistance which is consistent and coincides identically with the previously mentioned definition. However, this is not true for the AJDAA nor for many other silicon grown junction devices. The curves do not generally intercept the origin and are not guite as linear in the saturation region. Consequently, Rsc will vary with the point of operation and must be specified for a given collector and base current. Although the error may be small, a more consistent description would

be to restrict the definition of R without ambiguity and would be useful to the circuit designer interested in ac operation. The necessary additional information could then be given in terms of the more truly descriptive term, the collector saturation voltage,  $V_{\rm CE}$  (SAT) identified with a given collector and base current. Referring to Figure 10 the series saturation resistance on the basis of the above definition would be the slope of the envelope of the characteristic in saturation region. A typical value of saturation voltage,  $V_{\rm CE}$  (SAT), for the 4JD4A is 200 millivolts, measured at  $I_{\rm B}=1$  mm  $I_{\rm C}=5$  mm, which is equivalent to a saturation resistance of 40 ohms.

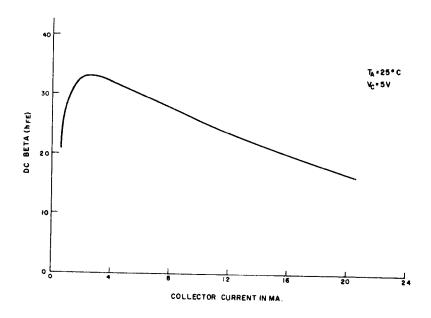

The crowding of the collector characteristics with base drive represen's the beta hold-up with collector current for the transistor. Figure 11 shows a typical variation of dc beta with current. Here we see that beta rises rapidly with current maximizing in the range of 1 to 3 ma collector current and then falls off at higher current levels. This degradation of beta hold-up at the higher values of collector current is due to a combination of factors, a reduction in emitter efficiency, base crowding effect, and poor injection efficiency at the base lead contact. Although this type of characteristic is representative of the device as it is now being produced a number of 4JD4A transistors were found with beta hold-up characteristics that was essentially flat for collector currents ranging from one to forty milliamperes.

#### TEMPERATURE DEPENDENCE

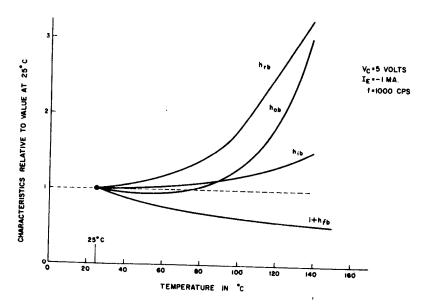

Figure 12 shows the variation of the common base "h" parameters with temperature. These curves which represents typical behavior of the AJD4A are normalized with reference to the values at room temperature, 25°C. It is seen that for the most part these parameters do not markedly deviate from their room temperature values below about 130°C. Above this temperature, however, a rather sharp rate of change is observed in all but hip.

The variation of breakdown voltage with temperature is interesting. Theoretically the junction breakdown voltage should increase with temperature in accordance with McKay's expression

$$BV_{T_i} = BV_{T_i} \left[ 1 + B \left( T_i - T_0 \right) \right] \tag{5}$$

where B is a constant of the order of 10-4 volts /OC, the exact value being a function of the junction grade. Measurements of the base to emitter breakdown, BVgBO, and collector to base breakdown, BVCBO, show an increase in breakdown voltage with temperature in accordance with this predicted variation. However, the collector to emitter breakdown voltage, BVCBO, although exhibiting this increase below 1000C decreases

fairly rapidly with temperature above 120°C. This can be explained when one considers the technique generally used to determine junction breakdown voltage which in essence involves measuring the voltage developed across the transistor junction under study, at a transfer current of 1 milliampere. When examining either the collector or emitter junction alone this method does provide a fairly reliable measure of the breakdown voltage because of the very sharp reverse characteristic associated with silicon junctions. This is not true, though, when the voltage stress is applied from emitter to collector. Under these conditions, since there is no base connection, the transfer current consists solely of the leakage current amplified by a (1 - a) term. To illustrate this, the emitter current may be written as

$$I_{\mathbf{z}} = I_{\mathbf{c}} + I_{\mathbf{l}} = \alpha c I_{\mathbf{r}} + I_{\mathbf{l}} \tag{6}$$

where I<sub>L</sub> = leakage current. Since there is no base connection in this test, it is reasonable to assume that the total transfer current I equals I<sub>E</sub> and rewriting

$$I = I_{-\infty}$$

(7)

Leakage current increases rapidly with temperature and can become appreciable above 100°C. Furthermore, alpha also tends to increase with temperature so that the combination can give rise to fairly large transfer currents which also increase with temperature. Thus, as the temperature increases, the voltage necessary to support a given leakage current would decrease. The BVCEO that was recorded is, therefore, most probably, not a true breakdown voltage but rather a measure of that voltage and temperature at which the amplified leakage current equals one milliampere. True breakdown, undoubtedly, occurs at a higher voltage. However, from an application standpoint this quasi-breakdown voltage is still significant, for it provides the circuit designer with a very real voltage limitation when operation in a common emitter configuration.

The variation of  $I_{CO}$  with temperature is shown in Figure 13 for a collector to base voltage of 5 volts.

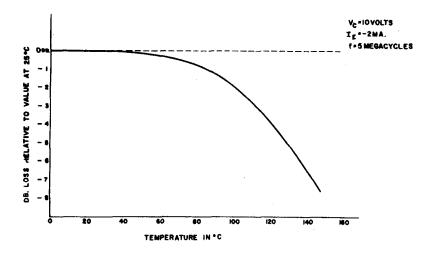

The variation of common emitter power gain with temperature is shown in Figure 14 and is seen to decrease with an increase in the ambient temperature. For a grown junction device power gain is proportional to the square root of the product of the lattice mobilities. Inasmuch as the lattice mobility is also proportional to (1/T)x, the power gain will decrease with temperature as shown.

#### CONCLUSIONS

The 4JD4A silicon transistor exhibits extremely good high frequency characteristics, which together with its low saturation resistance

of 40 ohms makes it particularly attractive for switching applications as well as for linear amplifier use.

#### CORRECTION

Frequency scale in Figure 6 is incorrect. However, the indicated alpha cutoff frequencies for the curves are correct.

#### REFERENCES

- Lesk, I. A. Grown-Diffused Germanium and Silicon Transistors for High Frequency Operation, presented at AIEE - IRE Semiconductor Device Research Conference, Purdue University, June 1956.

- 2. Hall, R. N. Melt-Back Transistors, presented at AIEE IRE Semiconductor Device Re-

- search Conference, University of Pennsylvania, June 1955.

- Moll, J. L. and Ross, I. M. Dependence of Transistor Parameters on the Distribution of Base Layer Resistivity, Proc. IRE, Vol.44, pp. 72 - 78, January 1956.

- Pritchard, R. L. Frequency Variations of Current-Amplification Factor for Junction Transistors, Proc. IRE, Vol. 40, pp. 1476 -1481, November 1952.

- Pritchard, R. L. High Frequency Power Gain of Junction Transistors, Proc. IRE, Vol. 43, pp. 1075 - 1085 - 1955

- McKay, K. G. Avalanche Breakdown in Silicon, Physical Review, Vol. 94, pp. 877 -884, May 1954

# GENERAL ELECTRIC TYPE 4JD4A SILICON NPN TRANSISTOR\* HIGH-FREQUENCY CHARACTERISTICS:

| PARAMETER                                                                                      | SYMBOL                  | TYPICAL VALUES                                                                       |

|------------------------------------------------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------|

| ALPHA-CUTOFF FREQUENCY COMMON EMITTER POWER GAIN COLLECTOR CAPACITANCE VOLTAGE FEEDBACK FACTOR | fee<br>Ga.<br>GC<br>hrb | 25 MEGACYCLES<br>13 <sub>DB</sub> AT 5 MEBACYCLES<br>14 <sub>HH</sub> f<br>60X IO -3 |

#### DC CHARACTERISTICS:

| PARAMETER                                                                                                                                                                                               | SYMBOL                                       | TYPICAL VALUES |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------|

| COMMON EMITTER CURRENT GAIN  COLLECTOR SATURATION RESISTANCE  COLLECTOR LEAKAGE CURRENT  COLLECTOR-TO-BASE BREAKDOWN VOLTAGE  COLLECTOR-TO-EMITTER BREAKDOWN VOLTAGE  EMITTER-TO-BASE BREAKDOWN VOLTAGE | hre<br>Rsc<br>Ico<br>BYcsc<br>BYcso<br>BYcso | 30             |

\* MEASURED AT 25°C

Table 1

Fig. 1 Impurity distributions at each step of the silicon diffused - meltback process.

Fig. 2

Net impurity concentrations for silicon diffused

- meltback bar.

Fig. 4

Photomicrograph of cross-sectioned bar showing base region and aluminum base contact.

izequency

Fig. 3

Uncapped view of completed silicon diffused meltback transistor.

Fig. 5 Variation of alpha with frequency.

Fig. 6 Variation of beta with frequency.

Fig. 7

Variation of grounded emitter power gain with bias.

Fig. 8 Variation of grounded emitter power with frequency.

LE = -IMA

Fig. 10 Grounded emitter collector characteristics.

Fig. 9

Variation of grounded base 'h' parameters with emitter current.

Fig. 11

Variation of DC beta with current.

Fig. 12

Variation of grounded base "h" parameters with temperature.

$${\rm Fig.}\,13$$  Variation of  ${\rm I}_{\rm CO}$  with temperature.

$\qquad \qquad \text{Fig. 14} \\ \text{Variation of grounded emitter power gain with temperature.}$

## NOISE FIGURES IN SEMICONDUCTOR DIELECTRIC AMPLIFIERS+

John M. Walker Westinghouse Electric Corp. Baltimore, Maryland Richard E. Smith Carnegie Institute of Technology Pittsburgh 13, Pa. Everard M. Williams Carnegie Institute of Technology Pittsburgh 13, Pa.

#### Introduction

Dielectric amplifiers 1,2 circuits utilize a non-linear capacitor in conjunction with other circuit elements to obtain amplification or control. In all dielectric amplifiers a low frequency control signal acts to modify the average impedance presented by the non-linear capacitor to a high frequency or carrier current. Variations in the carrier voltage resulting from impedance changes of the non-linear capacitor are rectified and constitute the amplifier output which is, consequently, directly related to the low-frequency control signal but at a higher power level.

Recent interest in dielectric amplifiers has been stimulated by the desire to obtain an amplifier with the reliability characteristics of solid-state devices, but with a very high input impedance at audio frequencies. The dielectric amplifier input impedance at audio frequencies without feedback can be made as high as about 100 megohms, whereas present solid state or transistor amplifiers have a maximum input impedance of the order of one megohm.

Two types of non-linear capacitors have been used in dielectric amplifiers - barium-strontium titanate capacitors and, more recently, the junction capacitance of reversed-biased germanium and silicon diodes. In barium-strontium titanate capacitors the capacitance non-linearity arises at high electric field strengths, close to rupture strengths. Consequently, when a bariumstrontium titanate capacitor is used in a dielectric amplifier corona tends to develop at the edges and in internal voids as a result of the high electric fields necessary for proper operation of the amplifier. Noise associated with the corona and internal breakdown of the titanate capacitor is so erratic in both time and magnitude that no quantitative results can be given for the noise figure of the dielectric amplifier; indeed the noise level has been found often to be so high that noise figure is not worth investigating.

In contrast reverse-biased semiconductor junction diodes may be operated as non-linear capacitors in an entirely satisfactory manner at low voltages and are not subject to corona or other breakdown difficulties. Their noise figure is therefore of some interest.

This paper describes the results of a study of this noise figure.

#### Part I - Circuit Design in Dielectric Amplifiers

Dielectric amplifiers utilize impedance changes resulting from the changes in reactance of a non-linear capacitor to control the amplitude of a high-frequency carrier which is subsequently rectified. Series or parallel LC circuits resonant at the carrier frequency are employed to increase the sensitivity of the carrier output to small capacitance variations resulting from the input signal. There is no reason to expect major differences in performance of the two types of amplifier circuits other than convenience in design. This paper is concerned with a single circuit, that of Figure 1.

In the circuit of Figure 1,  $L_0$  and  $C_{

m d}$  comprise the series circuit resonant at the carrier frequency.  $C_{

m d}$  is the non-linear capacitor whose average impedance to the carrier is determined by the input signal. The capacitor,  $C_0$ , prevents the fixed bias,  $V_0$ , from disturbing the operation of the detector circuit and isolates the input terminals to prevent input impedance from dependence solely on the inductance,  $L_0$ , and the internal impedance of the carrier source.  $L_1$  serves to isolate the input circuit from the carrier circuit at the frequency of the carrier.

The instantaneous value of the diodejunction capacitance is determined by the junction voltage in a manner which has been discussed in detail by Dill.<sup>3</sup> The input signal and the

\* Part of a dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering at Carmegie Institute of Technology. Work described is part of a program supported by the Brown Instruments Division, Minneapolis-Honeywell Regulator Co., and the Office of Naval Research under Contract Nonr-760(09).

carrier appear across the diode junction and thereby determine the instantaneous junction capacitance. The average junction capacitance presented to the input signal is undisturbed by the carrier signal because the carrier signal is very high in frequency; however, the capacitance at the carrier frequency is changed by the input signal. Variation in the average junction capacitance as a function of the input signal causes the carrier amplitude to vary as a function the input signal. Consequently, the output, which is the detected carrier amplitude, varies with the input, and the circuit acts as an amplifier. The relationship is nearly linear and can be entirely so for small signals.

The selection of the carrier frequency and the value of Lo in this amplifier circuit are determined by the value conveniently obtainable for the junction capacitance, Cd. Typical commercially available junction diodes with high back resistances and, therefore, suitable for high-impedance amplifiers have a junction capacitance of 5-10 micromicrofarads. As much junction capacitance as desired may be obtained by utilizing multiple diodes in parallel at the expense of reduced input impedance. For convenience in the study of noise figure reported here it was considered desirable to use a moderately low carrier frequency and consequently multiple diodes were to obtain larger values of capacitance than would be employed in an amplifier in which input impedance was actually maximized. The diode unit employed comprised five IN158 germanium junction diodes in parallel. Substantially larger values of back resistance are, of course, to be found in silicon diodes which are now available. Such dicdes were not available, however, at the initiation of this particular study.

A curve of the capacitance of the multiple diode unit (in the back biassed direction) is shown in Figure 2.

#### Noise Figure Measurements

Noise figure was measured by a substitution method. The experimental arrangement is shown in Figure 3. The cutput of the single stage dielectric amplifier was naturally too low for direct measurement. Consequently the output of the dielectric amplifier was fed into a low-noise amplifier to raise its level to a suitable value for a wave analyzer. The wave analyzer used had a four cycle per second bandwidth. The four cycle band of noise from the wave analyzer was fed into a cathode-follower which served to match the impedance of the wave analyzer to a thermocouple indicating device.

Noise output power of the dielectric amplifier was measured by recording the deflection on an output meter for various values of resistance at the amplifier input. Absolute calibrations were obtained with a continuous-wave standard signal generator substituted for the resistor at

the amplifier input. The continuous-wave r.m.s. voltage that was equivalent to the r.m.s. noise voltage appearing at the amplifier output was used to calculate the square of the r.m.s. value of the output noise per cycle with the expression:

in which Vnc = voltage of continuous wave standard signal generator r.m.s. d<sub>f</sub> = Bandwidth of the noise signal e<sub>no</sub><sup>2</sup>= r.m.s. output noise voltage squared

Amplifier output noise power per cycle P, is then;  $P = \overline{C_{no}} / R_{L}$ , in which  $R_{L}$  is the output load resistance. Noise power in the output originating from the thermal noise of the source was determined by determining the voltage gain of the amplifier with a continuous-wave generator and then calculating the noise power per cycle, Ps, due to the thermal noise of the source with the expression:

in which  $R_{\rm L}$  is the source resistance and G is the voltage gain of the amplifier. The noise figure, F, is then:

This procedure for measuring noise figure was advantageous because an input signal to the amplifier was not required during the noise measurement itself. Use of a standard input signal to the amplifier during noise measurement tends to limit the measurements to cases in which the source impedance of the amplifier is somewhat less than 0.5 megohms because of the low impedances of standard signal sources and the difficulty of applying transformers to modify source impedances to megohm values.

Results of the measurements of the output noise power of the dielectric amplifier are shown in Figure 4. The signal source resistance was varied for the different sets of noise data to determine the dependence of the amplifier output noise power on the source resistance. As can be seen from the curves of Figure 4, the amplifier output noise decreases with decreasing source resistance and increasing frequency.

Noise power in the output of the dielectric amplifier resulting from the thermal noise of the source resistance was calculated after determining the amplifier gain.

Using the results of the measurements of the output noise power and the calculated output noise power due to the thermal noise of the source resistance the noise figure of the dielectric

amplifier was calculated. Figure 5 shows the noise figure of the dielectric amplifier as a function of frequency for various values of the source resistance, R<sub>1</sub>. Such curves permit determination of the optimum value of source resistance since as source resistance is reduced the noise figure decreases until a critical value is reached. Further reduction results in an increase in noise figure. The data of Figure 5 are applicable to determination of optimum source resistance at signal frequencies of 1.5 kilocycles and above.

From the data presented the conclusions that can be drawn are; 1) noise figure decreases as frequency increases 2) the noise figure is a function of source resistance, and 3) there exists an optimum source resistance to minimize the noise figure, and this optimum resistance is different for every frequency. A more thorough explanation of the parameters governing the noise figure resulted from an investigation of the sources of noise and the representation of these sources in an equivalent circuit which are described in the next section.

#### Noise Sources and Equivalent Circuit

The general characteristics of noise in junction devices have been reported in the literature 4. An investigation of the particular noise characteristics of the composite five unit diode was made prior to investigation of the influence of these characteristics in dielectric amplifier applications. The equivalent-circuit parameters of the diode shown in Figure 6a were evaluated before noise measurements were taken.

Noise measurements on the diode employed the same equipment used to measure the amplifier noise figure, Figure 3, with the input to the low-noise amplifier of the noise measuring equipment connected to the circuit shown in Figure 6b.  $R_{\rm O}$  in Figure 6b was varied to determine the effect of this resistance on the diode noise output and  $V_{\rm I}$  was varied for different measurements to find the dependence of the diode noise on reverse bias.

In Figure 7 all the noise measurements taken on the set of junction diodes for three values of bias are consolidated. The shaded areas represent all the measurements taken at a particular value of bias by varying R<sub>o</sub>. The open circuit noise voltage, e., was obtained from measurements of e., by the equation relating e., which is

in which

$$R = \frac{R_a R_o}{R_a + R_o}$$

Subscript a refers to low-noise amplifier components.

The agreement of the noise data taken at a particular value of bias corresponding to five values of R<sub>0</sub> with no more descrepancy than that represented by a band 3db wide when used to determine \(\frac{\texts\_0}{\texts\_0}\) suggests the reliability of (1) the value obtained for R<sub>d</sub>, (2) the general measuring technique in that results are repeatable, and (3) the placing of the diode noise generator in the resistance branch of the equivalent circuit.

The next question that arises is "does the noise originating in the diodes act as any other signal in changing the junction capcaitance of the diode?" This question has a bearing on the extent to which the diode noise influences the output of the dielectric amplifier. Referring to Figure 1 it can be seen that the output of the dielectric amplifier is taken across Lo and the internal impedance of the carrier source. Both of these have an impedance of less than ten ohms over the audio frequency band; whereas, Co, which is in series with the combination of L and the carrier source impedance and acts as a voltage divider for any audio signal originating in the diode, has an impedance greater than 10° ohms over the audio frequency band. Thus for all practical purposes the point at which the output of the dielectric amplifier is taken is at ground potential for any audio signal originating in the diode, and as a result, any audio signal, such as noise originating in the diode can only affect the output of the dielectric amplifier by changing the junction capacitance.

It has been found necessary to assume that the diode noise generator acts in series with the diode dynamic resistance, Rd, in order to obtain calculated values consistent with noise measurements on both the diodes and dielectric amplifier. When the diode noise generator is in series with the dynamic resistance, Rd, a decrease in Ro decreases the noise appearing across the junction capacitance, Cd, and thus decreases the noise power output of the dielectric amplifier. This result is in agreement with noise measurements taken on the dielectric amplifier. If the noise generator were placed in series with the junction capacitance or in series with the parallel combination of junction capacitance and dynamic resistance, decreasing Ro would increase the noise appearing across the junction capacitance. Increasing the noise voltage appearing across the junction capacitance increases the noise power output of the dielectric amplifier which is contrary to the effect observed in dielectric amplifier noise measurements.

Noise measurements on the diode indicate that the noise originating in them behaves as 1/f over the audio frequency range; however, noise measurements on the dielectric amplifier indicate noise independent of frequency for frequencies above 1kc and 1ow values of R<sub>O</sub>.