# Analog Switches and Their Applications

Siliconix

# **Analog Switches** and Their Applications

**Introduction to FET Switches**

Switch and Driver Circuits

Multiplexing CHAPTER

Sample-and-Hold Circuits

N-path Filters CHAPTER 5

Signal Conversion using Analog Switches CHAPTER

Applications Information CHAPTER

Copyright © by Siliconix incorporated. All Rights Reserved. Printed in the U.S.A. This book, or parts thereof, may not be reproduced in any form without permission from Siliconix incorporated.

Information contained in this book is believed to be accurate and reliable. However, we cannot accept responsibility for its use, nor for any infringement of patents or rights of others which may result from its use. Publication of this information does not imply any authority or license for the use of any patented feature.

Siliconix incorporated, 1976

#### **Preface**

An abundance of literature is available on discrete semiconductor devices and integrated circuits, wherein the applications emphasis is mainly on linear and digital circuitry. Furthermore, most written information on sample-and-hold circuits, analog-to-digital and digital-to-analog converters, multiplexers and N-Channel filters tend to concentrate on systems considerations. Comparatively little has been written on the subject which bridges the linear and digital fields, namely analog switching and the effects that analog switches have on system performance.

The object of this book is to introduce the reader to FET analog switches and familiarize him with the way that the switch control or driver circuit affects switch performance. By developing an understanding of the circuit combinations that can be used for analog switching, the reader is then able to analyze the effects on system performance. With this objective in mind the contents are divided into seven chapters.

With the exception of chapters one and seven, all chapters are subdivided into two major sections. The first subsection is a theoretical discussion of analog switches. The second subsection is practical application circuits.

Chapter one is an introduction to the FET as a switch, the second chapter describes various driver circuits and their interaction with FET switches. The next four chapters are devoted to describing the performance of Analog Switches in four different fields of signal handling. Chapter seven contains a collection of applications material written by Siliconix personnel.

## CONTENTS

| Chapter | 1 Introduction to FET Switches Page | Chapter                | 3 Multiplexing                 | Page |

|---------|-------------------------------------|------------------------|--------------------------------|------|

| THEC    | DRETICAL DISCUSSION                 | THE                    | ORETICAL DISCUSSION            |      |

| 1.1     | Introduction 1-1                    | 3.1                    | Introduction                   | 3-1  |

| 1.2     | Comparison of Electromechanical     | 3.2                    | Factors Affecting System       |      |

|         | and Semiconductor Switches 1-1      |                        | Performance                    |      |

| 1.3     | Elementary Semiconductor            | 3.3                    | Considerations of Multiplexer  |      |

|         | Theory 1-5                          |                        | Errors                         |      |

| 1.4     | The p-n Junction 1-6                | 3.4                    | FET Multiplexer Performance    |      |

| 1.5     | The Bipolar Transistor 1-8          | 3.5                    | Principal Applications Areas o | f    |

| 1.6     | The Field Effect Transistor 1-9     |                        | Multiplexers                   |      |

| 1.7     | Junction FETs1-10                   | 3.6                    | Primary Requirements of Anal   |      |

| 1.8     | MOSFETs 1-15                        | 2.7                    | Switches as Multiplexers       |      |

| 1.9     | The FET as a Switch 1-18            | 3.7                    | Analog Signal Characteristics. |      |

| 1.10    | Summary                             | 3.8                    | Techniques Used in Multiplexi  | _    |

|         | •                                   | 3.9                    | Supermultiplexing              | 3-29 |

| Chapter | 2 Switch and Driver Circuits Page   | 3.10                   | Examples of Multiplexer        | 2.24 |

|         |                                     | 2.11                   | Applications                   |      |

| THE     | DRETICAL DISCUSSION                 | 3.11                   | Conclusions                    | 3-38 |

| ٠.      | 2.1                                 | PRAG                   | CTICAL APPLICATIONS            |      |

| 2.1     | Introduction                        |                        |                                |      |

| 2.2     | Types of FET Switches 2-1           | 3.12                   | Application Circuits           | 3-39 |

| 2.3     | Driver Circuits                     |                        | References                     |      |

| 2.4     | Interface Circuits 2-15             |                        |                                |      |

| 2.5     | General Comments on Driver          |                        | ,                              |      |

|         | Gates2-18                           | <u></u>                |                                | _    |

| 2.6     | Sources of Error 2-21               | Chapter                | 4 Sample-and-Hold Circuits     | Page |

| 2.7     | Noise Immunity 2-37                 |                        |                                |      |

| 2.8     | Choosing the Optimum Driver         | THEORETICAL DISCUSSION |                                |      |

| •       | Gate 2-40                           |                        | •                              |      |

| •       | •                                   | 4.1                    | Introduction                   |      |

| PRAC    | CTICAL APPLICATIONS                 | 4.2                    | Basic Sample-and-Hold Circuit  |      |

|         | •                                   | 4.3                    | Types of Circuits              |      |

| 2.9     | Application Circuits 2-48           | 4.4                    | Sources of Error               |      |

| 2.10    | References                          | 4.5                    | Methods for Reducing Errors    | 4-14 |

| 4.6                           | Miscellaneous Applications of IC Switches and Multiplexers in       | 6.10     | Advantages Gained by the Use of FET Switches6-14              |

|-------------------------------|---------------------------------------------------------------------|----------|---------------------------------------------------------------|

|                               | Sample-and-Hold Applications 4-20                                   | 6.11     | Summary of A-D and D-A Conversion Applications 6-14           |

| 4.7                           | Low Level Sample-and-Hold 4-29                                      | 6:12     | Chopping 6-14                                                 |

| PRA                           | CTICAL APPLICATIONS                                                 |          | Performance and Selection of FET Switches for Choppers 6-15   |

| 4.8<br>4.9                    | Application Circuits         4-37           References         4-38 | 6.14     | Summary of Chopping Applications 6-23                         |

| Chapter 5 N-path Filters Page |                                                                     | PRAC     | CTICAL APPLICATIONS                                           |

|                               |                                                                     | 6.15     | Application Circuits 6-24                                     |

| THEORETICAL DISCUSSION        |                                                                     |          | References                                                    |

| 5.1<br>5.2                    | Introduction         5-1           Basic N-path Filter         5-2  | Chapter  | 7 Applications Information Page                               |

| 5.3                           | Analysis                                                            | ~ 1      | FFT A 1 C (A 1)                                               |

| 5.4                           | Bandpass Filter Analysis 5-8                                        | 7.1      | FETs as Analog Switches (AN72-2)                              |

| 5.5                           | Shunt Switched Bandpass Filter 5-12                                 | 7.2      | IC Multiplexer Increases Analog Switching Speeds (AN73-2)     |

| PRA                           | CTICAL APPLICATIONS                                                 | 7.3      | Switching High-Frequency Signals with FET Integrated Circuits |

| 5.6                           | Applications 5-12                                                   |          | (AN73-3)                                                      |

| 5.7                           | Summary5-21                                                         | 7.4      | Driver Circuits for the JFET<br>Analog Switch (AN73-5)7-27    |

| 5.8                           | References                                                          | 7.5      | An Introduction To FETs (AN73-7)                              |

|                               | r 6 Signal Conversion Using                                         | 7.6      | Analog Switches in Sample-and-                                |

| Analog Switches Page          |                                                                     | 7.0      | Hold Circuits (AN74-2)7-57                                    |

| THEORETICAL DISCUSSION        |                                                                     | 7.7      | CMOS Analog Switches (AN75-1)7-63                             |

|                               |                                                                     | 7.8      | DG300 Series Analog Switch<br>Applications (AN76-6) 7-79      |

| 6.1                           | Introduction 6-1                                                    | 7.9      | Multiplexer Adds Efficiency to                                |

| 6.2                           | D-to-A Converters                                                   |          | 32-Channel Telephone System                                   |

| 6.3                           | A-to-D Converters                                                   | <b>-</b> | (TA73-1)7-93                                                  |

| 6.4                           | Deglitching 6-6                                                     | 7.10     | Designing with Monolithic FET<br>Switches (TA73-2)            |

| 6.5                           | Coding 6-6                                                          |          | Switches (1A/3-2) /-94                                        |

| 6.6                           | Ranging                                                             | A        | ix I                                                          |

| 6.7                           | Multiplying Conversion 6-8  Delta-Sigma Modulation 6-9              |          |                                                               |

| 6.8<br>6.9                    | Switch Parameters6-10                                               |          | fices                                                         |

| 0.9                           | Switch Latameters                                                   | Dates Of | inco                                                          |

#### Chapter 1

#### **Introduction to FET Switches**

#### 1.1 INTRODUCTION

One of the most common control elements in electrical circuitry is the simple ON-OFF switch. This has evolved over the years from the manually operated circuit breaker of the early experimenters to the multiswitch integrated circuit of today. In every application, the function of the switch remains the same, viz. to isolate or connect two sections of an electrical circuit.

Until the advent of the thermionic valve, switching action was effected almost exclusively by the manual or electromechanical opening and closing of metal contacts. The operation of mechanical switches is easily understood and they require a very simple form of maintenance. However, with today's increasing demands of modern circuits, it has become evident that electromechanical switches alone cannot meet all requirements and that there are applications in which only electronic types are viable. By far the most popular of these is the semiconductor switch.

In recent years, semiconductor switches have made inroads into application areas that hitherto have been exclusively the domain of electromechanical devices. Solid-state switches are now used in sample-and-hold circuits; multiplexers; high power switching; chopper circuits etc., whereas in the past some form of electromechanical switch would have been used.

### 1.2 COMPARISON OF ELECTROMECHANICAL AND SEMICONDUCTOR SWITCHES

#### 1.2.1 General

The types of electromechanical and semiconductor switches available are many and varied, each having some advantages and some disadvantages. The choice between a mechanical and semiconductor switch usually depends upon the application. The performance and major switching parameters of both types are compared in the following sections.

#### 1.2.2 ON Resistance

Most electromechanical switches initially have very low ON-resistance, typically tens of milliohms. During their lifetime, however, wear at the switch contact surfaces can increase this resistance value by a factor of a hundred or more. Semiconductor switches have higher ON resistance but their resistance is constant over the switch lifetime. Field effect transistors are available with ON resistances of less than 2 ohms and some high power bipolar transistors can have collector-emitter saturation resistances of less than 100 milliohms. If the application required a switch with near zero ON resistance, the main contender would then be the electromechanical type, but if a constant ON resistance over the switch lifetime is of prime importance, then the semiconductor switch is far more preferable.

CHAPTER

#### 1.2.3 **OFF-Isolation**

The maximum OFF resistance of electromechanical switches is limited by surface conduction along the package. This resistance is reduced considerably in moist environments or through careless handling. Nevertheless, extremely high OFF resistance is possible, and with specially treated reed switches this can be as high as 10<sup>12</sup> ohms. The OFF resistance of semiconductor switches can have the same order of magnitude. The value of the semiconductor switch leakage current is roughly proportional to the square root of the voltage across the junction, and it increases with increasing temperature. Values of junction leakages can be less than one picoamp at 25°C for low power field effect transistor switches.

#### 1.2.4 Switching Speed

Semiconductor switches comprise no moving parts, hence their switching speed is not limited by contact inertia. Consequently, switching times of nano-seconds are easily attainable and maximum switching rates are often in excess of 10<sup>6</sup> operations per second. By comparison electromechanical switches are slow indeed. Even the fastest of reed switches have turn-on/turn-off times measured in milliseconds, and maximum switching rates rarely exceed a few hundred operations per second.

#### 1.2.5 Maximum ON Current

Power dissipation ratings limit the maximum currents that semiconductor devices are able to switch: collector currents of up to 100 amperes are possible with bipolars, while the largest field effect transistors at present have maximum drain currents in the region of 10 amperes. High power switches, with forced cooling, can conduct currents of up to 1000 amperes. Some electromechanical switches are capable of conducting currents of many thousands of amperes, but switching such high currents with these devices causes severe arcing and burning of contact faces. Electromechanical switches capable of conducting thousands of amperes are therefore normally switched when the load current is zero.

#### 1.2.6 Maximum OFF Voltage

For electromechanical switches the maximum OFF voltage is limited by the voltage breakdown of the insulating dielectric. For large switches, with wide contact spacing, the maximum OFF voltage can be many hundreds of thousands of volts. The smaller electromechanical devices, reed switches, miniature relays etc. are capable of switching several hundreds of volts.

Operation of semiconductor switches relies on p-n junction action. Consequently the reverse biased breakdown voltage of the junction sets a limit to the maximum voltage that can be switched. Some thyristor devices have breakdown voltages as high as 1000 volts, while bipolar and field effect transistors can have maximum switching voltages in the region of 200 volts. It must be stressed that this is more than adequate to meet the needs of most semiconductor systems which normally run off supplies of less than 50 volts.

#### 1.2.7 Minimum Analogue Voltage

The minimum analogue voltage switchable is determined by the total error signal contributed by the switch. One source of error in electromechanical devices is the

thermal EMF generated across the moving contacts. This can be tens of microvolts. A much larger error, prevalent in dry reed relays, results from the dynamic 'noise generated by contact bounce. This can be as high as 500 microvolts peak-to-peak initially, decaying to tens of microvolts after a few milliseconds.

Bipolar semiconductor switches require a finite collector-emitter voltage to maintain conduction. This voltage which is seldom less than a few millivolts, appears as an offset and severely limits the minimum value of analogue voltage that can be switched.

Field effect transistors have no such offset and are used extensively in low voltage switching applications. The thermal EMFs generated in field effect transistors are virtually zero, owing to their near symmetrical structure. Factors affecting the low level analogue switching voltage capability of FETS are switching transient breakthrough into the channel from the gate, and thermal noise due to the channel ON resistance. Both these topics are considered in detail in Chapters 2 and 3.

#### 1.2.8 Drive Signals

Compatibility with existing circuits is an important consideration when deciding on a switch type. If, as is frequently the case, there is some degree of involvement with computers or other electronic systems which require standard logic control signals, then switching systems which respond to the same type of logic signals are desirable. The voltage levels required to operate electromechanical switches normally vary between 1 and 250 volts and most require a driving power greater than 50mW. Since logic driving circuits are limited in their power handling capability, this necessarily means that electromechanical switches usually require some form of interfacing with their logic control elements. Most semiconductor switches, owing to their lower drive power requirements, are directly compatible with transistor logic systems.

#### 1.2.9 Switching Life

Since electromechanical switches comprise some moving parts, their operating life is affected by mechanical wear; in particular, wear at the contact surfaces. This can lead to an increase in ON resistance and the eventual welding together of the contacts. Figures for operating life times or switching cycles are difficult to assess since they depend on operating conditions. A dry reed relay switching at the rate of 100Hz would perform 10<sup>8</sup> switching operations in only 300 hours which is approximately the minimum expected lifetime of the relay.

This figure would be greatly reduced if the relay were switching into an inductive or capacitive load. Inductive loads produce arcing at the switch contacts because of the back EMF induced when the switch is opened. Capacitive loads accelerate contact wear due to current surges when the switch turns on. The switching life of a semiconductor device is not limited by mechanical wear and provided it is operated within its maximum specified ratings it can continue to switch almost indefinitely. For example, the mean time before failure (MTBF) of semiconductor devices is usually well in excess of 100,000 hours. Consequently, a semiconductor switch operating at 10<sup>6</sup> Hz could perform in excess of 3.6 x 10<sup>14</sup> cycles during its operating life.

CHAPTER 3

#### 1.2.10 Reliability

In many applications the ability of a device to survive in adverse environments is most important. Military and space equipments need to withstand extremes of temperature, pressure, mechanical shock etc. without impairing operation. In general, semiconductor devices exhibit greater resistance to adverse environments than electromechanical types. Semiconductors are less susceptible to damage or change of state through shock, vibrations or high accelerations and do not suffer from sticking contacts due to freezing at very low temperatures. Their electrical characteristics are dependent on temperature and are somewhat prone to change when subjected to high energy radiation. However, this does not prevent their use in military equipment requiring an operating temperature range of -55°C to 125°C, or in satellite applications with the attendant high radiation environment.

#### 1.2.11 System Size

Size, power consumption and weight of components become increasingly important as systems grow more complex. In this respect, the semiconductor switch has distinct advantages over its electromechanical counter part. The use of integrated circuits and modern fabrication techniques enable multiple switches to be contained in a single robust package. The Siliconix DG506, for example, has 16 switches with their binary decode circuitry in a 28 pin package measuring only 1.4 inches x 0.6 inches. An equivalent system using relays would be considerably more bulky.

#### 1.2.12 System Costs

Total system costs should take into account not only the initial capital outlay but also factors such as maintenance costs, personnel training and the secondary costs resulting from system failures.

Switch for switch, the costs for electromechanical and semiconductor types are comparable, but as circuit complexity increases the cost per switch for semiconductor systems using integrated circuits falls, giving them a considerable price advantage over electromechanical types. Costly equipment down-time is also greatly reduced with semiconductor systems due to their higher reliability and longer lifetimes.

#### 1.3 ELEMENTARY SEMICONDUCTOR THEORY

It is relevant at this stage to present a brief description of semiconductors and their application as switches.

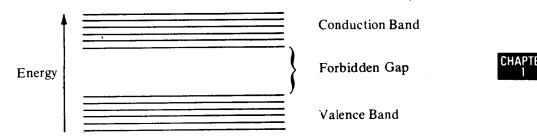

Quantum mechanics shows that electrons in a solid can be represented as occupying discrete energy bands which are separated from each other by forbidden energy gaps.

Fig. 1.1 Comparative energy levels

Fig. 1.1 represents the two outermost bands of any atom, the valence band and the conduction band, separated by a forbidden energy gap. It is the availability of electrons in the conduction band which determines the conductivity of a solid. Conduction can only occur if electrons arrive in the conduction band from the valence band. For this to happen, the electrons must receive sufficient energy to enable them to 'jump' the forbidden energy gap between the two bands.

If the forbidden energy band is wide, and prevents electrons appearing in the conduction band, the material is an insulator. Electrons will move from the valence to conduction band if sufficient energy is imparted to them. The application of a high electric field will do this. Thus, for all insulators, there is a specific voltage at which their insulating properties break down. In metals, the valence and conduction bands overlap with the result that electrons are freely available in the conduction band and can be persuaded to move between atoms when only a small voltage is applied. Thus, metals are good conductors of electricity.

In certain materials, the thermal energy imparted to some electrons at ambient temperatures is sufficient to enable them to cross the forbidden energy gap. For these materials there is a finite probability of electrons appearing in the conduction band. Therefore these materials will exhibit slight electrical conductivity which increases with increasing temperature. Such materials are referred to as semiconductors. Although many semiconducting materials exist, the two most widely used are silicon and germanium, with silicon being the more common of the two at present.

The width of the forbidden energy gap in pure silicon is of the order of 1.1 electron-volts at room temperature; the average thermal energy of the valence electrons is 0.025 electron-volts; thus, the probability of electrons appearing in the conduction band is small and the conductivity is very low. Conductivity can be increased if certain impurities are added to the semiconductor.

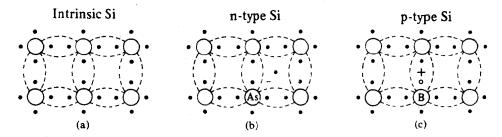

Fig. 1.2 Schematic crystal structure of intrinsic and doped silicon.

Both silicon and germanium have a valency of 4. This means that a pure or intrinsic semiconductor will have a crystal structure as in Fig. 1.2a. Each silicon atom binds with its neighbouring atom to produce a stable configuration of eight valence electrons associated with each nucleus. If an impurity atom, such as arsenic with a valency of 5 is introduced into the crystal structure (Fig. 1.2b), then a free electron results from the binding of the valence electrons. This electron can be easily elevated to the conduction band and, therefore, contribute to electrical conduction. The arsenic atom can be said to have donated a free electron to the semiconductor and for this reason the impurity atom is known as a donor atom. Obviously the greater the concentration of donor atoms, the greater will be the number of free electrons and the greater the conductivity. Semiconductors treated with donor impurities are known as n type. The existence of the free electrons does not constitute a net negative charge in the structure as associated with it is a localised positive charge on the arsenic atom. This positive charge also contributes to electric current but to a lesser extent. To distinguish between the two types of charge carriers in n type semiconductors, the free electrons are known as majority carriers and the positive charges as minority carriers.

If a trivalent impurity, such as boron or indium is introduced, the binding of the valence electrons results in a space or hole in the valence band (Fig. 1.2c). An electron from a neighbouring atom will move to fill the hole thereby causing a hole to appear in its place. The result is that a hole behaves similarly to a free electron but with a positive charge. It will contribute to electric current since a movement of holes in one direction is effectively the same as a movement of electrons in the opposite direction. Impurity atoms of this type are known as acceptor atoms and a semiconductor so treated is called p type. In a p type semiconductor, the holes are the majority carriers and the electrons are the minority carriers.

The process of adding impurities to semiconductors is known as doping. Impurity atoms may be either diffused into the pure semiconductor at high temperature or injected into the crystal structure using Ion Implantation techniques.

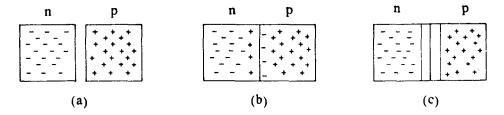

#### 1.4 P-N JUNCTION

If n and p type semiconductors are joined, then at the junction the free electrons of the n type and the holes of the p type will be mutually attracted and will drift towards each other (Fig. 1.3b). Some will cross the junction producing a potential drop which tends to prevent any further flow of charge carriers across

the junction. This results in regions deficient in majority charge carriers on both sides of the junction. These regions act as insulating regions and are known as depletion layers (Fig. 1.3c).

Fig. 1.3 Showing formation of a depletion layer at a p-n junction.

If a voltage supply is now applied to the junction with the negative terminal to the **n** type and the positive to the **p** type, it will oppose the inherent potential barrier already existing at the junction. If the applied voltage is greater than the potential barrier, it will cause more carriers to cross the junction and an electric current results. In this arrangement, the junction is said to be forward biased. If the voltage is applied with opposite polarity, then effectively the charge carriers in the **n** and **p** regions will be attracted away from the junction, resulting in an increase in the width of the depletion layer with an increase in potential drop across the junction which exactly opposes the applied voltage. Thus, very little current can flow and the junction is said to be reverse biased.

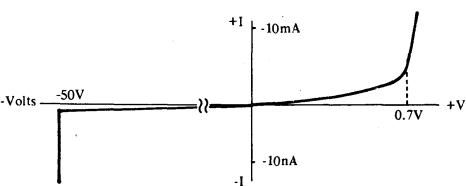

Fig. 1.4 V/I characteristic for silicon p-n junction.

A junction of n and p type semiconductors performs the function of a rectifying diode as shown by the voltage/current characteristic of Fig. 1.4. This reverse bias current is temperature dependent; its value for silicon approximately doubles for every 10°C increase in temperature. Other factors affecting the reverse current are dopant concentrations and junction area. The value is typically of the order of 1 nanoamp at 10 volts, but can be less than 1 picoamp. The reverse current increases sharply when the reverse voltage becomes sufficiently high. This is due to avalanche breakdown across the junction and to a large extent is dependent upon dopant concentration. A decrease in dopant concentration will result in an increased breakdown voltage. Breakdown voltages can be in excess of 1000V.

For a junction that consists of **n** and **p** conducting regions separated by an insulating depletion layer, there is associated with it a particular value of capacitance. This capacitance normally degrades the performance of semiconductor devices and efforts are usually directed at keeping the capacitance to a minimum. Factors affecting the value of junction capacitance are applied voltage, junction area, and impurity concentration. As the reverse bias voltage increases, so the width of the depletion layer increases thus reducing the capacitance.

A reduction in impurity concentration produces an increase in the depletion layer width for a given reverse bias voltage, and consequently a reduction in capacitance. Minimum junction capacitance is aimed for in most products, but varactor diodes make use of this voltage dependent characteristic and are designed for specific capacitance/voltage sensitivities. Values of junction capacitances can vary from less than 1 pico farad to greater than 10 nano Farads.

#### 1.5 THE BIPOLAR TRANSISTOR

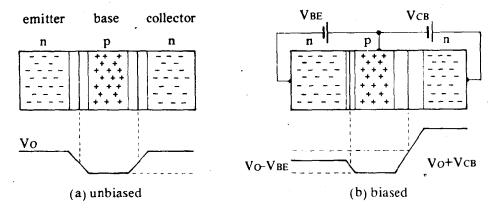

If a second p-n junction is added in close proximity to the first, a three terminal n-p-n or p-n-p device is produced. Such a device is the basis of a bipolar transistor. An n-p-n type bipolar schematic structure is shown in Fig. 1.5.

Fig. 1.5 Bipolar schematic structure

Fig. 1.5a shows the structure and potential distribution when no external voltages are applied. Under this condition the potential steps on each side of the centre or base region are equal and there is no net charge transfer across the junctions.

If external voltages are applied as in Fig. 1.5b, the base-emitter junction will be forward biased and the base-collector junction reverse biased. There will be a reduction in the base-emitter potential barrier and electrons will be injected into the base region from the emitter. These would normally recombine with holes in the base region, but if the width of the depletion layer of the reverse biased collector-base junction extends sufficiently into the base region, most of the electrons will be swept across to the collector where they recombine with holes to form collector current.

For a basic understanding of how the device operates, consider positive or negative charges (positive for a p-type emitter, negative for an n-type) flowing

from the emitter into the base region. A fraction x (say) of these recombine with charges of opposite polarity in the base region and so gives rise to base current. The remaining (1-x) fraction of charges reaches the collector-base depletion region across which they are accelerated into the collector. The algebraic sum of collector and base currents is equal to the emitter current YIE). The ratio of collector to base currents is (1-x)IE: xIE; that is, (1-x): x. For a given bipolar transistor, x is practically constant at constant temperature, and for normal bipolar action is x1. Current amplification can therefore be effected: a small increase in base current results in a much larger increase in collector current.

For high current gain performance, the number of electrons arriving at the collector from the emitter must be maximised. Therefore, the collector-base depletion layer must be made wider by lightly doping the base, and the base thickness made as small as possible. The number of electrons emitted is maximised by heavily doping the emitter with respect to the base, which inherently results in a low base-emitter breakdown voltage. The collector is lightly doped near the junction but heavily doped at the point where metal contact is made to it, and sometimes in the regions away from the junction, to reduce saturation resistance. This gives the desired low contact resistance. It is implicit in the foregoing discussion that a bipolar will function with the collector and emitter interchanged. This is so, but only with a low inverse current gain and lower operating voltages.

#### 1.6 THE FIELD EFFECT TRANSISTOR

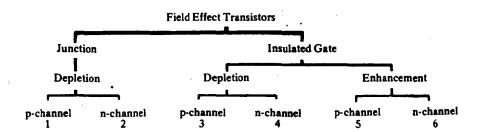

Bipolar transistors are often termed minority carrier transistors by virtue of the minority carrier current through the base. However, the field effect transistor (FET) relies on majority carrier current for its operation. A FET consists essentially of an electrically conducting channel (either n- or p- type) whose conductivity may be controlled by applying a voltage to a controlling gate terminal. There are two distinct branches of the FET family—the JUNCTION FET and the INSULATED GATE FET, with further subdivisions as shown in Fig. 1.6. The two types will be reviewed in detail.

Fig. 1.6 FET family tree

CHAPTER

#### 1.7 **JUNCTION FETS**

#### 1.7.1 General Layout and Characteristics

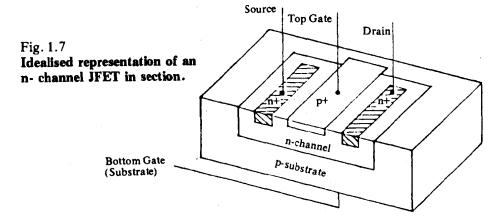

The JFET consists of a channel of n- or p- type semiconductor embedded in a semiconductor region of opposite polarity.

Fig. 1.7 shows an idealized n-channel JFET where the p-type region is the controlling gate and the n-type channel has electrical connections made at both ends (Source and Drain). Electrical connection to the gate is made at either the substrate or top gate contact. The controlling gate is isolated from the conducting channel by virtue of the reverse biased p-n junction. To understand how the JFET works, one must consider its operation under two distinct bias conditions.

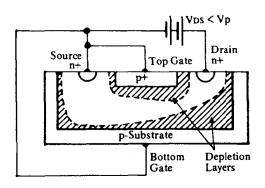

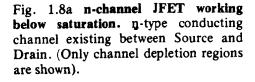

Fig. 1.8b n-channel FET working in saturation region. n-channel is almost cut off between Drain and Source. (Only channel depletion regions are shown).

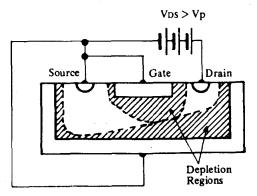

Fig. 1.8a illustrates the idealized cross sectional diagram of an n-channel JFET with a positive voltage VDs applied between drain and source, and with the gate shorted to the source. Since the drain is positive with respect to source and gate, the drain-gate junction will always be reverse biased and practically no gate current will flow. A depletion region will form over the whole p-n junction area and this will be physically greatest at the high field regions between the drain and gate. The existence of the depletion region reduces the effective channel width and thereby increases the channel resistance. An increase in the value of VDs increases the width of the depletion region. This results in a reduction of the channel cross-section and an increase in channel resistance. Above a certain VDs value, the channel will no longer exhibit a resistive characteristic but reaches a state of saturation Fig. 1.8b where the channel current changes very little for a large change in VDs. The JFET is then said to be saturated. This saturation current is given the symbol IDSS which is an abbreviation for the drain to source current with the gate short-circuited. The ID/VDs characteristic at VGs = 0V is shown in Fig. 1.8c. Initially ID increases almost linearly with VDs until the depletion region begins to 'pinch-off' the channel, and the curve flattens out at the IDSS value. The value of VDS at which this takes place is termed the 'pinch-off' voltage and is given the symbol Vp.

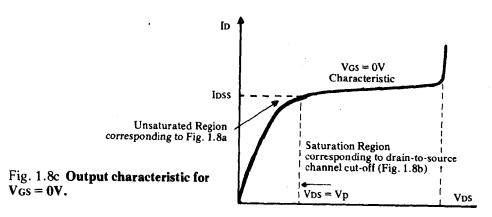

Fig. 1.9

n-channel JFET showing channel

depletion layer when drain-source

voltage VDs=0V and VGs=negative

voltage.

Consider the case of Fig. 1.9 where  $V_{DS} = 0V$  and a negative gate-source voltage (— $V_{GS}$ ) is applied. The depletion region is controlled mainly by the gate-source voltage  $V_{GS}$ : the depletion region widens as  $V_{GS}$  becomes more negative and

consequently the channel resistance increases. Therefore, for values of VDs at or near to zero volts, the drain-source resistance is controlled by VGs. As VGs increases, the channel resistance increases until a voltage VGS(off) is reached, at which level the channel is completely 'pinched-off' and no drain current allowed to flow. This value of VGS(off) is equal in magnitude but opposite in polarity to Vp, and is usually referred to as the 'Gate Pinch-off' Voltage'. It also is given the symbol Vp.

BELOW PINCH OFF C ABOVE PINCH-OFF VGS - 0

Fig. 1.10

Family of output characteristics for an n-channel JFET.

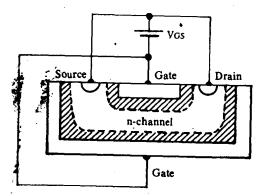

A combination of VDs and VGs bias conditions results in a family of characteristics (Fig. 1.10). From this it is seen that there are two important modes of operation for a JFET, namely:

- 1) Operation to the left of the pinch-off voltage locus. This is known as the unsaturated or triode region where ID is governed by both VDs and VGs. As will be seen later, the triode region is most important when the JFET is used as an analogue switch.

- 2) Operating to the right of the pinch-off voltage locus. Here the JFET is in the saturated or pentode region and ID is controlled almost entirely by VGs. In this region, the JFET is most useful as a voltage amplifier.

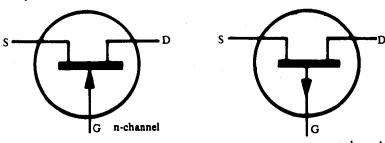

The operation of a p-channel JFET is similar to the n-type except that voltage polarities and current directions are reversed. The symbols for both n and p channels are shown in Fig. 1.11. The arrows on the gate show the polarity of the gate-channel junction.

Fig. 1.11 Symbols for Junction FETs

p-channel

The application of a negative voltage to the gate of an n-channel JFET increases the depth to which the depletion layer extends into the channel, and so reduces the conductivity of the channel. A small positive voltage on the gate has the