# ROCEEDINGS

# PROCEEDINGS OF THE 1994 BIPOLAR/BICMOS CIRCUITS AND TECHNOLOGY MEETING

1994

Minneapolis, Minnesota Oct. 10-11, 1994

Sponsored by IEEE

94CH35709 94-

94-78759

### PROCEEDINGS OF THE 1994 BIPOLAR/BICMOS CIRCUITS AND TECHNOLOGY MEETING

# SPONSURED BY IEEE ELECTRON DEVICES SOCIETY

### IN COOPERATION WITH

# IEEE CIRCUITS AND SYSTEMS SOCIETY IEEE TWIN CITIES SECTION

EDITED BY C. R. SELVAKUMAR

Papers have been printed without editing, as received from the authors.

All opinion expressed in the Proceedings are those of the authors ands are not binding on the Institute of Electrical and Electronic Engineers.

Copyright and Reprint Permission: Abstracting is permitted with credit to the source. Libraries are permitted to photocopy beyond the limits of the US. copyright law for private use of patrons those articles in this volume that carry a code at the bottom of the first page, provided the per-copy fee indicated is paid through the Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923. Instructors are permitted to photocopy isolated articles for non-commercial classroom use without any fee. For other copying, reprint or republication permission, write to: IEEE Copyrights Manager, IEEE Service Center, 445 Hoes Lane, P.O. Box 1331, Piscataway, NJ 08855-1331. All rights reserved. Copyright © 1994 by the Institute of Electrical and Electronics Engineers.

Additional copies may be ordered from:

IEEE Order Department 445 Hoes Lane Piscataway, NJ 08854

IEEE Catalog Number: 94CH35709

ISBN: 0-7803-2117-0

Library of Congress: 94-78759

# Welcome to the 1994 Bipolar/BiCMOS Circuits & Technology Meeting

The remarkable progress made in Bipolar/BiCMOS technologies in the early part of the nineties, an age emerging with a major accent on low power, nomadic, information super processing, is both fascinating and challenging. In the midst of vigorous challenge from CMOS, the bipolar/BiCMOS technologies are marching ahead with commercial launching of Multi-Gigabits/s Bipolar Gate Arrays and complex BiCMOS microprocessors at blazing speed, not to mention the impressive analog products and 200mm wafer SiGe technologies. Entering the ninth year, the 1994 BCTM continues to serve as a primary forum for discussing the advances made in the area of bipolar/BiCMOS technologies.

This year's program begins with a keynote address by David Fullagar of Maxim, entitled "The Future of Bipolar in Analog ICs." He will talk about a second renaissance of analog bipolar ICs in the offing and the interesting challenges and opportunities ahead. At Monday's luncheon talk, John Shier of VTC will present the intricate interdisciplinary nature of complexities and challenges of disk drives, a \$25billion/year market.

The double-length invited tutorial/review paper sessions continue to be a popular feature of this conference. We have five interesting invited tutorial/review papers to be presented by leading experts. John Prince of the University of Arizona will present a talk on modeling of interconnects. The issues in the design by simulation as applicable to BiCMOS will be discussed by Jeffrey Frey of the University of Maryland. Greg Taylor on Intel will present circuit techniques for high fan-in, dynamic BiNMOS gates and its application in the 90 MHz and higher speed microprocessors. Analog BiCMOS circuit design techniques are discussed by Sone and Yatsuyanagi of NEC. Where Silicon-Germanium HBT technology is heading, and its role in the RF to millimeterwave spectrum of frequencies, including the recent work by Bernard Meyerson's group at IBM, will be discussed by Christian Kermarrec of Analog Devices.

There are two exciting evening panel discussions planned for this year. The first one is on Low Power Design, organized by Tom Fletcher of Intel, and the second one, organized by David Harame of IBM and Alan Solheim of BNR, is on, "Is SiGe a Laboratory Curiosity or Something Real?"

Of the total number of abstracts submitted, 55% were accepted for presentation. This year, we received 55% of the abstracts from industry and 45% from universities. The regional distribution of abstracts received is as follows: 52% from the USA and Canada, 26% from Japan and Asia, 20% from Europe and 2% from elsewhere, which includes a paper from New Zealand.

We thank the committee members for their enthusiastic contributions and strongly encourage your active participation in this years BCTM.

C. (Selva) R. Selvakumar (Program Chairman) & John Shier (General Chairman)

### 1994 BCTM Executive Committee

John Shier General Chairman VTC, Inc. Bloomington, MN

C. R. Selvakumar Program Chairman University of Waterloo Waterloo, Ontario

Krishna Shenai Vice-Chairman University of Wisconsin Madison, WI

**Tad Yamaguchi** Incoming Vice-Chairman MAXIM, Inc. Beaverton, OR Doug Verret

Past Chairman

Texas Instruments

Houston, TX

Jon Schieltz Finance Chairman MAXIM, Inc. Beaverton, OR

**Tom Fletcher**Subcommittee Chairman

Intel Corp.

Hillsboro, OR

Ron Knepper Subcommittee Chairman Stanford University Stanford, CA Jerold Seitchik Subcommittee Chairman Texas Instruments Dallas, TX

Alan Solheim Subcommittee Chairman Bell Northern Research Ottawa, Ontario

John Shott Subcommittee Chairman Stanford University Stanford, CA

Row 1: K. Joardar, P. Davis, R. Pease, J. Seitchik. Row 2: P. van Wijnen, K. Shenai, J. Shier, J. Jopke, C. Selvakumar, T. Yamaguchi. Row 3: M. Nakamae, K. O, B. Davis, T. Brown, A. Barish, D. Harame, S. J. Prasad, R. Knepper, R.-H. Yan, J. Shott, T. Long, H. Iwai. Row 4: A. Solheim, T. Fletcher, D. Bowers, M. Law, S. Robins, R. Schrimpf, C. McAndrew

### SUBCOMMITTEE ON CAD/MODELING

Ronald Knepper, Chairman Stanford University Stanford, CA

H. J. Chen Honeywell Plymouth, MN

Motorola

Mesa, AZ

meywell AT&T mouth, MN Allentown, PA

S. J. Prasad Tektronix Beaverton, OR

Mark Lundstrom Purdue University West Lafayette, IN

Kuntal Joardar

Shaun Simpkins MAXIM, Inc. Beaverton, OR

Colin McAndrew

Paul van Wijnen Intel Santa Clara, CA

### SUBCOMMITTEE ON ANALOG DESIGN

Alan Solheim, Chairman Bell Northern Research Ottawa, Ontario

**Derek Bowers** Analog Devices Sunnyvale, CA

Sunnyvale, CA

Bill Davis

Bill Davis Motorola, Inc. Tempe, AZ Paul Davis AT&T Bell Labs Reading, PA

Mike Koen Burr-Brown Tucson, AZ Robert Pease National Semiconductor

Santa Clara, CA

### SUBCOMMITTEE ON DIGITAL DESIGN

Tom Fletcher, Chairman Intel Hillsboro, OR

**Arnold Barish**IBM

Poughkeepsie, NY

Tony Brown Northern Telecom Nepean, Ontario **Dan Hopta**Digital Equipment Corp.

Marlboro, MA

Craig Lage Motorola Austin, TX Prasad Raje Hewlett-Packard Palo Alto, CA

### SUBCOMMITTEE ON DEVICE PHYSICS

Jerold Seitchik, Chairman Texas Instruments Dallas, TX

David Harame IBM

Yorktown Heights, NY

Paul Kempf Northern Telecom Nepean, Ontario Mark Law Univ. of Florida Gainesville,

Rafael Reif

Cambridge, MA

**David Roulston** Univ. of Waterloo Waterloo, Ontario

Ron Schrimpf Univ. of Arizona Tuscon, AZ

### SUBCOMMITTEE ON PROCESS/TECHNOLOGY

John Shott, Chairman Stanford University Stanford, CA

Helmut Klose Siemens AG Munich, Germany

Hiroshi Iwai Toshiba Corp. Kawasaki, Japan

Tom Long AT&T Microelectronics Allentown, PA **Bob Lutze** Brooktree San Diego, CA

**Masahiko Nakamae** NEC Kanagawa, Japan

Kenneth O Analog Devices Wilmington, MA Scott Robins

Cypress Semiconductor

San Jose, CA

**Doug Verret**Texas Instruments

Houston, TX

**Tad Yamaguchi** MAXIM, Inc. Beaverton, OR

### **EDITORIAL COORDINATION**

Janice Jopke CCS Associates

### **PUBLICATIONS AND PUBLICITY**

John Shier VTC, Inc. Janice Jopke CCS Associates

### 1994 BCTM SCHEDULE AT A GLANCE

| 1994 BCTM SCHEDULE AT A GLANCE                                          |                                                |                                                    |                                                       |                           |  |  |  |

|-------------------------------------------------------------------------|------------------------------------------------|----------------------------------------------------|-------------------------------------------------------|---------------------------|--|--|--|

| SUNDAY - OCTOBER 9 Registration & Social Hour - Ballroom 1 - 7:00 PM    |                                                |                                                    |                                                       |                           |  |  |  |

| MONDAY - OCTOBER 10 Registration opens at 7:30 AM in the Ballroom Foyer |                                                |                                                    |                                                       |                           |  |  |  |

| Opening Rei<br>Annoucem                                                 | 8:30 AM                                        |                                                    |                                                       |                           |  |  |  |

| KEYNOTE :<br>Analog ICs                                                 | 8:45 AM                                        |                                                    |                                                       |                           |  |  |  |

| 20 Minute Bre                                                           | eak: Coffe                                     | e & Roll                                           | s in the Foyer                                        | 9:30 - 9:50 AM            |  |  |  |

| I. Analog 1<br>Ballroom 3                                               | II. High Perfor-<br>mance BiCMOS<br>Ballroom 4 |                                                    | III. I.C.<br>Modeling<br>Fifth Season                 | 9:50 AM - Noon            |  |  |  |

| "A Fa                                                                   | 12:00 PM                                       |                                                    |                                                       |                           |  |  |  |

| IV. IC Bipolar<br>Transistor<br>Technology<br>Ballroom 3                | VI. High-Speed<br>Digital<br>Ballroom 4        |                                                    | VIII. Power<br>and Thermal<br>Effects<br>Fifth Season | 1:45 - 3:25 PM            |  |  |  |

| V. Analog<br>BiCMOS<br>Ballroom 3                                       | VII: High Per-<br>formance ECL<br>Ballroom 4   |                                                    | IX. Charac-<br>terization<br>Ballroom 1               | 3:35 PM -<br>4:50/5:15 PM |  |  |  |

| Author                                                                  | Interview                                      | s Imme                                             | diately After S                                       | Sessions                  |  |  |  |

|                                                                         |                                                | DINNER E                                           | BREAK                                                 |                           |  |  |  |

| Low Power Design oratory                                                |                                                | 3 - SiGe: Lab-<br>Curiosity or<br>ing Real?<br>m 4 | 8:00 PM                                               |                           |  |  |  |

| TUESDAY - OCTOBER 11                                                    |                                                |                                                    |                                                       |                           |  |  |  |

| X. Analog II<br>Ballroom 2                                              | XII. Device<br>Simulation<br>Ballroom 3        |                                                    | XIV. Bipolar<br>Process<br>Integration<br>Ballroom 4  | 8:30 - 10:10 AM           |  |  |  |

| XI. Analog III<br>Ballroom 2                                            | XIII. Stress &<br>Reliability<br>Ballroom 3    |                                                    | XV. Process<br>Integration<br>Issues<br>Ballroom 4    | 10:20 AM - Noon           |  |  |  |

| Author Interviews Immediately After Sessions                            |                                                |                                                    |                                                       |                           |  |  |  |

### TABLE OF CONTENTS

| Welcome and Announcements Monday, October 10, 8:00 AM Ballrooms 1 & 2 John Shier, VTC, General Chairman C. R. Selvakumar, University of Waterloo, Program Chairman                                  |    |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|

| Keynote Address<br>David Fullagar, Maxim                                                                                                                                                            |    |    |

| Session I: ANALOG 1 Monday, October 10, BALLROOM 3 Co-chairs: Robert Pease (National), Derek Bowers (Analog Devices)                                                                                |    |    |

| 9:50 AM 1.1 A 14-b 2.5 MSPS Pipelined ADC with On-Chip EPROM, D. Mercer (Analog Devices)                                                                                                            | p. | 15 |

| 10:15 AM 1.2 A Fast Low-Power Voltage-Feedback Opamp with 40 V Complementary Bipolar Technology, F. Moraveji (National)                                                                             | p. | 19 |

| <ul> <li>10:40 AM</li> <li>1.3 A 6.8 mA Closed-Loop Monolithic Buffer with 120 MHz bandwidth, 4000 V/μs Slewing, and ±12 V Signal Compatibility, D. Bowers (Analog Devices)</li> </ul>              | p. | 23 |

| 1.4 WITHDRAWN                                                                                                                                                                                       |    |    |

| Session II: HIGH-PERFORMANCE BICMOS Monday, October 10, 9:50 AM Ballroom 4 Co-chairs: Tom Fletcher (Intel), Prasad Raje (HP)                                                                        |    |    |

| 9:50 AM<br>2.1 <b>High Fan-in Circuit Design (invited tutorial)</b> , Greg Taylor and Larry Clark (Intel)                                                                                           | p. | 27 |

| <ul> <li>10:40 AM</li> <li>2.2 A Novel Sub-2.0 V BiCMOS Logic Circuit with a BiCMOS Charge Pump,<br/>H. Okamura, T. Atsumo, K. Takeda, M. Takada, K. Imai, Y. Kinoshita, and T. Yamazaki</li> </ul> | p. | 33 |

| <ul> <li>11:05 AM</li> <li>2.3 A 1.1 V Bootstrapped Bipolar CMOS (B<sup>2</sup>CMOS) Logic Gate, S. Embabi and K. Islam (Texas A&amp;M) and A. Bellaour (CDTA Algiers)</li> </ul>                   | p. | 37 |

A 4.5 ns BiCMOS 22V10 PAL, S. Wong, D. Yu, R. Bettmann, S. Pai, Y. Koh, D. Wong, J. Kleine, and F. Jenné (Cypress)

p. 41

11:30 AM

2.4

Monday, October 10, Fifth Season Co-chairs: Jerry Seitchik (TI), Kuntal Joardar (Motorola) 9:50 AM 3.1 A Quasi-Static Approach to Modeling Emitter Stored Charge in the Highp. 44 Frequency Small-Signal A.C. Response of BJTs, J. S. Hamel (Univ. of Canterbury) 10:15 AM Advanced Modeling of Distortion in Bipolar Transistors Using the 3.2 p. 48 MEXTRAM Model, L. de Vreede, H. de Graaff, K. Mouthaan, M. de Kok, J. Tauritz, and R. Baets (Delft Univ. of Technology) 10:40 AM 3.3 Modeling and Simulation of Package and Interconnects (invited tutorial), p. 52 John Prince (Univ. of Arizona) 11:30 AM Analysis of a Si BJT Scaling Scheme for Low-Noise and Low-Power 3.4 p. 60 Analog Applications, N. Itoh, Y. Yoshida, S. Watanabe, Y. Katsumata, and H. Iwai (Toshiba) Session IV: I.C. BIPOLAR TRANSISTOR TECHNOLOGY Monday, October 10, Ballroom 3 Co-chairs: Masahiko Nakamae (NEC), John Shott (Stanford) 1:45 PM A High-Speed Bipolar Transistor Using a 2-Step Epitaxial Base 4.1 p. 64 Technology, K. Yamano, H. Fujimaki, H. Yokouchi, K. Ohshima, and K. Suzuki (Oki) 2:10 PM A Single-Crystal Silicon-Contacted Double Self-Aligned BJT using 4.2 p. 68 Selective Epitaxy, C. Subramanian and G. Neudeck (Purdue) 2:35 PM Comparison of Polysilicon and Silicon-Carbon Emitters with Enhanced 4.3 p. 72 Emitter Efficiency, C. Emons, R. Koster, D. Paxman, and M. Theunissen (Philips) 3:00 PM Advanced Process Technology for a 40 GHz fT Self-Aligned Bipolar LSIs, 4.4 p. 76 T. Hashimoto, Y. Tamaki, S. Satoh, and T. Shiba (Hitachi) Session V: ANALOG BICMOS Monday, October 10, Ballroom 3 Co-chairs: Derek Bowers (Analog Devices), Bob Pease (National) 3:35 PM Design Techniques for Analog BiCMOS Circuits (invited tutorial), Kazuya Sone 5.1 p. 80 and Michio Yotsuyanagi (NEC) 4:25 PM Fully Analog LMS Adaptive Notch Filter in BiCMOS Technology, T. Linder 5.2 p. 87 and H. Sojer (Siemens)

Session III: I.C. MODELING

| Session VI: HIGH-SPEED DIGITAL Monday, October 10, Ballroom 4 Co-chairs: Tony Brown (Northern Telecom), Dan Hopta (DEC)                                                                            |        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| <ul> <li>1:45 PM</li> <li>6.1 A 1.3-ns 32-Word by 32-Bit Three-Port BiCMOS Register File,<br/>Chin-Chieh Chao and Bruce A. Wooley (Stanford Univ.)</li> </ul>                                      | p. 91  |

| <ul> <li>2:10 PM</li> <li>6.2 A Subnanosecond 64 kb BiCMOS SRAM, M. Santoro, L. Tavrow, and G. Bewick (Sun Microsystems)</li> </ul>                                                                | p. 95  |

| <ul> <li>2:35 PM</li> <li>6.3 Voltage Scalable GHz Interface Circuits for BiCMOS Applications,</li> <li>H. Chang, K. Fung, M. Izzard, and D. Scott (Texas Inst.)</li> </ul>                        | p. 99  |

| 3:00 PM 6.4 A Silicon Bipolar 14 Gb/s 1:4 Demultiplexer IC and its System Requirements, Z. Lao, U. Langemann, and J. Albers (Ruhr-Univ., Germany)                                                  | p. 103 |

| Session VII: HIGH-PERFORMANCE ECL Monday, October 10, Ballroom 4 Co-chairs: Arnold Barrish (IBM), Craig Lage (Motorola)                                                                            |        |

| <ul> <li>3:35 PM</li> <li>7.1 An ECL Gate with Improved Speed and Low Power in a BiFET Process,</li> <li>V. Oklobdzija (Univ. Calif. Davis)</li> </ul>                                             | p. 107 |

| 4:00 PM 7.2 A Fully-Compensated APD Circuit with 10:1 Ratio Between Active and Inactive Current, N. Jouppi (DEC)                                                                                   | p. 111 |

| 4:25 PM 7.3 A Fully Compensated Active Pull-Down ECL Circuit with Self-Adjusting Driving Capability, K. Ueda, N. Sasaki, H. Sato, and K. Mashiko (Mitsubishi)                                      | p. 115 |

| <ul> <li>4:50 PM</li> <li>7.4 A Speed, Power, and Supply Noise Evaluation of ECL Driver Circuits,</li> <li>N. Jouppi (DEC), S. Sidoropoulos (Stanford), and S. Menon (DynaLogic)</li> </ul>        | p. 119 |

| Session VIII: POWER AND THERMAL EFFECTS Monday, October 10, Fifth Season (6th FLOOR) Co-chairs: Ron Schrimpf (U. of Arizona), Colin McAndew (AT&T)                                                 |        |

| 1:45 PM 8.1 Chip-Level Electrothermal Simulation of BJT Circuits, S. Moinian, P.Feldmann, and R. Melville (AT&T)                                                                                   | p. 123 |

| 2:10 PM 8.2 Thermally Induced Current Constriction in III-V Heterojunction BJTs, E. Koenig and U. Seiler (Daimler-Benz) and J. Schneider and U. Erben (Univ. of Ulm)                               | p. 127 |

| 2:35 PM 8.3 Measurements and Simulations of Breakdown Phenomena in a Voltage Scalable Smart Power Complementary BiCMOS Process, R. Ryter, R. Zingg, and W. Fichtner (Swiss Fed. Inst. of Technol.) | p. 131 |

| 3:00 PM  8.4 The Effect of the Bipolar Transistor in the Switching Dynamics of IBGTs in Resonant Converter Applications, I. Widjaja, A. Kurnia, D. Divan, and K. Shenai (Univ. Wisconsin)        | p. | 135 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

| Session IX: CHARACTERIZATION  Monday, October 10, Ballroom 1  Co-chairs: Paul van Wijnen (Intel), S. J. Prasad (Tektronix)                                                                       |    |     |

| <ul> <li>3:35 PM</li> <li>9.1 A New Approach for Extracting Base Width Modulation Parameters for Bipolar Transistors, K. Joardar (Motorola)</li> </ul>                                           | p. | 140 |

| 4:00 PM<br>9.2 SPICE Early Modeling, C. McAndrew and L. Nagel (AT&T)                                                                                                                             | p. | 144 |

| <ul> <li>4:25 PM</li> <li>9.3 Accuracy of Series Resistance Extraction Schemes for Polysilicon BJTs, E. Dubois, PH. Bricout, and E. Robilliart (IEMN/ISEN)</li> </ul>                            | p. | 148 |

| PANEL DISCUSSION A - LOW POWER DESIGN<br>Monday, October 10, Ballroom 3                                                                                                                          | p. | 153 |

| PANEL DISCUSSION B - IS SIGE A LABORATORY CURIOSITY OR SOMETHING REAL? Monday, October 10, Ballroom 4                                                                                            | p. | 153 |

| Session X: ANALOG II. TUesday, October 11, BALLROOM 2 Co-chairs: Allen Solheim (BNR), Paul Davis (AT&T)                                                                                          |    |     |

| 8:30 AM 10.1 SiGe HBTs Reach the Microwave and Millimeter-Wave Frontier (invited tutorial), C. Kermerrec, G. Dawe, T. Tewksbury, B. Meyerson, D. Harame, and M. Gilbert (IBM and Analog Devices) | p. | 155 |

| 9:20 AM  10.2 Design and Realization of Low-Noise High-Gain Si Bipolar  Transimpedance Preamplifiers for 10 Gb/s Optical Fiber Links, M.  Neuhäuser, HM. Rein, and H. Wernz (Ruhr Univ., Bochum) | p. | 163 |

| <ul> <li>9:45 AM</li> <li>10.3 SiGe Bipolar ICs for a 20 Gb/s Optical Transmitter, T. Hashimoto, F. Sato, M. Soda, H. Tezuka, T. Suzuki, T. Tatsumi, and T. Tashiro (NEC)</li> </ul>             | p. | 167 |

| Session XI: ANALOG III. Tuesday, October 11, BALLROOM 2 Co-chairs: Paul Davis (AT&T), Allen Solheim (BNR)                                                                                        |    |     |

|                                                                                                                                                                                                  |    |     |

| <ul> <li>10:45 AM</li> <li>11.2 A 2.7 V 800 MHz 2.1 GHz Transceiver Chipset for Mobile Radio Applications in 25 GHz f<sub>T</sub> Si Bipolar, W. Veit, J. Fenk, S. Ganser, K. Hadjizada, S. Heinen, H. Herrmann, and P. Sehrig (Siemens)</li> </ul>   | p. 175 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| <ul> <li>11:10 AM</li> <li>11.3 High Q Inductors for Wireless Applications in a Complementary Silicon Bipolar Process, K. Ashby, I. Koullias, W. Finley, J. Bastek, and S. Moinian (AT&amp;T)</li> </ul>                                              | p. 179 |

| <ul> <li>11:35 AM</li> <li>11.4 An Adjustment-Free Single-Chip Video Signal Processing LSI Chip for VHS VCRs, N. Yamamoto, O. Nakagawa, K. Takebuti, K. Kinjyo, Y. Kitamura, S. Mori, Sasaki, and H. Hori (Hitachi)</li> </ul>                        | p. 183 |

| Tuesday, October 11, BALLROOM 3 Session XII: DEVICE SIMULATION. Co-chairs: Ron Knepper (IBM), Mark Lundstrom (Purdue)                                                                                                                                 |        |

| 8:30 AM 12.1 The Importance of Including Lattice Self-Heating and Hot-Carrier Transport in BJT Simulation, M. Liang and M. Law (Univ. of Florida)                                                                                                     | p. 187 |

| 8:55 AM  12.2 A Physically-Based Model for Carrier Freeze-Out in Si and SiGe BJTs Suitable for Device Simulators, M. Shaheed and C. Maziar (Univ. of Texas, Austin)                                                                                   | p. 191 |

| 9:20 AM 12.3 Design of BiCMOS Technology by Simulation, (invited tutorial), Jeffrey Frey (Univ. of Maryland) - No manuscript available for publication                                                                                                | p. 195 |

| Session XIII STRESS AND RELIABILITY Tuesday, October 11, BALLROOM 3 Co-chairs: Mark Law (Univ. Fla.), David Harame (IBM)                                                                                                                              |        |

| <ul> <li>10:20 AM</li> <li>13.1 BiCMOS h<sub>fe</sub> Degradation: Causes and Circuit Solution, C. McAndrew,</li> <li>I. Kizilyalli, and J. Bude (AT&amp;T)</li> </ul>                                                                                | p. 197 |

| <ul> <li>10:45 AM</li> <li>13.2 Excess Collector Current Due to an Oxide-Trapped Charge-Induced Emitter in Irradiated NPN BJTs, A. Wei, S. Kosier, R. Schrimpf, M. Delaus, and W. Combs (Univ. of Arizona, Analog Devices, and U. S. Navy)</li> </ul> | p. 201 |

| <ul> <li>11:10 AM</li> <li>13.3 A Simple Technique for Improving the Hot-Carrier Reliability of Single-Poly BJTs, S. Kosier, A. Wei, R. Schrimpf, M. DeLaus, and A. Martinez (Univ. of Arizona and Analog Devices)</li> </ul>                         | p. 205 |

| - ,                                                                                                                                                                                                                                                   |        |

# Session XIV: BIPOLAR PROCESS INTEGRATION Tuesday, October 11, BALLROOM 4 Co-chairs: Tom Long (AT&T), Tad Yamaguchi (Maxim)

| <ul> <li>8:30 AM</li> <li>14.1 0.5 μm Silicon Bipolar Transistor Technology for Analog Applications,</li> <li>H. Nakajima, N. Itoh, K. Inou, T. Iinuma, S. Matsuda, C. Yoshino, Y. Katsumata, and</li> <li>H. Iwai (Toshiba)</li> </ul>                                  | p. 213 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 8:55 AM  14.2 A 52 GHz Epitaxial-Base BJT with a 26.5 V Early Voltage, a Box-Like Base, and a Retrograde Collector, K. Inou, S. Matsuda, N. Sugiyama, K. Usuda, S. Imai, Y. Kawaguchi, K. Yamada, Y. Katsumata, and H. Iwai (Toshiba)                                    | p. 217 |

| <ul> <li>9:20 AM</li> <li>14.3 A Double Polysilicon Self-Aligned BJT Process (ADRF) with Optional NMOS Transistors for RF and Microwave Applications, K. O, P. Garone, C. Tsai, B. Scharf, M. Higgins, D. Mai, C. Kermarrec, and J. Yasaitis (Analog Devices)</li> </ul> | p. 221 |

| <ul> <li>9:45 AM</li> <li>14.4 A 40 V Si Complementary Bipolar Technology for High-Precision and High-Frequency Analog Circuits, R. Bashir, J. DeSantis, D. Chen, F. Hébert, A. Ramde, P. Maghsoudnia, H. You, P. Meng, F. Moraveji, and R. Razouk (National)</li> </ul> | p. 225 |

| Session XV: PROCESS INTEGRATION ISSUES Tuesday, October 11, BALLROOM 4 Co-chairs: Hiroshi Iwai (Toshiba), Scott Robins (Cypress)                                                                                                                                         |        |

| <ul> <li>10:20 AM</li> <li>15.1 Process Integration Technology for Low Process Complexity BiCMOS using Trench Collector Sink, H. Yoshida, H. Suzuki, Y. Kinoshita, K. Imai, T. Akimoto, K. Tokashiki, and T. Yamazaki (NEC)</li> </ul>                                   | p. 230 |

| 10:45 AM 15.2 Single-Poly BiCMOS Technology with 30 GHz Bipolar f <sub>T</sub> , C. Wang and J. van der Velden (Philips)                                                                                                                                                 | p. 234 |

| <ul> <li>11:10 AM</li> <li>15:3 A High-Performance CBiCMOS with Novel Self-Aligned Vertical PNP Transistors, T. Ikeda, T. Nakajima, S. Kubo, H. Jouba, and M. Yamawaki (Mitsubishi)</li> </ul>                                                                           | p. 238 |

| <ul> <li>11:35 AM</li> <li>15.4 Influence of Back-End Thermal Processing on Polysilicon-Monosilicon Contact Resistance Due to Dopant Deactivation, A. Perera, W. Taylor, and M. Orlowski (Motorola)</li> </ul>                                                           | p. 242 |

| Author Index                                                                                                                                                                                                                                                             | p. 247 |

### A 14-b 2.5 MSPS Pipelined ADC With On Chip EPROM

Douglas A. Mercer

Analog Devices Semiconductor

181 Ballardvale Street Wilmington, MA 01887

### **ABSTRACT**

A 14-b 2.5-MSPS, multi-stage pipeline, subranging analog-to-digital converter is presented. In addition to conventional laser-wafer-trim, on chip, "write once" EPROM is used to calibrate inter-stage gain errors at package sort. Integral nonlinearity errors as small as +/- 2LSB, and differential nonlinearity errors of -0.6, +0.8 LSB have been achieved. The 5.4 mm by 4.4 mm device includes a 2.5-V reference is built on a 2-um 10-V BiCMOS process and consumes 550 mW of power.

### Introduction

Applications such as high end still imaging (CCD and PMT) systems and high data rate digital communications over twisted pair (ADSL) require converters with dynamic range higher than 12 bits. Also the conversion rates required are beyond what presently available monolithic converters with more than 12 bits offer. High resolution, high sample rate converters have been reported. A 15-b ADC [1] samples only up to 1 MSPS, lacks much of the digital calibration circuitry and consumes 1.8 watts. A 2.5 MSPS ADC [2] has only 13 bit resolution. Other 14-b converters with conversion rates greater than 1 MSPS are available as multi-chip hybrids. These converters are in relatively large packages and can consume more than 2 watts of power.

A monolithic 14-b 2.5 MSPS ADC, with a fast acquisition time of less than 200 nSeconds combined with 110 uV rms total noise, has been developed on a 2 micron 10 V BiCMOS process. The converter dissipates only 550 mW from +/- 5 volt power supplies and is packaged in a 44 pin PLCC package. The process includes laser trimmable thin film resistors, double poly capacitors in addition to 2 GHz ft NPN devices and 2 micron CMOS. The double poly feature has been used to fabricate a simple floating gate NMOS "write once" EPROM structure. The EPROM calibration is used to insure linearity at the 14-b level after packaging.

### **Functional Description**

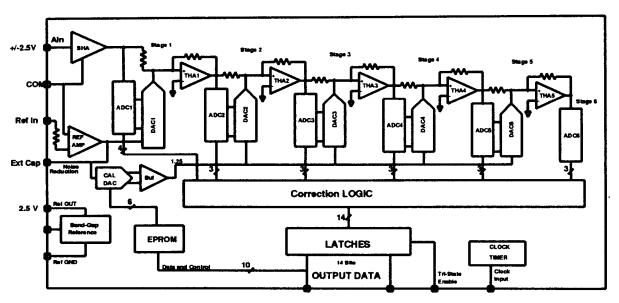

The design (block diagram shown in figure 1) extends and integrates proven circuit techniques to provide a complete monolithic converter function. A low noise, self-correcting, frontend sample-hold amplifier from [3] has been extended to improve settling time from 12 bits in 250 nSeconds to 14 bits in less than 200 nSeconds and to lower its noise below 80 uV rms for use in this 14-b ADC. The converter is a multi-stage pipeline design with 5 stages of Flash/DAC/SHA and a final 6th Flash. The flash resolution for the stages is 4-3-3-3-3. One bit of overlap between

stages is used for error correction. The choice of the number of bits to use in first stage is based on matching requirements for 14 bit linearity. The advantages of a less complex design are possible if all the stages in the pipeline are the same number of bits. With 4 bits in the first stage, only way to end up with 14 bits after digital error correction is to have all the rest of the stages be 3 bits per stage.

To economize on power, only the frontend SHA, first flash and DAC, where the highest dynamic range is needed, use the full +/- 5 volt power supplies. The second SHA (which is in stage1) and stages 2-6 operate from only the +5 analog power supply. The DACs and SHAs in these single supply stages are based on a high speed low power design presented in [4]. The total power has a design center of just over 500 mW at room temperature. About 1/2 of the total power is used in the frontend SHA and first stage Flash/DAC/SHA.

### **Lowering The Input Noise**

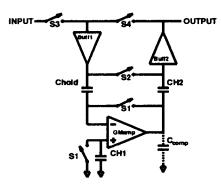

The input SHA is based on an architecture from [3]. The block diagram of the SHA is shown in figure 2. In a SHA there are two modes of operation, sampling the input and holding a sample on the output. The wide band noise seen in the output is the combination of the noise present across the hold capacitor at the moment of sampling and the noise present while in hold mode. The former of these two is often the largest contributor. The designer must identify the important noise sources to tackle problem.

To understand the performance of this circuit the following is a quick look at its operation as it impacts the noise. When sampling the input, switches S1, S2 and S3 are closed with S4 open. Because S1 is closed around amplifier GMamp, the bottom of capacitor Chold is held at a virtual ground. The top of Chold is driven to the input by buffer Buff1 through switch S3. The major contributors to the noise across Chold in this mode are Buff1 as it drives the top and GMamp which is driving the bottom. The noise contribution from the on resistance of the switches can be made low enough by sizing as not to be significant, and Buff2 is not in the signal path.

These two amplifier stages must be designed to optimize the trade-off between noise and signal bandwidth. It is desirable to have Buff1 be as wide band as possible for two reasons, fast acquisition of the input and stability while in hold mode. However, wide bandwidth also contributes more noise. The same is true of the amplifier GMamp. A significant portion of the power is used in this SHA to provide both low noise and wide bandwidth and fast settling time. The noise was reduced from 170uV in [3] to 80uV.

Figure 1 Block Diagram

Figure 2 Sample and Hold Amplifier

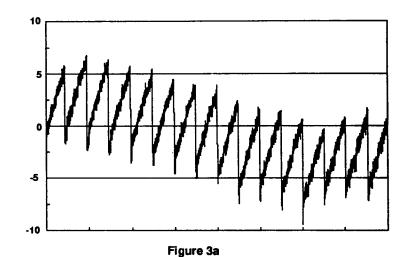

INL with Inter-stage gain error 1.5

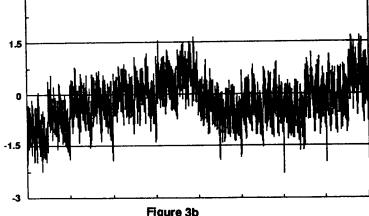

Figure 3b INL After Inter-stage gain calibration