# The 13th Annual IEEE/SEMI® Advanced Semiconductor Manufacturing Conference

Advancing the Science and Technology of Semiconductor Manufacturing

# **ASMC 2002**

Advanced Semiconductor

Manufacturing Conference and Workshop

April 30-May 2 Seaport Hotel Boston, MA USA

Advanced Metrology

Advanced BEOL Processing

Advanced FEOL

Contamination Free Manufacturing

Cost Management Methodologies

Defect Free Manufacturing

Fab Dynamics

Process Control Methodology

Resource Productivity Management

Yield Modeling, Analysis and Enhancement

Yield Enhancement Tools and Methods

Sponsored by:

Produced by:

#### TABLE OF CONTENTS

## **Advanced FEOL Processing**

| Invited: In-Line Electrical Characterization Of Ultrathin Gate Dielectric Films  Florence Cubaynes, <i>Philips Research Leuven</i> ; Sophie Passefort, Kwame Eason, Xiafang Zhang, <i>KLA-Tencor Corporation</i> ; Lucien Date, Didier Pique, <i>Applied Materials</i> ; Thierry Conard, Aude Rothschild, Marc Schaekers, <i>IMEC Leuven, Belgium</i> | 1  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Alternative Smart-cut-like Process for Ultra-thin SOI Fabrication W.N. Carr, and B. Chen, Silicon Wafer Technologies; A.Y. Usenko, New Jersey Institute of Technology, Yves Chabal, Agere Systems                                                                                                                                                     | 6  |

| A Manufacturable Shallow Trench Isolation Process for Sub-0.2um DRAM Technologies W.Y. Lien, W.G. Yeh, C.H. Li, K. C.Tu, I. H. Chang, H.C. Chu, W.R. Liaw, H.F. Lee, H.M. Chou, C.Y. Chen, M. H. Chi, Taiwan Semiconductor Manufacturing Company, Ltd.                                                                                                | 11 |

| Controlling Lithographic Imaging Performance at Sub-100 nm CD with Optical Measurements I. Grodnensky, S. Enayati, J. Manka, S. Mizutani, S. Slonaker, Nikon Precision Inc.                                                                                                                                                                           | 17 |

| A Robust Shallow Trench Isolation (STI) with SiN Pull-Back Process for Advanced DRAM Technology C.H. Li, K.C. Tu, H.C. Chu, I.H. Chang, W.R. Liaw, H.F. Lee, W.Y. Lien, M.H. Tsai, W.J. Liang, W.G. Yeh, H. M. Chou, C.Y. Chen, M. H. Chi, R&D, Taiwan Semiconductor Manufacturing Company, Ltd.                                                      | 21 |

| Flexible Polishing Surface (FPS) vs Rigid Polishing Surface (RPS) in CMP: Pros and Cons<br>Yehiel Gotkis, David Wei and Rodney Kistler, LAM Research Corporation                                                                                                                                                                                      | 27 |

| Fab Dynamics                                                                                                                                                                                                                                                                                                                                          |    |

| Invited: A Simulation of Periodical Priority Dispatching of WIP for Product-mix Fabrication Kazuyuki Saito and Sumika Arima, <i>The University of Aizu</i>                                                                                                                                                                                            | 33 |

| Characterization of Film Uniformity in LPCVD TEOS Vertical Furnace Shirley Ekbundit, Motorola MOS12; Brian Izzio, Axcelis Technologies                                                                                                                                                                                                                | 38 |

| Fulfilling the Speed Imperative: New Product Development and Enterprise Project Management in the New Economy Raimond E. Immelman, <i>The TOC Center Inc.</i>                                                                                                                                                                                         | 43 |

| Distributed WIP Control in Advanced Semiconductor Manufacturing Robin Qui, Penn State Great Valley; Richard Burda, IBM Microelectronics; Robert Chylak, Kulicke & Soffa Industries                                                                                                                                                                    | 49 |

| Dynamic Deployment Modeling Tool for Photolithography WIP Management Dennis Williams and David Faver, IBM Microelectronics                                                                                                                                                                                                                            | 55 |

| Automated System Infrastructure to Facilitate Design of Experiments (DOE) Data Analysis Navin Tandon and Gurshaman Baweja, Texas Instruments, Inc.                                                                                                                                                                                                    | 59 |

| Yield Enhancement Tools and Methods                                                                                                                                                                                                                                                                                                                   |    |

| Invited: Wafer Back Side Applications for Yield Protection and Enhancement Lesley A. Cheema, Leonard J. Olmer, Oliver D. Patterson, Agere Systems; Susan S. Lopez, Mark B. Burns, KLA-Tencor Corp.                                                                                                                                                    | 64 |

| Methodology for Targeted Defect Reduction and Inspection Optimization  Andy Skumanich and Elmira Ryabova, Applied Materials                                                                                                                                                                                                                           | 72 |

| A Statistical Method for Reducing Systematic Defects in the Initial Stages of Production Kazunori Nemoto, Shuji Ikeda, Osamu Yoshida, Shunji Sasabe, Trecenti Technologies, Inc.; Hua Su, KLA-Tencor Corp.                                                                                                                                            | 77 |

| Yield Prediction Using Critical Area Analysis with Inline Defect Data Carl Zhou, Ron Ross, Carl Vickery, Brian Metteer, Steve Gross, Doug Verret, Texas Instruments Inc.                                                                                                                                                                              | 82 |

| Accuracy of Yield Impact Calculation Based on Kill Ratio Makoto Ono and Hisafumi Iwata, PERL, Hitachi Ltd.; Kenji Watanabe, Semiconductor and Integrated Circuits, Hitachi Ltd.                                                                                                                                                                       | 87 |

| Advanced Defect Detection Methods for CMP Process Modules in Semiconductor Manufacturing Peter Stoeckl, AMD Fab 30: Jim Kayanagh, Barry Saville, Thilo Dellwig, KLA-Tencor Corp.                                                                                                                                                                      | 92 |

#### **Process Control Methodology**

| Invited: Advanced Process Control: Benefits For Photolithography Process Control Christopher Gould, Infineon Technologies Richmond                                                                                                                                       | 98             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Advance Process Control Solutions for Semiconductor Manufacturing Moshe Sarfaty, Arulkumar Shanmugasundram, Alexander Schwarm, Joseph Paik, Jimin Zhang, Rong Pan, Martin J Seamons, Howard Li, Raymond Hung, Suketu Parikh, Applied Materials Inc.                      | 101            |

| Shallow Trench Isolation Run-to-Run Control Project at Infineon Technologies Richmond Paul Jowett, Victor Morozov, Infineon Technologies Richmond                                                                                                                        | 107            |

| HandMon-ISPM: Handling Monitoring in a Loading Station of a Furnace Ralph Trunk, Heinz Schmid, Claus Schneider, Lothar Pitzner, Fraunhofer Institute of Integrated Circuits; Heiner Ryssel, University of Erlangen; Henry Bernhardt, Eckhard Marx, Infineon Technologies | 113            |

| Line-profile and Critical Dimension Measurements Using a Normal Incidence Optical Metrology System Weidong Yang, Roger Lowe-Webb, Rahul Korlahalli, Vera Zhuang, Nanometrics Inc., Hiroki Sasano, Wei Liu, David Mui, Applied Materials Inc.                             | 119            |

| Development and Deployment of a Multi-Component Advanced Process Control System for an Epitaxy Tool  James Moyne, Victor Solakhian, and Alexander Yershov, Brooks Automation, Inc.; Malcolm Anderson, Debbie Mockler-Hebert, Fairchild Semiconductor                     | 125<br>or Corp |

| Poster Session                                                                                                                                                                                                                                                           |                |

| BF <sub>2</sub> <sup>+</sup> Implant: A Fluorine Bubble Induced ET Failure Chris J. Viera, Burcay Gurcan, Kendra A. Crocker, Perrin A. Todd, Kenneth M. Lewis, National Semiconductor Corp.                                                                              | 131            |

| Direct Wafer Temperature Measurements for Etch Chamber Diagnostics and Process Control Mei Sun, SensArray Corporation; Calvin Gabriel, Advanced Micro Devices                                                                                                            | 134            |

| Epi Resistivity Profiles Without Wafer Damage Karen Woolford and Christopher Panczyk, SUMCO Phoenix Corp.; Gregory Martel, SemiTest, Inc.                                                                                                                                | 140            |

| Failure Rate and Yield Limiting W-plug Corrosion Diagnosis using Characterization Test Vehicles Xing Tao, Kenneth Reis, Brad Haby, Martin Karnett, Charles Watts, Miguel Delegado, Philips Semiconductors; Kenneth R. Harris, PDF Solutions, Inc.                        | 144            |

| Innovations for Economical 300/450mm IC Fabricators Bevan P.F. Wu, Bevan Wu & Associates                                                                                                                                                                                 | 150            |

| KFAB Decision Site: An Interactive, Exploratory Yield Analysis Framework  Art Flores, Joe Lebowitz, Will Pressnall, Charlie Martin, Texas Instruments, Inc.; C. Bradford Hopper, Spotfire, Inc.                                                                          | 155            |

| Manufacturing Execution System (MES) Operating System Migration to Integrate Leading-Edge Methodologies and Leverage Emerging Techno Brian Best, <i>Dominion Semiconductor</i>                                                                                           | ologies<br>159 |

| A MEMS-Based, High Sensitivity Pressure Sensor for Ultraclean Semiconductor Applications Albert K. Henning, Nicholas Mourlas, Steven Metz, Redwood Microsystems, Inc.; Art Zias, ZiaSense                                                                                | 165            |

| Optimization of Oxide Spacer Etch Process for 0.35 um CMOS Transistor Kenneth M. Lewis, Cindy Daigle, Paul Allard, Dave Tucker, National Semiconductor Corp.                                                                                                             | 169            |

| Plasma Chemical Cleaning of Chip Carrier in a Downstream Hollow Cathode Discharge<br>Günther Nicolussi and Eugen Beck, <i>INFICON Limited</i>                                                                                                                            | 172            |

| Pt/PZT/Pt and Pt/Barrier Stack Etches for MEMS Devices in a Dual Frequency High Density Plasma Reactor P. Werbaneth, J. Almerico, L. Jerde, S. Marks, Tegal Corporation; Bruce Wachtmann, Analog Devices                                                                 | 177            |

| Reduce Scrap: Control Oxide Loss in SC1 Heather Maines, Mark Rathmell, National Semiconductor Corp.: Lydia Veldhuis, National Semiconductor Netherlands                                                                                                                  | 184            |

| Robust Optimization of Experimental Designs in Microelectronics Processes using a Stochastic Approach François Pasqualini, Emmanuelle Josse, STMicroelectronics                                                                                                          | 187            |

| Spelunking in the Data Mine: On Data Mining as an Analysis Tool for the Optimization of Microprocessor Speed Kevin Anderson, Ervin Hill, Alan Mitchell, <i>Intel Corporation</i>                                                                                         | 193            |

| STI Trench Recess Feed Forward Control for Self-Aligned Contact Processes to Reduce PMOS Contact Leakage Burcay Gurcan, Todd Thibeault, Heather Maines, Kenneth Swan, Lisa Moores, <i>National Semiconductor Corp.</i>                                                   | 199            |

| Tool Commonality Analysis for Yield Enhancement George Kong, Motorola - Dan Noble Center                                                                                                                                                                                 | 202            |

| Ultra-dilute Silicon Wafer Clean Chemistry for Fabrication of RF Microwave Devices  Izzy K. Bansal, M/A Com, A Tyco Electronics Company                                                                                                     | 206        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Wafer Level Packaging and 3D Interconnect for IC Technology R. Islam, C. Brubaker, EV Group US Inc.; P. Lindner, C. Schaefer, EV Group                                                                                                      | 212        |

| Keynote: Semiconductor Manufacturing Outlook: Growth When? Where? Why? Bob Johnson, Gartner Dataquest                                                                                                                                       | †          |

| Resource Productivity Management                                                                                                                                                                                                            |            |

| Invited: Equipment Productivity Improvement via Inline Qualification Implementation Neal Lafferty, Rochester Institute of Technology, Bennie Fiol, Paul Jowett, Yuri Karzhavin, Tim Urenda, Infineon Technologies AG                        | 218        |

| Data Acquistion Approach for Real-time Equipment Monitoring and Control Gurshaman Baweja and Bing Ouyang, Texas Instrument, Inc.                                                                                                            | 223        |

| Semiconductor Fab Maintenance Challenge and BKM in Downturn Economy Todd J. Massie, IBM Microelectronics                                                                                                                                    | 228        |

| Development of National Skill Standards for Technicians Working in Highly Automated (300mm) Environments Michael Lesiecki, Maricopa Advanced Technology Education Center; Bob Simington, Intel Corporation                                  | 231        |

| Modeling Staffing Requirements within a Semiconductor Manufacturing Environment Hung-Nan Chen, Motorola, Inc.; Russ Dabbas, Conexant Inc.                                                                                                   | 234        |

| Yield Modeling, Analysis and Enhancement                                                                                                                                                                                                    |            |

| Invited: A Manufacturing Perspective of Physical Design Characterization Daniel N. Maynard, Bette Bergman Reuter, Jon A. Patrick, IBM Microelectronics                                                                                      | 240        |

| Beyond DFM: When Manufacturability has to be Guaranteed by Design David D. Potts, Timwah Luk, Fairchild Semiconductor Corp.                                                                                                                 | 247        |

| Yield/Reliability Enhancement using Automated Minor Layout Modifications Gerard A. Allen, University of Edinburgh                                                                                                                           | 252        |

| Application of Decision Trees for Integrated Circuit Yield Improvement Venkat Raghavan, Agere Systems                                                                                                                                       | 262        |

| Statistical Modeling and Analysis of Wafer Test Fail Counts Hanno Melzner, Infineon Technologies                                                                                                                                            | 266        |

| Defect Free Manufacturing                                                                                                                                                                                                                   |            |

| Invited: Physical Removal of Nano-Scale Defects from Surfaces Ahmed Busnaina, Northeastern University; Hong Lin, IBM Microelectronics                                                                                                       | 272        |

| Planarization Yield Limiters for Wafer-Scale 3D ICs M. Gupta, G. Rajagopalan, C.K. Hong, JQ. Lu, K. Rose, R.J. Gutmann, Rensselaer Polytechnic Institute                                                                                    | 278        |

| An Approach for Improving Yield with Intentional Defects Amy Engbrecht, Rick Jarvis, International SEMATECH (AMD); Abbie Warrick, Lawrence Livermore National Laboratory                                                                    | 284        |

| Transporting FOUPs as a Driver for ESD-Induced EMI Larry B. Levit, Ion Systems; Julian A. Montoya, Intel Corporation                                                                                                                        | 289        |

| An Approach to Recipe Control in Wafer Fab<br>Gurshaman Baweja, Murali Chandrasekaran, Bing Ouyang, Texas Instruments, Inc.                                                                                                                 | 295        |

| Keynote: Achieving the Benefits of 300mm Bruce Sohn, Intel Corporation                                                                                                                                                                      | †          |

| Contamination Free Manufacturing                                                                                                                                                                                                            |            |

| Invited: The Effect of Hafnium or Zirconium Contamination on MOS Processes  B. Vermeire, K. Delbridge, V. Pandit, H.G. Parks, S. Raghavan, University of Arizona; K. Ramkumar, S. Geha, Intel Corporation;  J. Jeon, Advanced Micro Devices | 299        |

| Cleaning of High Aspect Ratio Submicron Trenches Hong Lin, IBM Microelectronics; Ahmed Busnaina, Northeastern University; Ian I. Suni, Clarkson University                                                                                  | 304        |

| Study of Airborne Molecular Contamination in Minienvironments<br>Sheng-Bai Zhu, Asyst Technologies, Inc.                                                                                                                                    | 309        |

| A Model for Outgassing of Organic Contamination from Wafer Carrier Boxes Yu-Min Ho, H.G. Parks, B. Vermeire, The University of Arizona                                                                                                      | 314        |

| † Not available at time printing.<br>IEEE/SEMI Advanced Semiconductor Manufacturing Conference & Workshop 2002                                                                                                                              | Boston, MA |

| Trace Gas Analysis by Diode Laser Cavity Ring-Down Spectroscopy Wen-Bin Yan and Calvin Krusen, Tiger Optics; John Dudek, Kevin Lehmann and Paul Rabinowitz, Princeton University                                                                                | 31  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Cost Management Methodologies                                                                                                                                                                                                                                   |     |

| Yield Learning and the Sources of Profitability in Semiconductor Manufacturing and Process Development Charles Weber, MIT Sloan School of Management                                                                                                            | 324 |

| A Hierarchical Approach to Cost Analysis for Next Generation Semiconductor Processes Raka Sandell and Neal G. Pierce, <i>Motorola – Dan Noble Center</i>                                                                                                        | 330 |

| ABC Modeling: Advanced Features Stephanie Miraglia, Cathy Blouin, Gary Boldman, Shauna Juff, Thomas Richardson, David Yao, IBM Microelectronics                                                                                                                 | 330 |

| Water Usage Reduction in a Semiconductor Fabricator Greg Klusewitz and Jim McVeigh, Fairchild Semiconductor                                                                                                                                                     | 340 |

| Spare Parts Expense Management System David Yao, Cathy Blouin, Mary Cavanaugh, Gary Boldman, Bruce Alvarez, Stephanie Miraglia, Linda Hungerford, IBM Microelectronics                                                                                          | 341 |

| Keynote: Silicon Micromachines for Lightwave Networks: The Little Machines that are Making it BIG!! David J. Bishop, Bell Labs, Lucent Technologies                                                                                                             | †   |

| Advanced BEOL Processing                                                                                                                                                                                                                                        |     |

| Characterization of Copper Voids in Dual Damascene Processes Richard L. Guldi, Judy B. Shaw, Jeffrey Ritchison, Texas Instruments, Inc.; Steve Oestreich, Kara Davis, Robert Fiordalice, KLA-Tencor Corp.                                                       | 351 |

| Manufacturing Implementation of Low-k Dielectrics for Copper Damascene Technology Hartmut Ruelke, Christof Streck, Joerg Hohage, Advanced Micro Devices; Susan Weiher-Telford, Olivier Chretien, Jan Matusche, Applied Materials GmbH                           | 356 |

| Surfacant Behavior and Study in Slurry Bih-Tiao Lin, C.S. Chen, W.K. Yeh, S.N. Peng, Taiwan Semiconductor Manufacturing Corporation, Ltd.                                                                                                                       | 362 |

| Sidewall Clean Effect Upon Titanium Salicide Filaments John P. Campbell, Michelle Boyer, A.J. Griffen, Jr., Zafar Imam, Howard Lee, Clint Montgomery Randy Pak, Brian Vialpondo, Texas Instruments, Inc.                                                        | 368 |

| Supercritical Fluid Processes for Semiconductor Device Fabrication Laura B. Rothman, Raymond J. Robey, Mir K. Ali, David J. Mount; SC Fluids, Inc.                                                                                                              | 372 |

| Opitimization of Resist Strip Recipe for Aluminum Metal Etch Processes Ephraim G. Mammo, Agere Systems; N. Singh, R. C. Mananquil, D. R. Myers, Applied Material, Inc.                                                                                          | 376 |

| Advanced Metrology                                                                                                                                                                                                                                              |     |

| Invited: Scanner Focus and CD Response Characterization Metrology for Sub 180nm Lithography Christopher Putnam, Holly Magoon, Muhammad Alam, Shelley Beaumont, Catherine Fruga, Frank Leung, Etsuya Morita, Ronald Pierce, Norman Roberts, Nikon Precision Inc. | 381 |

| Comprehensive and Easy to Use SEM Analysis Structures for BiCMOS Process Development Steven Leibiger, Fairchild Semiconductor Corp.                                                                                                                             | 390 |

| Metro-3D: An Efficient Three Dimensional Wafer Inspection Simulator for Next Generation Lithography Zhengrong Zhu, Aaron L. Swecker, Andrzej J. Strojwas, Carnegie Mellon University                                                                            | 396 |

| Automated Residual Metal Inspection R. Tiwari and J. Strupp, Texas Instruments, Inc.; P. Terala and D. Shoham, Applied Materials, Inc.                                                                                                                          | 402 |

| The Implementation of AFM for Process Monitoring and Metrology in Trench MOSFET Device Manufacturing Rodney S. Ridley, Sr., Chris Strate, Joe Cumbo, Tom Grebs, Chris Gasser, Fairchild Semiconductor Corp.                                                     | 408 |

| Neural Network Modeling of Reactive Ion Etching Using Principal Component Analysis of Optical Emission Spectroscopy Data Sang J. Hong and Gary S. May, School of Electrical and Computer Engineering, Georgia Institute of Technology                           | 415 |

# In-line electrical characterization of ultrathin gate dielectric films

Florence Cubaynes, Sophie Passefort<sup>1</sup>, Kwame Eason<sup>1</sup>, Xiafang Zhang<sup>1</sup>, Lucien Date<sup>2</sup>, Didier Pique<sup>2</sup>, Thierry Conard<sup>3</sup>, Aude Rothschild<sup>3</sup>, Marc Schaekers<sup>3</sup>

Philips Research Leuven, Belgium; <sup>1</sup>KLA-Tencor Corporation, Santa Jose, CA, USA; <sup>2</sup>Applied Materials, Meylan, France; <sup>3</sup>IMEC, Leuven, Belgium

#### **Abstract**

In this paper, in-line measurements of ultrathin gate dielectrics are reported. Various plasma nitrided oxides down to 1.5 nm EOT have been studied using in-line optical and non-contact electrical measurement techniques. The good correlation obtained with physical analysis and "classic" capacitance-voltage measurements shows the suitability of in-line measurement techniques for a first qualitative evaluation of ultrathin dielectric films.

### Keywords

Nitrided oxide, plasma nitridation, gate dielectric, inline characterization, Quantox, capacitance, EOT.

#### Introduction

Progress in CMOS technology has been dominated by the scaling down of device feature sizes. One of the many challenges in CMOS scaling is the continued increase of the gate dielectric capacitance per unit area. This can be accomplished by either reducing the gate dielectric thickness or increasing the gate dielectric constant  $(\varepsilon_r)$ . For rapid assessment and optimization of new gate dielectric materials such as nitrided silicon oxide, a reliable in-line characterization of these ultrathin films is required [1]. This work presents results from in-line optical and electrical characterization of heavily nitrided oxides formed in a rapid thermal processing (RTP) chamber with plasma nitridation (PN) capability. In addition, the obtained results are compared to conventional physical and electrical characterization.

#### **Experiment**

In this study, ultrathin nitrided oxides were grown on high quality p-type Si (100) wafers. The bottom silicon oxide was grown using a rapid thermal oxidation (RTO) or an in-situ steam generation (ISSG) oxidation and was followed by a plasma nitridation. Two different nitridation techniques have been studied (PN1 and PN2). The oxynitrides received a post anneal at  $1000^{\circ}$ C under  $N_2$  for 60 seconds and  $1000^{\circ}$ C under  $O_2$  for 15 seconds for PN1 and PN2 nitridation, respectively. Table 1 summarizes the different conditions and variants used for this experiment.

| Base oxide | Plasma nitridation        |                          |

|------------|---------------------------|--------------------------|

| RTO/ISSG   | PN1                       | PN2                      |

| 950°C      | 550°C, 240 sec, 3<br>Torr | 27°C, 15 sec,<br>25mTorr |

| 12 Å       | 20 % He                   |                          |

| 13 Å       | 20, 40, 60, 80 %<br>He    |                          |

| 15 Å       | 20, 40, 60, 80 %<br>He    | 95 % He                  |

| 16 Å       | 20 % He                   |                          |

| 20 Å       | 20 % He                   |                          |

**Table 1:** Process conditions used for the oxidation and the plasma nitridation.

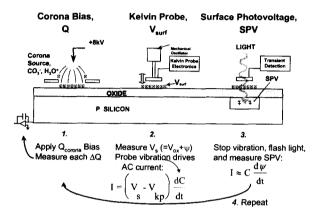

In-line optical measurements were performed using the KLA-Tencor ASET-F5 and physical analysis were performed using X-ray Photoelectron Spectroscopy (XPS). In-line electrical measurements were performed using the KLA-Tencor Quantox. The Corona-Oxide-Silicon (COS) Quantox system [1] is combining three non-contacting technologies: charged corona, vibrating Kelvin probe and a pulsed light source, as shown in Figure 1. Charged corona ions provide biasing and emulate the function of the gate electrode of the Metal Oxide Semiconductor (MOS) structure. The Equivalent physical Oxide Thickness (EOT) parameter is determined from dielectric capacitance. capacitance is determined from dO/dV accumulation in the COS system. The capacitance is

converted to thickness using  $\varepsilon_r = 3.9$ . Some second order corrections can be applied to acquire data to account for semiconductor band bending.

After completion of MOS capacitor fabrication, conventional, Capacitance-Voltage (C-V) measurements were performed on capacitors of 100  $\mu mx100~\mu m$ . The C-V EOT was extracted using the CVC modeling program from NCSU [2], accounting for polysilicon depletion of gate electrode and quantum mechanical effects in substrate.

Figure 1: Quantox COS measurement theory.

#### Results and Discussion

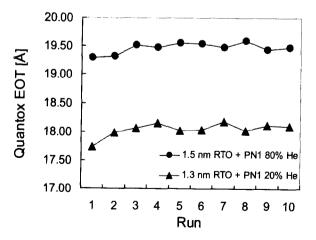

In-line electrical measurement of the EOT of ultrathin dielectric films has been performed using the Quantox. The stability of the in-line EOT measurement has been assessed, and determined to be  $3\sigma < 0.4$  Å static repeatability. The repeatability data is presented in Figure 2.

**Figure 2:** Stability of the Quantox EOT. The measurement of the EOT of two different dielectrics has been repeated ten times. The 3-sigma variation is less than 0.4 Å for both EOTs.

Based on the optical thickness and the EOT measured respectively with the ASET-F5 and the Quantox, the physical thickness and dielectric constant of the ultrathin nitrided oxides have been estimated. For this purpose, some basic assumptions have been made: a linear transition on optical constant (n) from pure oxide (SiO<sub>2</sub>) to pure nitride (Si<sub>3</sub>N<sub>4</sub>) (Equation 1) as well as a linear correlation of optical constant to dielectric constant (Equation 2) have been assumed using Palik optical tables (Table 2) [3].

$$T_{optical} = \frac{n}{n_{SiO_2}} T_{physical} \tag{1}$$

$$\varepsilon_r = 6.383 \times n - 5.4 \tag{2}$$

|         | n @ 633 nm | E <sub>r</sub> |

|---------|------------|----------------|

| Oxide   | 1.457      | 3.9            |

| Nitride | 2.021      | 7.5            |

Table 2: Palik optical tables for pure oxide and pure nitride.

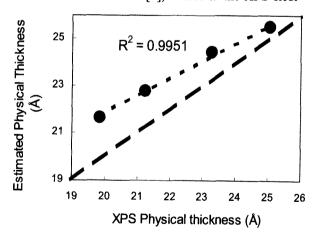

Figure 3 shows a strong correlation of the estimated physical thicknesses with the thicknesses calculated from XPS analysis. This relation is diverging from a 1:1 correlation when the films get thinner. This might be attributed to the assumptions made to calculate the physical thicknesses (e.g. AMC noise on optical thickness measurements [4]) and/or to the XPS error

Figure 3: Correlation between the estimated physical thickness with the thickness calculated from XPS analysis of thin nitrided oxide films formed with a base oxide of 1.5nm followed by a plasma nitridation with different dilution ratio: 20, 40, 60, 80 % He.

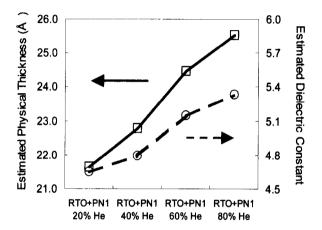

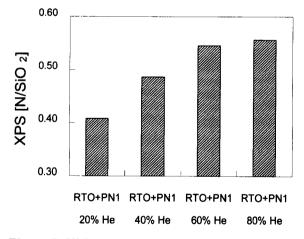

Figure 4 shows that when the He dilution percentage (the dilution ratio in the PN chamber) is increased, both the physical thickness and the dielectric constant increase. A higher He dilution percentage in PN1 process results in more physical growth of the dielectric. The increase in dielectric constant with increasing N content is in accordance with previously published result [5] and with XPS measurements presented in Figure 5. Figure 5 confirms that a higher He dilution ratio causes an increase of the nitrogen content incorporated in the film, which leads to an increase of the dielectric constant.

Figure 4: Estimated physical thickness and dielectric constant of nitrided thin films formed with a base oxide of 1.5 nm followed by a plasma nitridation (PN1) with different He dilution ratio.

Figure 5: XPS measurements of the nitrogen content in nitrided oxide films formed with a base oxide of 1.5 nm followed by a plasma nitridation (PN1) with different He dilution ratio.

Dielectrics with various base oxide thicknesses followed by a common nitridation have been studied.

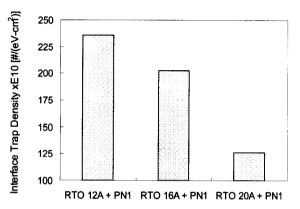

The thinner the base oxide the more nitrogen is incorporated in the film, as shown in the literature [6]. The interface trap density in such films has been measured with the Quantox. A higher interface trap density has been measured for the thinner films which contain a higher amount of nitrogen. This is in accordance with previous work [7] showing that a large amount of charges (fixed charges, interface states) are incorporated in the dielectric during the plasma nitridation process. The higher Dit implies that the incremental N is located primarily at the Si-SiO<sub>2</sub> interface.

**Figure 6:** Interface trap density of nitrided oxide films formed with various base oxide thicknesses and followed by a common plasma nitridation (PN1).

Figure 6, in conjunction with Figures 4 and 5, illustrates the correlation between increases in He dilution, nitrogen incorporation, and interface states. The end-of-line electrical (transistor) interface trap density is less than in-line electrical (Quantox) [7], which is attributed to the additional high temperature processing beyond gate dielectric formation. The additional high temperature processing, and particularly the final forming gas anneal, seen by the end of line dielectric serves to reduce the interface trap density. Yet, the amount of nitrogen in ultrathin oxynitride films has been qualitatively measured by performing in-line electrical measurements.

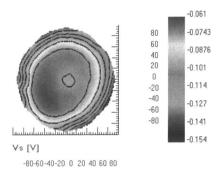

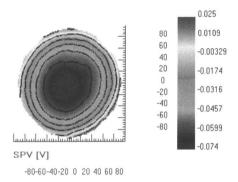

Quantox mapping capabilities have been used to look at the non-uniformity of plasma nitridation PN1. Figures 7 and 8 show a radial pattern for respectively the surface voltage (Vs) and the surface photo voltage (SPV).

**Figure 7:** Surface Voltage (Vs) map of 1.5 nm RTO followed by PN1 with 80% He dilution ratio.

**Figure 8:** Surface PhotoVoltage (SPV) map of 1.5 nm RTO followed by PN1 with 80% He dilution ratio.

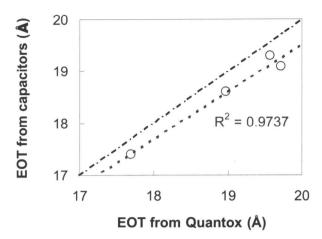

This non-uniformity has been quantified with 4-point measurements from the center to the edge of the wafer. The EOT values, measured with the Quantox or extracted from C-V curves using the CVC model. confirm the radial non-uniformity observed in the Vs and SPV maps (Figure 9). A variation of about 2 Å is observed from the center to the edge of the wafer. Further optimisation of the PN1 process conditions will be needed to address the non-uniformity issue. Figure 9 shows the correlation between the EOT measured on the Quantox and the EOT extracted from C-V curves. The minor differences seen between the two EOTs can be attributed to the extra processing steps needed to manufacture capacitors. Yet, these results show that it is possible to obtain inline electrical test measurements that correlate strongly with conventional off-line C-V analysis.

**Figure 9:** Correlation between the EOT measured with the Quantox and the one extracted from C-V curves using the CVC fitting model. This correlation is made for a 1.5 nm base oxide followed by PN1 with 80% He on four locations on the wafer.

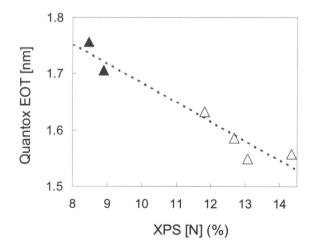

Finally, in-line measurement of the EOT has been made for dielectrics with a fixed base oxide thickness followed by different nitridation processes: PN1 and PN2 (Table 1). The physical thickness, estimated using equations 1 and 2, was the same for the studied dielectrics while the dielectric constant was higher for the oxynitrides formed with PN2. Correlation of the EOTs and the amount of nitrogen in the films has been established, as presented in Figure 10. As expected [5, 8, 9], the higher the amount of nitrogen in the film, the smaller is the EOT. In this study, the lower EOT films were achieved with PN2.

**Figure 10:** Amount of nitrogen in the oxynitride films as a function of the EOT measured with the Quantox. The dielectrics studied have the same base oxide thickness but various plasma nitridation processes: PN1 and PN2 (Table 1).

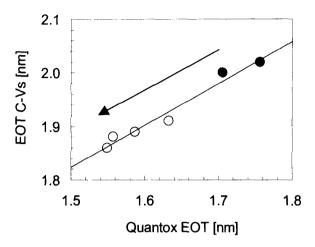

A comparison between the EOT measured with the Quantox and the EOT extracted from C-V curves is illustrated in Figure 11. Again, the differences seen between the two EOTs can be attributed to the extra processing steps needed to manufacture capacitors.

Figure 11 Correlation of the EOT measured with the Quantox and the one extracted from C-V curves using the CVC fitting model for dielectrics with different nitridation PN1 and PN2 (Table 1).

These results show that it is possible to obtain a correlation between in-line and off-line electrical measurements. This allows for a fast screening and first qualitative optimization of novel gate dielectrics.

#### **Conclusions**

In this paper, ultrathin plasma nitrided silicon oxide films have been characterized using in-line optical and non-contact electrical measurements. Two different plasma nitridation processes have been studied. The correlation obtained between the optical thickness, physical analysis, capacitor and Quantox measurements demonstrates that in-line electrical characterization is well suited for a first qualitative evaluation of ultrathin dielectric films.

The EOT of various dielectrics has been measured using the Quantox. A static repeatability 3 $\sigma$  better than 0. 4 Å was achieved. The physical thickness and the dielectric constant were estimated using in-line optical and electrical measurements and correlated to XPS analysis. The amount of nitrogen in ultrathin oxynitride films has been qualitatively measured by performing in-line electrical measurements. We found a correlation between increases in the He dilution ratio of the plasma nitridation process, nitrogen incorporation, and interface trap density. Finally, two different plasma nitridation processes were compared demonstrating the usefulness of in-

line electrical measurements as a first optimisation of thin gate dielectrics.

#### **Acknowledgement**

This work was partly funded by the European Union under IST-1999-11599 HUNT project.

#### References

- [1]. C. Hayzelden et al., SEMI Tech. Symp., p23 (1999).

- [2]. J.R. Hauser et al., Characterization and Metrology for ULSI Tech.: Int. Conf., p235 (1998).

- [3] Handbook of Optical Constants of Solids. Edited by E.D. Palik. Academic Press, 1985.

- [4] K. Eason et al., SEMICON Southwest STS, p69 (2001)

- [5]. K. Eason et al., ECS Toronto, p195 (2000).

- [6]. F.N. Cubaynes et al., to be published.

- [7]. Y. Okayama et al., Symp. VLSI Tech. Dig., p220 (1998).

- [8] S. Hattangady et al., SPIE Symp. Microelec. Manuf. (1998)

- [9] H. Al-Shareef, et al., ECS Toronto, p210 (2000).

## Alternative Smart-cut-like Process for Ultra-thin SOI Fabrication

Alexander Usenko Silicon Wafer Technologies 240 King Blvd Newark, NJ USA usenko@si-sandwich.com William N. Carr, Bo Chen

New Jersey Institute of Technology

University Heights

Newark, NJ

USA

carr@njit.edu, bc3@njit.edu

Yves Chabal Agere Systems 600 Mountain Ave. Murray Hill, NJ USA yves@agere.com

#### **Abstract**

We describe for the first time a layer transfer caused by delamination along the hydrogen laver formed bv plasma hydrogenation at a place of end-of-range defects. The process involves first creating a buried trap using variously silicon. or implantation. Wafers thus processed with an initial implant to levels below 1016 cm-2 are then hydrogenated with RF plasma. Next steps include pre-bonding, cleavage, and post-bonding as in the Smart-cut process. The cleavage occurs at a depth corresponding to the maximum of vacancyenriched defects (between R<sub>p</sub>/2 and R<sub>p</sub>). Plasma hydrogenation may be used as a step in the process of fabricating thin SOI wafers.

#### Keywords

Silicon-on-insulator Layer transfer Plasma hydrogenation Thin top layer SOI

#### 1. Introduction

The International Technology Roadmap Semiconductors 2001 [1] projects that the top silicon layer for SOI starting wafers will be 20 to 100 nm in thickness by 2004 to support processing of fullydepleted CMOS circuits. At the present time processes such as Smart-Cut<sup>TM</sup> provide an inherent silicon film thickness of about 500 nm and a minimum thickness of about 200 nm [2]. The thickness of the delaminated layer in the Smart-Cut process depends on the energy of implantation of hydrogen. When the energy of the hydrogen implant is reduced to levels below 50 keV to achieve thin delaminating thickness problems arise [3 - 5]. Attempts have been reported to thin the surface silicon layer of Smart-cut processed wafers to obtain SOI wafers with surface films of less than 200 nm thickness. Terreault et al. [3 - 5] used low energy

hydrogen implantation (5 to 8 keV) in a regular Smart-cut to get a thinner top SOI layer. They report blistering the thin layer, but do not describe the layer transfer. Maleville at al. [6] reports 70 nm top Si SOI using touch polishing of an initial 500 nm layer. Srikrishnan [7] forms an etch stop layer inside of the transferred with Smart-Cut silicon film by implantation into the top silicon layer with a subsequent etching. Popov [8] reports a layer-bylayer oxidation (of the film transferred with Smartcut) with subsequent stripping in diluted HF for thinning of the layer. All listed approaches increase SOI wafer production cost and degrade thickness uniformity. Our work here reports the utilization of RF plasma hydrogenation as a post process following a low level implant to create the desired surface layer of thickness less than 100 nm.

#### 2. Experimental

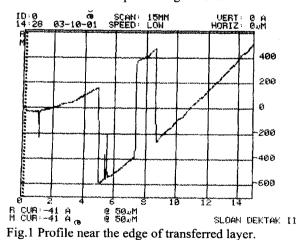

Silicon wafers were ion implanted with silicon, argon, or hydrogen to form a buried trap layer for hydrogen. Then the as-implanted wafers were hydrogenated in an RF plasma setup Tegal-100 at hydrogen pressures of 0.5 to 10 Torr and an RF power of 300 Watts. Importantly, the RF plasma processing is performed in two temperature regimes: a first step 200°C or less and a second step at 300°C or more. Pre-bonding, cleavage, and post-bonding steps were performed according to the as in the Smart-cut process. The thickness of transferred layers was measured with a Dektak profilometer near wafer edges where the layer transfer fails. Infrared absorbtion measurements were performed using both transmission and multiple internal reflection geometries [9] to gain access to both bonding and stretching vibrations of trapped hydrogen.

#### 3. Results

The layer transfer occurs in cases of proper selection of implantation conditions and plasma hydrogenation conditions. A typical edge profile of the transferred layer is shown on Fig.1. The thickness of the transferred layer is 75 nm. The donor wafer properties, implantation, and plasma hydrogenation conditions are listed in the Table below.

| Table                             |                              |

|-----------------------------------|------------------------------|

| Wafer                             |                              |

| Diameter                          | 100 mm                       |

| Growth                            | Czochralski                  |

| Dopant                            | Boron                        |

| Resistivity                       | 1 Ohm cm                     |

| Implantation                      |                              |

| Specie                            | Silicon                      |

| Energy                            | 180 keV                      |

| Dose                              | $2x10^{15}$ cm <sup>-2</sup> |

| Hydrogenation                     |                              |

| Source                            | RF plasma                    |

| Plasma power                      | 300 Watts                    |

| Temperature, 1st step             | 200°C                        |

| Duration, 1 <sup>st</sup> step    | 1 hour                       |

| Temperature, 2 <sup>nd</sup> step | 350°C                        |

| Duration, 2 <sup>nd</sup> step    | 1 hour                       |

The profile is shown in Fig.1 for the silicon-intosilicon implantation for trap layer formation. In this case the surface silicon layer is 75 nm in thickness. Similar results are obtained for some other heavier ions that penetrate less deeply.

Infrared absorbtion measurements taken on samples annealed up to 300°C during the second plasma immersion step indicate that hydrogen is primarily located on internal surfaces, with some H still in monovacancy-type defects such as VH and VH<sub>3</sub>. This finding is consistent with previous studies [9]. Further studies are under way to characterize the nature and location of hydrogen incorporated in the silicon as function of processing conditions.

4. Discussion

Our previous work [10] we reported silicon flaking along a hydrogenated trap layer. We used electrolytic hydrogenation. In the present paper we present results using plasma instead of electrolytic hydrogenation.

Hydrogen in atomic form is known for its high diffusivity in silicon and its ability to combine with many types of defects in crystalline silicon. It has been known since 1987 that plasma hydrogenation of single crystalline silicon can result in the formation of hydrogen platelets [11,12]. Because of the lack of defects in silicon bulk and low hydrogen solubility in silicon, the platelets in [11,12] are found in nearsurface defect-rich regions only. To control the process of hydrogen platelet distribution in silicon, an additional step in the formation of the defect-rich layer is needed. To accumulate hydrogen in the desired part of the wafer we need to pre-form defects that readily interact with hydrogen. Silicon-intosilicon implantation forms a dense defect layer at desired depth under the surface.

An inherent delaminating thickness for either Smart-cut or the trap-filling processes is controlled by implantation depths [3, 6, 8]. For Smart-cut the depth is the  $R_p$  of hydrogen while for the trap-filling process is between  $R_p/2$  and  $R_p$  for heavier ions. Correspondingly, the layer transfer depths are 200-2000 nm, and 20-200 nm. Therefore, the trap-filling process is advantageous for making thin SOI.

At the beginning of plasma hydrogenation, atomic hydrogen diffuses through silicon and attaches to broken bonds in a layer damaged by implantation [11]. The next step in hydrogen evolution is to form nuclei of hydrogen platelets. It happens at temperatures lower than 250°C as previously found by Johnson et al. [12]. Further hydrogenation increases the platelet size and can be done at higher temperatures. Higher temperature during the second stage of hydrogenation is also needed to allow Oswald ripening during which time bigger platelets grow at the expense of smaller ones [12].

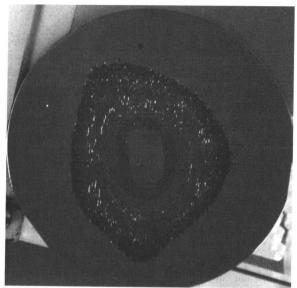

Fig.2. Typical wafer blistered during implantation. Implantation conditions: H<sub>2</sub><sup>+</sup> at 100 keV, 0.3 mA.

Experiments with blistering were widely used elsewhere to understand phenomena involved in the Smart-cut [3, 9, 14] process. At the level of hydrogen implantation required in Smart-cut (i.e. about 4x1016 cm<sup>-2</sup>), the silicon surface easily blisters during implantation (Fig.2), even without an additional annealing. The silicon wafer surface can be also blistered after RF plasma hydrogenation. An interesting feature is that the minimum hydrogenation time in RF plasma required for blistering is several times longer, than the time required for successful layer transfer. Typical blistering picture after RF plasma hydrogenation and subsequent anneal is shown on Fig.3 and Fig.4. It was found that the hydrogen implantation dose needed for blistering is about the same as the dose required for layer transfer (for the same annealing temperatures). We suppose, that in our case there is much higher hydrogen loss due to outdiffusion than for the case of blistering caused by high dose hydrogen implantation. These hydrogen losses may be due to the proximity of surface, or due to a difference in the type of the traps binding the hydrogen. When the hydrogen-rich layer (either obtained by trapping of by implantation) evolves into a quasi-continuous cleavage plane, the hydrogen atoms or ions detraps from one defect, diffuse to another defect with higher bonding energy, and get trapped again. In a case of high dose hydrogen implantation the higher mechanical stress is expected, so we expect more weakened silicon bonds, and higher bonding energy for hydrogen attaching to those sites.

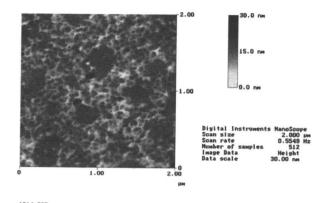

Fig.3. Surface relief developed on self-implanted silicon wafer after plasma hydrogenation, (area of view  $2x2 \mu m^2$ ).

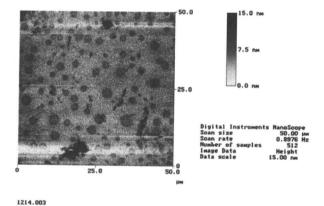

Fig.4. Surface relief developed on self-implanted silicon wafer after plasma hydrogenation, (area of view 50x50 µm²).

Figures 3 and 4 show the surface of a wafer processed with self-implantation+hydrogenation. The surface is covered with features with lateral dimensions about 0.2 micron and vertical dimension about 5 nanometers. Infrared measurements show high hydrogen peak.

To keep the large amount of hydrogen inside the silicon wafer, the local temperature under the beam should not substantially exceed room temperature. This restriction severely limits the maximum hydrogen ion beam current during the implantation step in the Smart-cut process. For similar process work reported elsewhere [13-18] and by ourselves [19-26], the hydrogen beam current is limited to 0.1 mA using conventional implant equipment in order to maintain the lower implant temperatures. At this beam current density we require 24 hours to fully implant a wafer with hydrogen using the published

Smart-cut process making the process ineffective. Higher implant rates are possible using implanters with a special cooling system, but there are no published data yet that confirm efficiency of the cooling for this case. In our process, neither high dose implantation not hydrogen implantation are needed, thus making our process potentially advantageous. Also, the typical implantation doses needed to form the trap layer is lower than 10<sup>15</sup> cm<sup>-2</sup>, that might result in better crystalline quality of the top layer in the final SOI wafer as compared to the Smart-cut.

The RF plasma causes a platelet nucleation and growth along a layer at a depth of about ½Rp of the defect-inducing implant. The room temperature step of the plasma process is for nucleation, and the 300oC step is for fast growth, similar as in [4,5]. The surface features of Fig's 1 and 2 show smaller features by a factor of 10x and 100x for lateral and vertical dimensions, respectively, compared with laboratory results [2,3] obtained with heavy hydrogen implants.

#### 4. Conclusion

RF plasma hydrogenation of a buried trap layer formed with low dose ion implantation has been demonstrated for forming silicon SOI with a thin top layer. Experiments described here indicate that the trap-filling process can provide a 10X reduction in SOI top layer thickness.

#### Acknowledgment

Partial funding from National Science Foundation SBIR award No. 0109573 is gratefully acknowledged. We acknowledge the assistance of Dr. Dentcho Ivanov at the New Jersey Institute of Technology with wafer bonding and Dr. Vladimir Popov from Institute of Semiconductor Physics, Novosibirsk, Russia for ion implantation of samples and for interesting discussions.

#### References

- [1] The International Technology Roadmap for Semiconductor, 2001, Front End Processes, p.7, (2001).

- [2] General Specification for: customized UNIBOND® Wafers, SOITEC, 2001.

- [3] C. Qian and B. Terreault, "Blistering of silicon crystals by low keV hydrogen and helium ions", Journal of Applied Physics, Vol. 90, pp. 5152–5158, (2001).

- [4] C. Qian, B. Terreault, and S. C. Gujrathi, Layer splitting in Si by H+He ion co-implantation:

- Channeling effect limitation at low energy", *Nuclear Instr. and Meth. in Phys. Res. B*, Vol. 175-177, pp. 711-714, (2001).

- [5] C. Qian, B. Terreault, "Layer splitting by H-ion implantation in silicon: Lower limit on layer thickness?", Materials Res. Soc. Symp. – Proceedings, Vol. 585, pp. 177-182, (2000).

- [6] C. Maleville; E. Neyret; L. Ecarnot; E. Arene; T. Barge; A.J. Auberton, "Unibond SOI wafers for ultra-thin films applications", 2001 IEEE International SOI Conference, pp. 155-156 (2001).

- [7] K.V. Srikrishnan, "Smart-cut process for the production of thin semiconductor material films", US Patent 5,882,987, March 16, 1999.

- [8] V.P. Popov et al. "Properties of extremely thin silicon layer in silicon-on-insulator structure formed by smart-cut technology", Materials Sci. and Engineering **B73** 82–86 (2000).

- [9] M. K. Weldon, V. E. Marsico, Y. J. Chabal, A. Agarwal, D. J. Eaglesham, J. Sapjeta, W. L. Brown, D. C. Jacobson, Y. Caudano, S. B. Christman, and E. E. Chaban, "On the mechanism of the hydrogen-induced exfoliation of silicon", J. Vac. Sci. Technol. B 15, pp. 1065-1073, 1997.

- [10] .A.Y.Usenko, W.N.Carr, "Electrolytic Hydrogenation of Buried Preamorphized Layer in Silicon for SOI Wafer Process", in: Siliconon-Insulator Technol. and Devices, Proc., ed. S. Cristoloveanu, vol. 2001-3, Electrochem. Soc., 33-38 (2001).

- [11] N. H. Nickel, G. B. Anderson, N. M. Johnson, and J. Walker, "Nucleation of hydrogen-induced platelets in silicon", Phys. Rev. B **62**, 8012-8015 (2000).

- [12] N. M. Johnson, F. A. Ponce, R. A. Street, and R. J. Nemanich, Defects in single-crystal silicon induced by hydrogenation, Phys. Rev. B 35, 4166–4169 (1987).

- [13] K. Henttinen and I. Suni S. S. Lau, "Mechanically induced Si layer transfer in hydrogen-implanted Si wafers", Appl. Phys. Lett., Vol. 76, pp. 2370–2372, (2000).

- [14] Y. Zheng and S. S. Lau T. Höchbauer, A. Misra, R. Verda, X.-M. He, and M. Nastasi J. W. Mayer, "Orientation dependence of blistering in H-implanted Si", Journ. of Appl. Phys., Vol. 89, pp. 2972–2978, (2001).

- [15] M. B. H. Breese L. C. Alves T. Hoechbauer and M. Nastasi, "Study of the crystalline quality of exfoliated surfaces in hydrogen-implanted silicon", Appl. Phys. Lett., Vol. 77, pp. 268–270, (2000).

- [16] D. L. da Silva, P. F. P. Fichtner, M. Behar, A. Peeva, R. Koegler and W. Skorupa,

- "Implantation temperature dependence of He bubble formation in Si", Nuclear Instr. and Meth. in Phys. Res. B, in press (2002).

- [17] V.P. Popov, I.V. Antonova, A.K. Gutakovsky, E.V. Spesivtsev, I.I. Morosov, "Ellipsometry and microscopy study of nanocrystalline Si:H layers formed by high dose implantation of silicon", Materials Sci. and Eng. B73 120–123 (2000).

- [18] K. Henttinen, T. Suni, A. Nurmela, I. Suni, S. S. Lau, T. Höchbauer, M. Nastasi and V. -M. Airaksinen, "Cold ion-cutting of hydrogen implanted Si", Nuclear Instr. and Meth. in Phys. Res. B, in press (2002).

- [19] A. Y. Usenko, A. G. Ulyashin, "Thinner SOI Using Plasma Hydrogenation", Japanese Journal of Applied Physics, in press, April, 2002.

- [20] A.Y. Usenko, W.N. Carr, and Bo Chen, "Plasma Hydrogenation of a Buried Trap Layer in Silicon: Formation of a Platelet Layer" in: Proc. of Int. Symp. On Plasma Processing XIV, presented at 201th Meeting of Electrochemical Society, 2002, in press.

- [21] A.Y.Usenko, W.N. Carr, "Blistering on Silicon Surface Caused by Gettering of Hydrogen on Post-Implantation Defects", Materials Res. Soc. Symp. Proceeding Vol.681E, 2001, pp.I3.3.1-I3.3.6, presented at MRS Spring Meeting, San-Francisco, CA, Apr. 16-20, 2001.

- [22] A.Y.Usenko, W.N. Carr, "Hydrogenation of Trap Layer as an SOI Process Step", in: Proceedings of 2000 IEEE SOI Conference, Wakefield, MA, Oct.2000, pp.16-17.

- [23] A.Y. Usenko, A.G. Ulyashin, W.N. Carr, W.R. Fahrner, A.V. Frantskevich, R.Job, "Thinner SOI Using Plasma Hydrogenation", Extended Abstracts of Int. Conf. on Solid State Devices and Materials, Sept. 26-28, 2001 Tokyo, Japan, pp.244-245 (2001).

- [24] A.Y. Usenko, W.N. Carr, B. Chen A.G. Ulyashin, "Forming on hydrogen platelet layer in silicon from hydrogen trapped onto microbubbles of noble gases", presented at 2002 MRS Spring Meeting.

- [25] W.N. Carr, B. Chen, A.Y. Usenko, "Improved Process for Thin Silicon-On-Insulator", presented at Advanced Workshop on Frontiers in Electronics (WOFE) St. Croix, Virgin Islands, USA January 6 - 11, Abstracts pp.64-65 (2002).

- [26] W.N. Carr, B. Chen, A.Y. Usenko, "Delamination of Crystalline Silicon Film from Substrate through Hydrogenation of Trap Layer", presented at Annual Amer. Physical Soc. March Meeting 2002, Indianapolis, IN, Abstracts, paper A18.008.

# A Manufacturable Shallow Trench Isolation Process for sub-0.2um DRAM Technologies

W. Y. Lien, W. G. Yeh, C. H. Li, K. C. Tu, I. H. Chang, H. C. Chu, W. R. Liaw, H. F. Lee, H. M. Chou, C. Y. Chen, and M. H. Chi R&D, Taiwan Semiconductor Manufacturing Company, Ltd. Hsin-Chu, Taiwan, R.O.C.

#### Abstract

A highly manufacturable and defect-free shallow trench isolation (STI) process is demonstrated by using 64M DRAM as a sensitive monitor. In the STI flow, a special sequence of extra anneal (1100C) after corner oxidation (i.e., liner oxide) and an RTA (1000C) anneal after HDP CVD oxide deposition can result in a significantly higher yield in 64M DRAM by effectively reducing silicon stress related substrate defects.

#### Keywords

DRAM, STI, liner oxide, HDP CVD oxide, SiN pull-back

#### I. Introduction

Shallow trench isolation (STI) is the most favorable scheme for advanced CMOS technology (since 0.25um generation) due to its high scalability and excellent isolation capability [1-3]. One of the most critical issues of STI process [4-5] is the reduction of stress related defects as resulted from nitride and silicon trench etch, liner oxidation, HDP CVD oxide gap-fill, and more importantly those subsequent thermal cycles and high energy implants. The stress can result in defects later in the process, especially triggered by high energy Arsenic implantation for source-drain. Such defects lead to many undesirable effects (e.g. increasing diode leakage, punch-through in transistor, GIDL in pass transistor, degradation of refresh time in DRAM) leading to low yields. Recent studies discussed methods for reducing such STI related stress and defects in silicon by applying high-temperature annealing after device and gate formation [4-5]. However, these methods are not suitable for advanced CMOS, as they will increase dopant diffusion and serious short-channel effects.

This paper reports a highly manufacturable STI flow by using high-temperature annealing before device and gate formation. We have compared the process variables impacting the generation of STI

defects, including flow sequence of corner oxidation and HDP CVD oxide densification. In addition, the effects of STI SiN pull-back and sacrificial oxide (SAC-ox) formation on the cell transistor performance and 64M DRAM CP1 yield are also studied.

#### II. Experiments

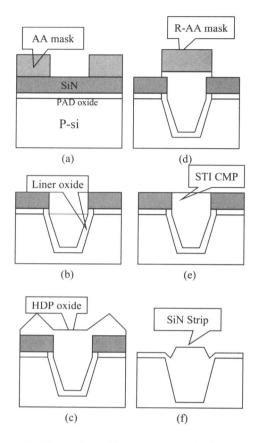

A brief description of the STI process flow used in this study is similar to conventional flow as sketched in Figure 1. After forming film stacks of pad oxide and nitride on substrate, a mask for defining active area (AA mask) is used by etching nitride, pad oxide and silicon substrate (Figure 1a). Then, a liner oxide is grown on the exposed substrate surface (Figure 1b). After the trench is filled by HDP CVD oxide (Figure 1c), a reverse AA (R-AA) masking step is performed (Figure 1d), and followed by plasma etching of HDP CVD oxide on the larger AA area. After photo-resist removal, oxide CMP is conducted (with nitride as a stop layer) for planarization (Figure 1e). Then the nitride layer is stripped by wet process to complete the STI fabrication (Figure 1f).

The key features of the DRAM vehicle used in this study are summarized in Table 1. The process technologies implemented include 3000A STI depth, retrograded triple-well, SAC (self-aligned contact) for storage node contact and bit-line contact, crown structure of cell capacitors, and tungsten bit-line.

**Table 1.** Key technology features of 64M DRAM in this study.

| Minimum Feature  | 0.19 um               |  |

|------------------|-----------------------|--|

| Minimum Pitch    | 0.44 um               |  |

| Cell Structure   | CUB                   |  |

| Isolation        | STI                   |  |

| STI Trench Depth | 3000A                 |  |

| Cell Size        | 0.387 um <sup>2</sup> |  |

Figure 1: Illustration of key process steps for STI flow.

Additional process steps of STI nitride pull-back, annealing after liner oxide, RTA for HDP CVD oxide, and sacrificial oxide formation performed in this study are described below.

#### III. Results and Discussions

#### **Effects of STI Process Sequences**

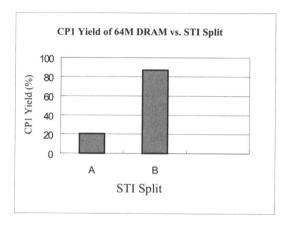

Process variables impacting the generation of STI defects, including the flow sequence of corner oxidation and HDP CVD oxide densification are studied. Table 2 shows the split conditions of the present study for the STI liner oxide and HDP CVD oxide flow sequences. Wafer of Group-A was implemented with a high-temperature furnace anneal (1100C) after depositing STI HDP CVD oxide. In the Group-B wafer, the high-temperature furnace anneal (1100C) was used after STI corner liner oxidation, and a RTA annealing step was used to densify STI HDP CVD oxide.

The dependence of 64M DRAM CP1 yield on the STI flow sequence is shown in Figure 2. The major yield loss found in the Group-A process is related to the DC fail, as resulted from abnormal standby leakage current on the CP1 test.

**Table 2.** Split table for liner oxide anneal and HDP CVD oxide anneal in STI.

| Flow          | Split         | Wafer # |   |

|---------------|---------------|---------|---|

| Liner Oxide   | 1100C furnace |         | В |

| Anneal        | w/o           | A       |   |

| HDP CVD       | 1100C furnace | A       |   |

| Oxide Densify | 1000C RTA     |         | В |

**Figure 2:** 64M DRAM's CP1 yield with STI flow splits (referred to Table 2).

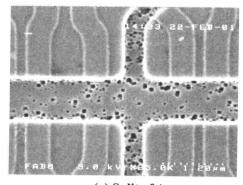

To find out the root cause of the abnormal leakage current occurred in Group-A process, we checked the SEM plan view by using de-layering and Wright etching methods. Figure 3 shows the SEM results and the STI substrate defects can be easily found in the sense-amplifier (SA) area with N+ (As) implant in Group-A wafers (Figure 3(a)). However, Group-B wafers have no such substrate defects found in the SA area with N+ implant (Figure 3(b)). By using the STI process sequence of Group-B, the STI substrate defects can be effectively eliminated and a significantly higher 64M DRAM yield is achieved as shown in Figure 2.

(a) Split of A