# 2001 SYMPOSIUM ON VLSI CIRCUITS

DIGEST OF TECHNICAL PAPERS

001880

# 2001 SYMPOSIUM ON VLSI CIRCUITS

DIGEST OF TECHNICAL PAPERS

#### **Publication Office**

Business Center for Academic Societies Japan 5-16-9 Honkomagome, Bunkyo-ku, Tokyo 113-8622, Japan

Copyright © 2001 by the Japan Society of Applied Physics. All rights reserved.

JSAP CAT. No. AP012316 IEEE CAT No. 01 CH 37185

ISBN 4-89114-014-3 Softbound ISBN 0-7803-6632-8 Microfiche ISBN 4-89114-013-5 CD-ROM Edition

Copies of this Digest can be purchased from:

Inside Japan

Business Center for Academic Societies Japan

5-16-9 Honkomagome, Bunkyo-ku, Tokyo 113-8622, Japan

Outside Japan

IEEE Service Center Single Publication Sales Unit

445 Hoes Lane, Piscataway, NJ 08854, USA

#### **FOREWORD**

#### Welcome to the 2001 Symposium on VLSI Circuits

The Symposium on VLSI Circuits is sponsored by the Japan Society of Applied Physics and the IEEE Solid-State Circuits Society, in cooperation with the Institute of Electronics, Information and Communication Engineers of Japan and the IEEE Electron Devices Society.

The Symposium will celebrate its fifteenth anniversary, establishing as a major international forum for discussing recent advances in the design of VLSI circuits. This is the first symposium in the twenty first century, and we have expanded the scope to include new concepts in LSI and physical design tools, in addition to microprocessors, signal processors, memories, analog circuits, RF circuits and communication circuits. This year the Symposium has 22 daytime sessions and will present 76 outstanding papers selected from the 153 submitted papers from both industry and universities around the world. In addition, the Symposium will offer a one-day technical short course preceding the Symposium on June 13th. The topic is "Physical Design for Low-Power and High-Performance Microprocessor Circuits".

The Symposium features four invited talks covering its entire scope. The plenary session on June 14th opens with two invited talks. They are, "Digital Vision Chips and High-Speed Vision Systems" and "BSIM Model for Circuit Design Using Advanced Technologies". On June 15th the invited talk, "Development Trend of LTPS TFT LCD for Mobile Applications", is followed by another invited talk describing a unique video system application of MEMs.

VLSI Circuit Symposium evening rump sessions are well known for their selection of timely topics and lively discussions. This year there are four rump sessions. The first rump session, "Which Features of an IC Technology will Benefit Radio SOC?" is a joint rump session with the VLSI Technology Symposium scheduled on June 13th. The remaining three sessions are, "Will Start-Ups Outperform Big Companies?", "Power Supply for Future System LSIs" and "Diverse DRAM Architectures: Why and Who Wins?".

The excellent technical program represents the outstanding efforts of the Technical Program Committees under the leadership of the Program Chair, Masakazu Yamashina, and Co-Chair, Shekhar Borkar. The Committee members, all world-leaders in the field of VLSI design, have solicited strong and interesting papers, selected, and organized them into attractive technical sessions. We express our sincere thanks to all the members for their highly-skilled efforts. We do hope that you not only enjoy the presentation of the papers but join the lively discussions in and outside the sessions.

Next year, the Symposium will return to the Hilton Hawaiian Village in Honolulu, Hawaii, together with the Technology Symposium. We do hope you will attend again.

June 2001

Takayasu Sakurai

**David Scott**

Symposium Chair

Symposium Co-Chair

#### **EXECUTIVE COMMITTEES**

### Japan Society of Applied Physics

Chair: Takuo Sugano Toyo Univ., Japan Science and Technology

Co-Chair: Susumu Kohyama Toshiba Semiconductor Company

Members: Chun-Yen Chang National Chiao Tung Univ.

Masao Fukuma NEC

Yutaka Hayashi

Koichiro Hoh

Chang-Gyu Hwang

Takashi Ito

Atsushi Iwata

Univ. of Tsukuba

Univ. of Tokyo

Samsung Electronics

Fujitsu Laboratories

Hiroshima Univ.

Masakazu Kakumu Toshiba Semiconductor Company

Yoiiro Mano Matsushita Electric

Toshiaki Masuhara ASET Akihiko Morino Selete

Tadashi Nishimura Mitsubishi Electric

Tsunenori Sakamoto AIST

Takayasu Sakurai Univ. of Tokyo

**Masao Taguchi** Fujitsu **Eiji Takeda** Hitachi

Ken Takeya NTT Electronics

Fang-Churng Tseng TSMC

Masakazu Yamashina NEC

Hoi-Jun Yoo KAIST

IEEE

Chair: Richard Jaeger Auburn Univ.

Members: Asad Abidi Univ. of California

Dirk Bartelink Hewlett-Packard

Bill Bidermann PiXIM

Shekhar Borkar Intel

**Richard Chapman** Texas Instruments

Roger DeKeersmaecker

Youssef El-Mansy

Craiq Lage

IMEC

Intel

Motorola

Nino Masnari North Carolina State Univ.

Yoshio Nishi Texas Instruments

Kevin O'Connor Agere Systems

David Scott Texas Instruments

Bill Siu Inte

Charles Sodini Massachusetts Institute of Technology

Yuan Taur IBM Research Center

Peter Verhofstadt SRC Intel

### 2001 SYMPOSIUM ON VLSI CIRCUITS

Symposium Chair: Takayasu Sakurai Univ. of Tokyo Symposium Co-Chair: David Scott Texas Instruments

Program Chair:Masakazu YamashinaNECProgram Co-Chair:Shekhar BorkarIntelSecretary:Tadahiro KurodaKeio Univ.

(Publicity)

Gitty NasserbakhtProximPublications/Publicity:Masato MotomuraNEC

: Masato Motomura NEC (Publications)

Wai Lee Texas Instruments

iv

Treasurer:

Local Arrangements:

Shinii Odanaka Bill Bidermann

Hiroshi Hanafusa Kazunori Nakahara

**Bob Havemann**

Osaka Univ. **PiXIM**

Sanvo Electric

Sharp

TI/SEMATECH

### TECHNICAL PROGRAM COMMITTEES

#### JAPAN/FAR EAST

Chair:

Members:

Masakazu Yamashina

Mitsuru Hiraki

Akira Hyogo Makoto Ikeda

**Deog-Kyoon Jeong** Hidevuki Kabuo Takahiro Kamei

Changhyun Kim

Kazutoshi Kobayashi

Koji Kotani Nicky C.C. Lu Masataka Matsui

Takahiro Miki Toshihiko Mori Masato Motomura Kazunori Nakahara

Yusuke Ohtomo Katsunori Seno

Atsushi Wada

**NEC** Hitachi

Science Univ. of Tokyo

Univ. of Tokyo Seoul National Univ. Matsushita Electric

Oki Electric

Samsung Electronics

Kyoto Univ. Tohoku Univ. Etron Technology

Toshiba

Mitsubishi Electric Fuiitsu Laboratories

NEC Sharp

NTT Electronics

Sony

Sanyo Electric

#### NORTH AMERICA/EUROPE

Co-Chair:

Shekhar Borkar Members: Asad Abidi

Jose Alvarez Kamran Azadet

**Bernhard Boser**

Jim Bowles

Ching-Te Chuang

Larry DeVito

**Bruce Gieseke** Peter Gillingham Jim Goodman **Tord Haulin**

Mark Horowitz Stephen Kosonocky

Wai Lee

Wah Kit Loh Lisa Dron McIlrath Gitty Nasserbakht

Peter Poechmueller

Harry Pon Behzad Razavi **David Scott Greg Taylor**

Intel

University of California

Motorola

Agere Systems University of California

AMD **IBM**

**Analog Devices**

AMD **MOSAID** Chrvsalis-ITS Optillion

Stanford University

**IBM**

Texas Instruments Texas Instruments

Massachusetts Institute of Technology

Proxim

Infineon Technologies

Intel

University of California Texas Instruments

Intel

# **CONTENTS**

# Thursday, June 14

# Session 1: Welcome and Plenary Session I [Suzaku]

| Chairpe        | rsons:     | M. Yamashina, <i>NEC</i> S. Borkar, <i>Intel</i>                                                                                                                                                                     |          |

|----------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 8:30           | 1-1        | Welcome and Opening Remarks                                                                                                                                                                                          |          |

| 8:45           | 1-2        | D. Scott Digital Vision Chips and High-Speed Vision Systems (Invited)                                                                                                                                                | 4        |

| 9:30           | 1-3        | M. Ishikawa and T. Komuro BSIM Model for Circuit Design Using Advanced Technologies (Invited)C. Hu                                                                                                                   | 1<br>5   |

| Sessio         | n 2: RF    | Front End I [Suzaku]                                                                                                                                                                                                 |          |

| Chairpe        | rsons:     | T. Mori, <i>Fujitsu Labs</i> .<br>G. Nasserbakht, <i>Proxim</i>                                                                                                                                                      |          |

| 10:35          | 2-1        | Full-CMOS 2.4GHz Wideband CDMA Transmitter and Receiver with Direct Conversion Mixers and DC-Offset CancellationKY. Lee, SW. Lee, Y. Koo, HK. Huh,                                                                   | _        |

| 11:00          | 2-2        | HY. Nam, JW. Lee, J. Park, K. Lee, DK. Jeong and W. Kim Single-Chip IF Transceiver IC with Wide Dynamic Range Variable Gain Amplifiers for Wideband CDMA Applications T. Maruyama, K. Kaneki, K. Takahashi, H. Sato, | 7        |

| 11:25          | 2-3        | T. Iga and N. Kato A OdB-IL, 2140±30 MHz Bandpass Filter Utilizing Q-Enhanced Spiral Inductors in                                                                                                                    | 11       |

| 11:50          | 2-4        | Standard CMOS                                                                                                                                                                                                        | 15<br>19 |

| Sessio         | n 3: Hi    | gh Speed Circuits [Suzaku I]                                                                                                                                                                                         |          |

| Chairpe        | rsons:     | M. Motomura, NEC J. Goodman, Chrysalis-ITS                                                                                                                                                                           |          |

| 13:45          | 3-1        | Robustness of sub-70nm Dynamic Circuits: Analytical Techniques and Scaling                                                                                                                                           |          |

| 14:10          | 3-2        | TrendsM. Anders, R. Krishnamurthy, R. Spotten and K. Soumyanath A 0.13 µm 6GHz 256x32b Leakage-tolerant Register FileR. Krishnamurthy,                                                                               | 23       |

| 14:35<br>15:00 | 3-3<br>3-4 | A. Alvandpour, G. Balamurugan, N. Shanbhag, K. Soumyanath and S. Borkar 480ps 64-bit Race Logic Adder                                                                                                                | 25<br>27 |

|                |            | A. Alvandpour, R. Krishnamurthy, K. Soumyanath and S. Borkar                                                                                                                                                         | 29       |

# Session 4: High Performance DRAM [Suzaku II]

| Chairpei | rsons:  | C. Kim, Samsung Electronics<br>H. Pon, Intel                                                                                                                                                                                   |    |  |  |  |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|

| 13:45    | 4-1     | A Cell Transistor Scalable Array Architecture for High-Density DRAMs  D. Takashima and H. Nakano                                                                                                                               | 31 |  |  |  |

| 14:10    | 4-2     | Bit Line Coupling Scheme and Electrical Fuse Circuit For Reliable Operation of High                                                                                                                                            |    |  |  |  |

| 14:35    | 4-3     | Density DRAMK. Lim, S. Kang, J. Choi, J. Joo, Y. Lee, J. Lee, S. Cho and B. Ryu An Area-Efficient 2GB/s 256Mb Packet-based DRAM with Daisy-Chained Redundancy SchemeB-S. Moon, J-W. Chai, J-S. Kim, S-M. Yim, S-A. Kim, C. Kim | 33 |  |  |  |

| 15:00    | 4-4     | and S-I. Cho<br>A 66-400 MHz, Adaptive-Lock-Mode DLL Circuit with Duty-Cycle Error Correction                                                                                                                                  | 35 |  |  |  |

| 10.00    |         | Y. Okuda, M. Horiguchi and Y. Nakagome                                                                                                                                                                                         | 37 |  |  |  |

| Sessio   | n 5: PL | Ls and Frequency Synthesizers [Suzaku III]                                                                                                                                                                                     |    |  |  |  |

| Chairpe  | rsons:  | T. Kamei, <i>Oki Electric</i> G. Nasserbakht, <i>Proxim</i>                                                                                                                                                                    |    |  |  |  |

| 13:45    | 5-1     | A Stabilization Technique for Phase-Locked Frequency Synthesizers                                                                                                                                                              | 39 |  |  |  |

| 14:10    | 5-2     | A Fully-Integrated CMOS Frequency Synthesizer with Charge-Averaging Charge Pump and Dual-Path Loop Filter for PCS- and Cellular-CDMA Wireless Systems Y. Koo, H. Huh, Y. Cho, J. Lee, J. Park, K. Lee, DK. Jeong and W. Kim    | 43 |  |  |  |

| 14:35    | 5-3     | 1-GHz and 2.8-GHz CMOS Injection-locked Ring Oscillator Prescalers                                                                                                                                                             |    |  |  |  |

| 15:00    | 5-4     | R.J. Betancourt-Zamora, S. Verma and T.H. Lee Automatic Calibration of Modulated $\Sigma$ - $\Delta$ Frequency SynthesizersD.R. McMahill                                                                                       | 47 |  |  |  |

|          |         | and C.G. Sodini                                                                                                                                                                                                                | 51 |  |  |  |

| Sessio   | n 6: De | esign Optimizations and New Technologies [Suzaku I]                                                                                                                                                                            |    |  |  |  |

| Chairpe  | ersons: | H. Kabuo, <i>Matsushita Electric</i><br>S. Borkar, <i>Intel</i>                                                                                                                                                                |    |  |  |  |

| 15:45    | 6-1     | Autonomous-Decentralized Low-power System LSI Using Self-Instructing Predictive Shutdown Method T. Shimizu, F. Arakawa and T. Kawahara                                                                                         | 55 |  |  |  |

| 16:10    | 6-2     | ASIC Design Methodology with On-Demand Library GenerationH. Onodera,                                                                                                                                                           |    |  |  |  |

| 16:35    | 6-3     | M. Hashimoto and T. Hashimoto Scaling trends of Cosmic Rays induced Soft Errors in static latches beyond 0.18μm                                                                                                                | 57 |  |  |  |

|          | C 4     | T. Karnik, B. Bloechel, K. Soumyanath, V. De and S. Borkar                                                                                                                                                                     | 61 |  |  |  |

| 17:00    | 0-4     | Single-Electron Pass-Transistor Logic and its Application to a Binary Adder Y. Ono and Y. Takahashi                                                                                                                            | 63 |  |  |  |

|          |         |                                                                                                                                                                                                                                |    |  |  |  |

# Session 7: Memory Redundancy [Suzaku II]

| Chairpe | ersons:  | M. Hiraki, <i>Hitachi</i> D. Scott, <i>Texas Instruments</i>                                                                                                                                                           |          |

|---------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 15:45   | 7-1      | A Post-Package Bit-Repair Scheme Using Static Latches with Bipolar-Voltage Programmable Antifuse Circuit for High-Density DRAMs KS. Min, JT. Park, SP. Lee, YH. Kim, TH. Yang, JD. Joo, KM. Lee, JK. Wee and JY. Chung | 67       |

| 16:10   | 7-2      | A New Column Redundancy Scheme for Yield Improvement of High Speed DRAMs with Multiple Bit Pre-fetch StructureJG. Lee, YH. Jun, KH. Kyung, C. Yoo,                                                                     |          |

| 16:35   | 7-3      | YH. Cho and Sl. Cho A system LSI memory redundancy technique using an ie-Flash (inverse-gate-electrode flash) programming circuit M. Yamaoka, K. Yanagisawa, S. Shukuri,                                               | 69       |

|         |          | K. Norisue and K. Ishibashi                                                                                                                                                                                            | 71       |

| Sessio  | on 8: Va | ariable Gain Amplifiers [Suzaku III]                                                                                                                                                                                   |          |

| Chairpe | ersons:  | A. Wada, Sanyo Electric<br>K. Azadet, Agere Systems                                                                                                                                                                    |          |

| 15:45   | 8-1      | A 50-MHz 98-dB Dynamic-Range dB-Linear Programmable-Gain Amplifier with 2-dB Gain Steps for 3-V Power Supply                                                                                                           | 70       |

| 16:10   | 8-2      | A Temperature Stable CMOS Variable Gain Amplifier with 80-dB Linearly Controlled Gain Range                                                                                                                            | 73<br>77 |

| 16:35   | 8-3      | A Variable Gain IF Amplifier with -67dBc $IM_3$ -Distortion at $1.4V_{pp}$ Output in $0.25\mu m$ CMOS                                                                                                                  | 81       |

| 20:00   | Rump     | Sessions:                                                                                                                                                                                                              |          |

| Organiz | ers:     | M. Hiraki, <i>Hitachi</i> B. Gieseke, <i>AMD</i>                                                                                                                                                                       |          |

|         | R-1      | Will Start-Ups Outperform Big Companies?                                                                                                                                                                               | 83       |

|         | R-2      | Power Supply for Future System LSIsS. Kosonocky, T. Kuroda, M. Matsui                                                                                                                                                  | 83       |

|         | R-3      | Diverse DRAM Architectures: Why and Who Wins? H. Pon, M. Motomura, B. Martino                                                                                                                                          | 84       |

|         | J-R      | Which Features of an IC Technology will Benefit Radio SOC? H. Iwai, S. Shichijo,                                                                                                                                       | Ω/       |

# Friday, June 15

## Session 9: Plenary Session II [Shunju]

| Chairpe | rsons:  | M. Yamashina, <i>NEC</i> S. Borkar, <i>Intel</i>                                                                                                                                                                                                                                                                                                                                                                                                                               |            |

|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 8:30    | 9-1     | Development Trends of LTPS TFT LCDs for Mobile Applications (Invited)                                                                                                                                                                                                                                                                                                                                                                                                          | 0.5        |

| 9:15    | 9-2     | K. Yoneda, R. Yokoyama and T. Yamada Electronics for DLP <sup>TM</sup> Technology Based Projection Systems (Invited)                                                                                                                                                                                                                                                                                                                                                           | 85<br>91   |

| Sessio  | n 10: N | /lultimedia and Networking [Shunju]                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

| Chairpe | rsons:  | M. Matsui, <i>Toshiba</i><br>CT. Chuang, <i>IBM T.J. Watson Research Ctr.</i>                                                                                                                                                                                                                                                                                                                                                                                                  |            |

| 10:20   | 10-1    | A 120mW Embedded 3D Graphics Rendering Engine with 6Mb Logically Local Frame-Buffer and 3.2GByte/s Run-time Reconfigurable Bus for PDA-Chip  R. Woo, CW. Yoon, J. Kook, SJ. Lee, K. Lee, YH. Park and HJ. Yoo                                                                                                                                                                                                                                                                  | 95         |

| 10:45   | 10-2    | Low Power Motion Compensation Block IP with embedded DRAM Macro for Portable Multimedia Applications CW. Yoon, J. Kook, R. Woo, SJ. Lee, K. Lee                                                                                                                                                                                                                                                                                                                                | 99         |

| 11:10   | 10-3    | and HJ. Yoo  Dynamically Reconfigurable Logic LSI - PCA-1H. Ito, R. Konishi, H. Nakada,                                                                                                                                                                                                                                                                                                                                                                                        |            |

| 11:35   | 10-4    | K. Oguri, A. Nagoya, N. Imlig, K. Nagami, T. Shiozawa and M. Inamori A 1GHz Power Efficient Single Chip Multiprocessor System For Broadband Networking ApplicationsS. Santhanam, R. Allmon, R. Blake, N. Bunger, B. Campbell, M. Carlson, Z. Chen, J. Cheng, T. Do, D. Dobberpuhl, J. Ingino, D. Kidd, D. Kruckemyer, J. Lee, D. Murray, S. Nishimoto, L. O'Donnell, M. Oykher, M. Panich, M. Pearce, D. Priore, R. Rogenmoser, D. Suh, V. Sundaresan, E. Supnet, V.V. Kaenel, | 103        |

|         |         | G. Yee and C. Vo                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 107        |

| Sessio  | n 11: F | RF VCOs [Shunju I]                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

| Chairpe | rsons:  | DK. Jeong, <i>Seoul National Univ</i> .<br>G. Taylor, <i>Intel</i>                                                                                                                                                                                                                                                                                                                                                                                                             |            |

| 13:30   | 11-1    | A 1.57 GHz Fully integrated Very Low Phase Noise Quadrature VCO                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| 13:55   | 11-2    | P. Vancorenland and M. Steyaert An optimally coupled 5 GHz quadrature LC oscillator P. van de Ven,                                                                                                                                                                                                                                                                                                                                                                             |            |

| 14:20   | 11-3    | A Highly-Tunable 12 GHz Quadrature LC-VCO in SiGE BiCMOS Process                                                                                                                                                                                                                                                                                                                                                                                                               | 115        |

| 14:45   | 11-4    | A.L. Coban, K. Ahmed and C. Chang A 1.8 GHz CMOS VCO with Reduced Phase Noise P. Andreani and H. Sjöland                                                                                                                                                                                                                                                                                                                                                                       | 119<br>121 |

# Session 12: Nonvolatile Memories [Shunju II]

| Chairpe | ersons: | K. Kotani, <i>Tohoku Univ.</i><br>J. Bowles, <i>AMD</i>                                                                                                                        |            |

|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 13:30   | 12-1    | A Novel Sensing Scheme for a MRAM with a 5% MR RatioK. Yamada, N. Sakai,                                                                                                       |            |

| 13:55   | 12-2    | Y. Ishizuka and K. Mameno A Pulse-Tuned Charge Controlling Scheme for Uniform Main and Reference Bitline Voltage Generation on 1T1C FeRAM HB. Kang, HW. Kye, DJ. Kim, GI. Lee, | 123        |

| 14:20   | 12-3    | JH. Park, JK. Wee, SS. Lee, SK. Hong, NS. Kang and JY. Chung A Bit-Line GND Sense Technique for Low-Voltage Operation FeRAM                                                    | 125        |

| 14:45   | 12-4    | and M. Aoki  A 512 Kbit low-voltage NV-SRAM with the size of a conventional SRAM  T. Miwa, J. Yamada, H. Koike, T. Nakura, S. Kobayashi, N. Kasai and H. Toyoshima             | 127<br>129 |

| Sessio  | n 13:   | Voltage and Current Generation [Shunju III]                                                                                                                                    |            |

| Chairpe | ersons: | Y. Ohtomo, NTT Electronics<br>S. Kosonocky, IBM, T.J. Watson Research Center                                                                                                   |            |

| 13:30   | 13-1    | An Efficient Digital Sliding Controller for Adaptive Power Supply Regulation                                                                                                   |            |

| 13:55   | 13-2    | J. Kim and M. Horowitz  A 1.8V Single-Inductor Dual-Output Switching Converter for Power Reduction                                                                             | 133        |

| 14:20   | 13-3    | Techniques                                                                                                                                                                     | 137        |

| 14:45   | 13-4    | Sub-1 V Process-Compensated MOS Current Generation Without Voltage Refer-                                                                                                      | 141        |

| Sessio  | n 14·   | ence                                                                                                                                                                           | 143        |

| 000010  |         |                                                                                                                                                                                |            |

| Chairpe | rsons:  | Y. Ohtomo, <i>NTT Electronics</i><br>A. Abidi, <i>Univ. of California</i>                                                                                                      |            |

| 15:30   | 14-1    | A Single-Chip 12.5Gbaud Transceiver for Serial Data Communication                                                                                                              |            |

| 15:55   | 14-2    | An 84-mW 4-Gb/s Clock and Data Recovery Circuit for Serial Link Applications                                                                                                   | 145        |

| 16:20   | 14-3    | MJ.E. Lee, W.J. Dally, J.W. Poulton, P. Chiang and S.F. Greenwood An SOI CMOS LVDS Driver and Receiver Pair                                                                    | 149        |

| 16:45   | 14-4    | A 15-GHz Wireless Interconnect Implemented in a 0.18-μm CMOS Technology Using Integrated Transmitters, Receivers, and Antennas B.A. Floyd, CM. Hung                            | 153        |

|         |         | and K.K. O                                                                                                                                                                     | 155        |

# Session 15: Emerging Technology [Shunju II]

| Chairpe | rsons:  | M. Hiraki <i>, Hitachi</i><br>B. Gieseke <i>, AMD</i>                                                                                                          |     |

|---------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 15:30   | 15-1    | Effects of Power-Supply Parasitic Components on Substrate Noise Generation in Large-Scale Digital Circuits M. Nagata, T. Ohmoto, Y. Murasaka, T. Morie         |     |

|         |         | and A. Iwata                                                                                                                                                   | 159 |

| 15:55   | 15-2    | Parametric Yield Enhancement System via Circuit Level Device Optimization using Statistical Circuit Simulation M. Miyama, S. Kamohara, K. Okuyama and Y. Oji   | 163 |

| 16:20   | 15-3    | A Floating-Body Charge Monitor Circuit for Partially Depleted SOI CMOS                                                                                         |     |

|         |         | J.B. Kuang, M.J. Saccamango and S. Ratanaphanyarat                                                                                                             | 167 |

| Sessio  | n 16:   | Sensor and Filters [Shunju III]                                                                                                                                |     |

| Chairpe | ersons: | A. Hyogo, <i>Science Univ. of Tokyo</i><br>H. Pon, <i>Intel</i>                                                                                                |     |

| 15:30   | 16-1    | A Pixel-Level Automatic Calibration Circuit Scheme for Sensing Initialization of a Capacitive Fingerprint Sensor LSI H. Morimura, S. Shigematsu, T. Shimamura, |     |

|         |         | K. Machida and H. Kyuragi                                                                                                                                      | 171 |

| 15:55   | 16-2    | A 200MHz 7th-order Equiripple Continuous-Time Filter by design of nonlinearity                                                                                 |     |

|         |         | suppression in 0.25μm CMOS ProcessT. Morie, H. Fujiyama and S. Dosho                                                                                           | 175 |

| 16:20   | 16-3    | A Micropower Log-Domain Filter Using Enhanced Lateral PNPs in a $0.25 \mu m$ CMOS                                                                              |     |

|         |         | Process                                                                                                                                                        | 179 |

# Saturday, June 16

# Session 17: Clock Distributions and Bus Drivers [Shunju I]

| Chairp       | ersons: | K. Kobayashi, <i>Kyoto Univ.</i><br>G. Taylor, <i>Intel</i>                                                                                                                                                                  |            |

|--------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 8:30<br>8:55 |         | A Low-Swing Clock Double-Edge Triggered Flip-FlopC. Kim and SM. Kang On-die Clock Jitter Detector for High Speed Microprocessors R. Kuppuswamy,                                                                              |            |

| 9:20         | 17-3    | K. Callahan, K. Wong, D. Ratchen and G. Taylor P-boosted Source Followers: A Robust Energy-efficient Bus Driver Technique                                                                                                    |            |

| 9:45         | 17-4    | R. Krishnamurthy, K. Soumyanath and D. Ayers Two schemes to reduce interconnect delay in bi-directional and uni-directional buses                                                                                            |            |

| Sessio       | on 18·  | Passive Elements and Test [Shunju II]                                                                                                                                                                                        | 193        |

| 00001        | JII 10. | rassive Elements and Test (Snunju II)                                                                                                                                                                                        |            |

| Chairpe      | ersons: | M. Motomura, <i>NEC</i><br>K. Azadet, <i>Agere Systems</i>                                                                                                                                                                   |            |

| 8:30         | 18-1    | Accurate Analysis of On-Chip Inductance Effects and Implications for Optimal                                                                                                                                                 |            |

| 8:55         | 18-2    | Silicon Integrated High Performance Inductors in a 0.18   mm CMOS Technology for MMIC HM. Hsu, JG. Su, SC. Wong, YC. Sun, CY. Chang, TY. Huang, C.C. Tsai, C.H. Lin, R.S. Liou, R.Y. Chang, T.H. Yeh, C.H. Chen, C.F. Huang, | 195        |

| 9:20         | 18-3    | H.D. Huang and C.W. Chen Design and Characterization of Vertical Mesh Capacitors in Standard CMOS                                                                                                                            | 199        |

| 9:45         | 18-4    | A JTAG Based AC Leakage Self Test T. Rahal-Arabi and G. Taylor                                                                                                                                                               | 201<br>205 |

| Sessio       | n 19: / | ADC and Track/Hold [Shunju III]                                                                                                                                                                                              |            |

| Chairpe      | rsons:  | T. Mori, <i>Fujitsu Labs.</i><br>CT. Chuang, <i>IBM T.J. Watson Research Center</i>                                                                                                                                          |            |

| 8:30         | 19-1    | A 1V operational, 20Ms/s and 57dB of S/N, Current-mode CMOS Sample-and-hold                                                                                                                                                  |            |

| 8:55         | 19-2    | An 8-bit 30MS/s 18mW ADC with 1.8V single power supplyT. Sigenobu, M. Ito                                                                                                                                                    |            |

| 9:20         | 19-3    | A 12-bit Mismatch-Shaped Pipeline A/D Converter                                                                                                                                                                              | 209        |

| 9:45         | 19-4    | An 8-GHz Bandwidth 1-GS/s GaAs HBT Dual Track-and-Hold                                                                                                                                                                       |            |

|              |         | o and the restriction                                                                                                                                                                                                        |            |

# Session 20: Low Power Design [Shunju I]

| Chairpe | ersons:   | K. Seno, <i>Sony</i><br>S. Borkar, <i>Intel</i>                                                                                                                                                                             |     |

|---------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 10:30   | 20-1      | Comparative Performance, Leakage Power and Switching Power of Circuits in 150nm PD-SOI and Bulk Technologies Including Impact of SOI History Effect                                                                         |     |

| 10:55   | 20-2      | S. Narendra, J. Tschanz, A. Keshavarzi, S. Borkar and V. De A 0.5V Power-Supply Scheme for Low Power LSIs using Multi-Vt SOI CMOS Tech-                                                                                     |     |

| 11:20   | 20-3      | nology                                                                                                                                                                                                                      |     |

| 11:45   | 20-4      | Pump Circuit H. Notani, M. Koyama, R. Mano, H. Makino and Y. Matsuda A 63 µW-Standby-Power Microcontroller with On-Chip Hybrid Regulator Scheme                                                                             |     |

| Sessio  | nn 21· I  | Embedded RAMs [Shunju II]                                                                                                                                                                                                   | 225 |

| 000010  | J., 21. L | -mbedded NAMS (Shunju II)                                                                                                                                                                                                   |     |

| Chairpe | ersons:   | N.C.C. Lu, Etron Technology<br>J. Bowles, AMD                                                                                                                                                                               |     |

| 10:30   | 21-1      | Quasi-Worst-Condition Built-In-Self-Test Scheme for 4-Mb Loadless CMOS Four-Transistor SRAM MacroK. Takeda, Y. Aimoto, K. Nakamura, S. Masuoka,                                                                             |     |

| 10:55   | 21-2      | K. Ishikawa, K. Noda, T. Takeshima and T. Murotani A 800MHz Single Cycle Access 32entry Fully Associative TLB With A 240ps Access Match Circuit                                                                             |     |

| 11:20   | 21-3      | cess Match Circuit                                                                                                                                                                                                          |     |

| 11:45   | 21-4      | <ul> <li>KM. Lee, TH. Yang, JY. Jung and HJ. Yoo</li> <li>A 6.25ns Random Access 0.25μm Embedded DRAM P. DeMone, M. Dunn,</li> <li>D. Haerle, JK. Kim, D. Macdonald, P. Nyasulu, D. Perry, S. Smith, T. Wojcicki</li> </ul> |     |

|         |           | and Z. Zhang                                                                                                                                                                                                                | 237 |

| Sessio  | on 22: F  | RF Front End II [Shunju III]                                                                                                                                                                                                |     |

| Chairpe | ersons:   | T. Miki, <i>Mitsubishi Electric</i><br>J. Goodman, <i>Chrysalis-ITS</i>                                                                                                                                                     |     |

| 10:30   | 22-1      | A Fully-Integrated 900-MHz CMOS Wireless Receiver with On-Chip RF and IF Filters and 79-dB Image RejectionC. Guo, CW. Lo, YW. Choi, I. Hsu, T. Kan,                                                                         |     |

| 10:55   | 22-2      | D. Leung, A. Chan and H.C. Luong A Single-Chip 2.4GHz Direct-Conversion CMOS Transceiver with GFSK Modem for Bluetooth Application SW. Lee, KY. Lee, E. Song, YJ. Jung, H. Jeong,                                           | 241 |

| 11:20   | 22-3      | JM. Kim, HJ. Lim, JW. Lee, J. Park, K. Lee, SI. Chae, DK. Jeong and W. Kim Concurrent Dual-Band CMOS Low Noise Amplifiers and Receiver Architectures                                                                        | 245 |

| 11:45   | 22-4      | H. Hashemi and A. Hajimiri Fully Integrated 2.2mW CMOS Front-End for a 900 MHz Zero-IF Wireless Receiver                                                                                                                    | 247 |

|         |           | S Mahdayi and A A Abidi                                                                                                                                                                                                     | 251 |

# 2001 VLSI Circuits Short Course "Physical Design for Low-Power and High-Performance Microprocessor Circuits"

#### Wednesday, June 13 (Suzaku)

| Organiz | ers: M. Matsui, <i>Tos</i><br>G. Taylor, <i>Inte</i> | shiba<br>el                           |                               |

|---------|------------------------------------------------------|---------------------------------------|-------------------------------|

| 9:30    | Opening                                              |                                       |                               |

| 9:40    | Overview of Physica                                  | al Design                             |                               |

| 10:00   | Interconnect Design                                  | of Athlon™ Microprocessors            | J. Moench, AMD                |

| 11:00   | Substrate-Bias Tech                                  | niques for SH4                        | K. Ishibashi, Hitachi         |

| 12:00   | Lunch                                                |                                       |                               |

| 13:15   | High-Performance S<br>to Circuits                    | Ol Digital Design: from Devices       | CT. K Chuang, IBM             |

| 14:15   | Low-Power and High<br>General Purpose DS             | n-Performance Circuit Design of<br>Ps | H. Takahashi, <i>TI-Japan</i> |

| 15:15   | Break                                                |                                       |                               |

| 15:30   | Embedded DRAM Some MPEG4 Codec LSIs                  | OCs and its Application for           | S. Miyano, <i>Toshiba</i>     |

| 16:30   | Circuit Design of XS                                 | cale™ Microprocessors                 | L. T. Clark, Intel            |

| 17:30   | Conclusion                                           |                                       |                               |

#### **Digital Vision Chips and High-Speed Vision Systems**

Masatoshi Ishikawa and Takashi Komuro

Department of Information Physics and Computing, Graduate School of Information Science and Engineering, The University of Tokyo 7-3-1 Hongo, Bunkyo-ku, Tokyo 113-8656, Japan

#### **Abstract**

Conventional image processing has a critical limit of frame rate derived from serial transmission of the video signal. In order to overcome the limit, fully parallel processing architecture without scanning has been proposed. In this paper, vision chips with digital circuits and high speed application systems developed in our laboratory will be described.

#### Vision Chip

In the real world, sensory information is parallel. Especially visual information is high dimensional (3D or 4D) parallel information and is captured and processed parallelly in human retina. However, in the engineering world, a vision system uses serial transmission of video signal from an image sensor such as CCD to a processor. In such a system, transmission speed is limited on the video signal such as NTSC (33ms).

On the other hand, a device called vision chip has been proposed, in which photo detectors (PDs) and processing elements (PEs) are connected in each pixel. It captures and processes images parallelly without serial transmission. Therefore, not only it realizes high speed processing but the benefits of being a system VLSI are expected.

#### **Design Concept**

Most of existing research of vision chip use analog circuits in processing element [1-4]. Analog circuits cost lower area and therefore are easier to integrate than digital ones. However, they have demerits that the functions are almost fixed once designed. As a result, many special purpose chips have been developed but there have been few chips for general purpose. To make general purpose vision chip which can process various algorithms on one chip, it is necessary to develop a programmable processing element designed in digital circuits. We call such vision chip as digital vision chip.

On the basis of such concept, Ishikawa et al. proposed an architecture of a digital vision chip[5]. Using a scaled-up model of the vision chip, various application systems have been developed. These systems have realized high speed visual feedback at a sampling period of 1ms.

Research on digital vision chips has been done at a few other laboratories worldwide. In France, a compact digital vision chip called the programmable artificial retina has been proposed, and the researchers have successfully developed chips of 65x76 pixel[6] and 128x128 pixel. In Sweden a unique digital vision chip based on their near-sensor image processing concept was proposed and a 32x32 pixel chip has been developed[7].

One of the problems inherent in designing a digital vision chip is the difficulty of integrating many pixels on a

single chip since the digital approach requires more circuits than analog. Therefore, the vision chips mentioned above have taken approach to place a priority on either compactness or performance of the PE, not both.

However, in the background of rapid progress of semiconductor integration technology in recent years, general purpose digital vision chip has become a realizable technology.

Of course, to integrate a large number of pixels in one chip, we have to make an effort to design a compact PE, that is, a design of PE whose area is as small as possible is needed.

#### **Architecture**

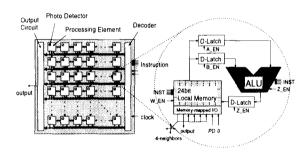

Following the design concept above, Komuro et al. designed a new architecture S<sup>3</sup>PE (Simple and Smart Sensory Processing Element) [8] which aimed at further high integration. Fig. 1. shows the architecture of S<sup>3</sup>PE.

Fig. 1 Architecture of Genaral Purpose Vision Chip

Each PE has an ALU which has bit-serial operation structure and 24 bit local memory in which each bit can be randomly accessed. It communicates with the photo detector and the neighbor PEs via 8 channel I/O which is mapped to memory address space.

The ALU has a simple structure consisting of a full-adder, a carry register and some multiplexers. It can process one of 10 kinds of logical and 8 kinds of arithmetic operations at each cycle. Bit-serial operation is a method that performs each bit of multi-bit operations in order. It is slower than bit-parallel operation but has merits of compact circuits and capability of variable bit length data operation.

In the local memory, 24 bit random access memory (RAM) and 8 bit I/O ports are allocated to the same address space. I/O ports are connected to up, down, left and right PEs, input from the sensor, and zero signal. Introducing the memory mapped I/O, all processing including not only operations but also I/O operation is performed by accessing the local memory.

As a result, the instruction code has a simple form; all

instructions consist of read address A, B (5 bits each), operation code (5 bits), and write address (5 bits). This 20 bit instruction is divided into four steps, and is transmitted and processed in order.

The A/D conversion of the analog signal from the photo detector is performed by measuring the time that the voltage of the capacitor discharged by the photo current crosses the threshold voltage. Using the PE as a counter, A/D conversion is realized without increasing circuit area.

These design policies give priority to the integrity over other performance such as processing speed. They depend on the idea that the power of massive parallelism is enourmous and even if the performance of each PE is a little low, the total performance is still high.

#### **Early Vision Algorithms**

We implemented some early vision algorithms for evaluating the performance of this vision chip. Tablel shows the steps and processing time. This table shows that the vision chip can process most of early vision programs at the order of  $\mu s$ , which is much higher than conventional image processing systems.

Table1 Steps and processing time of early vision algorithms

| Algorirhm                 | steps | time   |

|---------------------------|-------|--------|

| Edge Detection (binary)   | 8     | 0.64µs |

| Smoothing (binary)        | 14    | 1.1µs  |

| Edge Detection (6bit)     | 47    | 3.8µs  |

| Smoothing (6bit)          | 41    | 3.3µs  |

| Thinning (binary) *       | 12    | 0.96µs |

| Convolution (6bit)        | 986   | 80µs   |

| Poisson Equation (6bit) * | 65    | 5.2µs  |

<sup>\*</sup> repeating operation

# VLSI implementation and System Development

Based on the architecture, we have designed a schematic and a custom layout using  $0.35\mu m$  CMOS process[9]. The number of transistor per PE is about 400 and the PE area is as small as  $105\mu m$  x  $105\mu m$ . Using this design, we have developed a prototype chip of 64x64 pixels. Fig. 2 shows the chip photo.

Fig.2 Chip Photo of General Purpose Vision Chip

To make a whole system using the vision chip, we have developed a controller which transmit instructions to the vision chip at the order of 100ns and also manage program control such as conditional jump and loop. The vision chip, controller, and memory are the components of the system.

We have also been developing a C-like programming language of the system (SPE-C) and its compiler. On the development environment, users can simulate and check their programs in a PC or a workstation.

# Global Feature Extraction Circuit for Digital Vision Chip

One of the important issues of the vision chip we have to consider is how to output. In principle, the parallel processing in the PE array is transformation from 2D pattern to 2D pattern. However, if we try to output the whole 2D pattern via pins, we face again the I/O bottleneck problem which we solved for the input.

In a real application which requires high speed control, the final output needed is not a pattern but some feature extracted from the pattern in most cases. For example, visual feedback control of the robot gets the position of the target from the sensor and gives feedback to the actuator. In this case, pattern information is only an intermediate expression and the output of the vision chip can be scalar information.

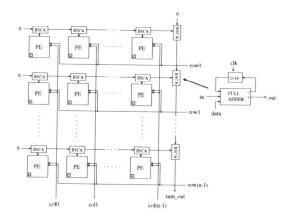

For such purpose, we designed a global feature extraction circuit which calculates moment at high speed. Moment is a value which is widely used in a real application. This circuit has some features: i) it consists of digital circuits, ii) circuit scale is small, iii) it can calcurate moments at high speed iv) it is easy to implement to VLSI. Fig. 3 shows the configuration.

Fig. 3 Moment Extraction Circuit

# High Speed Target Tracking Vision Chip

The digital vision chip based on S<sup>3</sup>PE is designed putting emphasis on generality to answer to various uses. Therefore, the circuit scale becomes large to some extent though we have made an effort to design a compact circuit. However, there are some applications which require higher resolution. Especially in case to monitor a large range of view or track more than one objects, high resolution sensor is desired.

Then, we propose a new vision chip which aims to improve the resolution and speed by focusing the purpose of the chip to a specific task [10]. In this design we have chosen target tracking as the task with which we have