# 1994 SYMPOSIUM ON VLSI CIRCUITS

DIGEST OF TECHNICAL PAPERS

# 1994 SYMPOSIUM ON VLSI CIRCUITS

DIGEST OF TECHNICAL PAPERS

## 1994 Symposium on VLSI Circuits

## **Digest of Technical Papers**

Copyright and Reprint Permission:

Abstracting is permitted with credit to the source. Libraries are permitted to photocopy beyond the limits of U.S. copyright law for private use of patrons those articles in this volume that carry a code at the bottom of the first page, provided the per-copy fee indicated in the code is paid through the Copyright Clearance Center, 27 Congress St., Salem, MA 01970. Instructors are permitted to photocopy isolated articles for non-commercial classroom use without fee. For other copying, reprint or republication permission, write to IEEE Copyrights Manager, IEEE Service Center, 445 Hoes Lane, P.O. Box 1331, Piscataway, NJ 08855-1331. All rights reserved. Copyright © 1994 by the Institute of Electrical and Electronics Engineers, Inc.

#### PRINTED IN THE UNITED STATES OF AMERICA

Publisher: John H. Wuorinen, Castine, ME 04421, USA

IEEE Cat. No. 94CH3434-8 JSAP Cat. No. AP 941212 ISBN 0-7803-1918-4 Softbound ISBN 0-7803-1919-2 Casebound ISBN 0-7803-1920-6 Microfiche Library of Congress Number 94-75833

Copies of this Digest can be purchased from:

IEEE Service Center Single Publication Sales Unit

445 Hoes Lane, Piscataway, NJ 08854, USA

Inside Japan

Business Center for Academic Societies Japan

5-16-9, Honkomagome 3-chome, Bunkyo-ku, Tokyo 113, Japan

## **FOREWORD**

Welcome to Hawaii for the 1994 Symposium on VLSI Circuits

The Symposium on VLSI Circuits is sponsored by the IEEE Solid-State Circuits Council and the Japan Society of Applied Physics in cooperation with the Institute of Electronics, Information and Communication Engineers of Japan. The technical program of the eighth Circuits Symposium clearly attests to the fact that this meeting is now perceived as one of the major international forums for the discussion of important advances in VLSI circuit design. Contained herein are 58 papers selected from the 150 papers submitted to the Program Committee from 12 different countries around the world.

The Symposium features four invited talks spanning its entire scope. The talks cover the IRIDIUM Personal Communication System, ATM in Broadband-ISDN Communication Systems, Multichip Module Technologies, and Design Tradeoffs in Advanced Microprocessor Architectures. We expect lively discussions at our five evening rump sessions, which include a joint Circuits and Technology Session on Low Power/Low Voltage Technologies.

The contributed papers that make up the bulk of this conference represent significant advances in circuit design as applied to memories, processors, communication circuits, and analog and digital signal processing. Future design problems are clearly discussed and possible solutions are given. In addition, advanced solutions to the requirements of today are described. We expect the technical content of the program and the beauty of Hawaii to make the Symposium a worthwhile event for every attendee.

The excellent program owes much to the outstanding efforts of the Technical Program Committees, under the leadership of the Program Chairman, Kevin O'Connor, and Program Co-Chairman, Atsushi Iwata. The Committee members, leaders in the field of Circuit Design, have solicited strong papers and selected and organized them into attractive technical sessions.

Next year, the Symposium will be held in Kyoto, together with the Technology Symposium. We do hope you will attend.

June 1994

Charles Sodini Symposium Chairman

Akihiko Morino Symposium Co-Chairman

### 1994 VLSI CIRCUITS SYMPOSIUM COMMITTEES

Chairman:

Charles Sodini

Massachusetts Institute of Technology

Co-Chairman:

Akihiko Morino

**NEC**

Program Chairman:

Kevin O'Connor

AT&T Bell Laboratories

Program Co-Chairman:

Atsushi Iwata Richard Hester

Hiroshima University Iowa State University

Secretary:

Yasushi Ooi (Publicity)

**NEC**

Publications/Publicity:

Ching-Te Chuang

Masakazu Kakumu

**IBM**

Hiroshi Inoue (Publications)

Oki Electric

Treasurer:

Richard Jaeger

**Auburn University** Toshiba

**Local Arrangements:**

Wayne White

**Hughes Aircraft**

Kiyoshi Yoneda

Sanyo Electric

## **EXECUTIVE COMMITTEES**

IEEE

Chairman:

Pallab Chatterjee

Texas Instruments Hewlett-Packard

Members:

Dirk Bartelink Youssef El-Mansy Richard Jaeger Court Skinner

Intel Corporation **Auburn University**

National Semiconductor Corp.

Lewis Terman

**IBM**

Peter Verhofstadt

Semiconductor Research Corp.

**Bruce Wooley**

Stanford University

**Japan Society of Applied Physics**

Chairman:

Takuo Sugano

Toyo University

Members:

Shojiro Asai Yutaka Hayashi Hitachi Sony

Hajime Ishikawa Fujitsu Laboratories

Susumu Kohyama

Toshiba

Hiroyoshi Komiya

Mitsubishi Electric

Akihiko Morino Hisakazu Mukai

NEC Oki Electric

Minoru Nagata Tetsushi Sakai

Hitachi NTT

Toyoki Takemoto

Matsushita Electric

İ۷

### **TECHNICAL PROGRAM COMMITTEES**

#### NORTH AMERICA/EUROPE

Chairman: Kevin O'Connor AT&T Bell Laboratories

Members: William Bidermann HaL

Robert Brodersen University of California

Ching-Te Chuang IBM

Larry DeVito Analog Devices

Richard Hester Iowa State University

Karl Horninger Siemens

Paul Hurst University of California

John Khoury AT&T Bell Laboratories

Clinton Kuo Motorola Sanjay Mehrotra SunDisk Thao Nguyen IBM

Willy Sansen Katholieke Universiteit Leuven

David Scott Texas Instruments

Luan Tran Micron Semiconductor

Peter Voss Cypress Semiconductor

lan Young Intel Corporation

#### JAPAN/FAR EAST

Co-Chairman: Atsushi Iwata Hiroshima University

Members: Daeje Chin Samsung Electronics

Hisakazu Edamatsu Matsushita Electric

Minoru Fujishima University of Tokyo

Hirohisa Gambe Fujitsu

Takahiro Hanyu Tohoku University

Masayuki Ishikawa NTT

Yoshiyuki Ishizuka Sanyo Electric

Mineo Kaneko Tokyo Institute of Technology

Yoshifumi Masaki Sharp Yoshinobu Nakagome Hitachi Ltd. Itsuo Nakamura Oki Electric

Nicky Lu Etron

Hidetoshi Onodera Kyoto University

Takayasu Sakurai Toshiba

Yasushi Terada Mitsubishi Electric

Hachiro Yamada NEC Futao Yamaguchi Sony Session 1: Welcome and Plenary Session I [Tapa I]

Chairpersons: Kevin O'Connor Atsushi Iwata

AT&T Bell Laboratories Hiroshima University

Session 2: Data Converters [Tapa I]

Chairpersons: J.

J. Khoury

AT&T Bell Laboratories

F. Yamaguchi

Sony

Session 3: Low Power Logic [Tapa II]

Chairpersons:

W. Bidermann

HaL

K. Asada

University of Tokyo

Session 4: Phase-Locked Loops and High-Speed Interfaces [Tapa III]

Chairpersons:

I. Young

Intel

T. Enomoto

Chuo University

Rump Sessions [Honolulu I, II and Iolani I, II, IV]

Session 5: Plenary Session II [Tapa II]

Chairpersons:

Atsushi Iwata

Hiroshima University

Kevin O'Connor

AT&T Bell Laboratories

Session 6: Flash EEPROMs [Tapa II]

Chairpersons:

S. Mehrotra

SunDisk

Y. Terada

Mitsubishi Electric

Session 7: Digital System Chips [Tapa III]

Chairpersons:

T. Nguyen

IBM

H. Edamatsu

Matsushita Electric

Session 8: Dynamic Memory Concepts [Tapa II]

Chairpersons:

D. Scott

Texas Instruments

D. Chin

Samsung Electronics

Session 9: Signal Processing [Tapa III]

Chairpersons:

L. DeVito

Analog Devices

I. Nakamura

Oki

Session 10: SRAM [Tapa I]

Chairpersons:

L. Tran

Micron

T. Sakurai

Toshiba

Session 11: Communication Circuits [Tapa II]

Chairpersons:

R. Brodersen

University of California

M. Ishikawa

NTT

## **CONTENTS**

# Session 1: Welcome and Plenary Session I [Tapa I]

| 1.1 | Opening Remarks                                                                                                             |     |

|-----|-----------------------------------------------------------------------------------------------------------------------------|-----|

| 1.2 | The IRIDIUMTMSM Personal Communication System                                                                               | r 1 |

| 1.3 | ATM in B-ISDN Communication Systems and LSI RealizationT. Koinuma and N. Miyaho                                             | ) 5 |

| Ses | ssion 2: Data Converters [Tapa I]                                                                                           |     |

| 2.1 | A Digital Self Compensation Circuit for High Speed D/A Converters                                                           |     |

|     |                                                                                                                             | 11  |

| 2.2 | A 13-Bit 10-MHz ADC Background-Calibrated with Real-Time Oversampling Calibrator                                            |     |

|     | T-H. Shu, B-S. Song and K. Bacrania                                                                                         | 13  |

| 2.3 | A CMOS 3V 24mW 20MSPS 10bit A/D Converter with Self Calibration Unit                                                        |     |

|     | N. Kumazawa, N. Fukushima, T. Fujiwara, K. Motoyama and N. Akui                                                             | 15  |

| 2.4 | A 1.5V Video-Speed Current-Mode Current-Tree A/D Converter                                                                  |     |

|     | H. Hasegawa, M. Yotsuyanagi, M. Yamaguchi and K. Sone                                                                       | 17  |

| Ses | sion 3: Low Power Logic [Tapa II]                                                                                           |     |

| 3.1 | Power Dissipation Measurements on Recovered Energy Logic                                                                    | 19  |

| 3.2 | A Low Power Complete Charge-Recycling Bus Architecture for Ultra-High Data Rate ULSIsH. Yamauchi, H. Akamatsu and T. Fujita | 21  |

| 3.3 | Half-Swing Clocking Scheme for 75% Power Saving in Clocking Circuitry                                                       |     |

| ••• | H. Kojima, S. Tanaka and K. Sasaki                                                                                          | 23  |

| 3.4 |                                                                                                                             |     |

| J.T | Adiabatic Computing with the 2N-2N2D Logic FamilyA. Kramer, J. Denker, S. Avery, A. Dickinson and T. Wik                    | 25  |

| 2.5 |                                                                                                                             | 20  |

| 3.5 | A GHz MOS Adaptive Pipeline Technique Using Variable Delay Circuits                                                         | 07  |

|     |                                                                                                                             | 27  |

| 3.6 | Data-Dependent Logic Swing Internal Bus Architecture for Ultra-Low-Power LSIs                                               |     |

|     |                                                                                                                             | 29  |

| 3.7 | An Extremely Low-Power Bipolar Current-Mode I/O Circuit for Multi-Gbit/s Interfaces                                         |     |

|     | T. Kawamura, M. Suzuki and H. Ichino                                                                                        | 31  |

| 3.8 | Multiplexer-Based Architecture for High-Density, Low-Power Gate Arrays                                                      |     |

|     | R. Landers and S. Mahant-Shetti                                                                                             | 33  |

## Session 4: Phase-Locked Loops and High-Speed Interfaces [Tapa III]

| 4.1 | A 15-150MHz, All-Digital Phase-Locked Loop with 50-Cycle Lock Time for High-Performance Low-Power MicroprocessorsJ. Lundberg and E. Nuckolls | 05 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------|----|

|     |                                                                                                                                              | 35 |

| 4.2 | A Wide-Bandwidth Low-Voltage PLL for PowerPC™ Microprocessors                                                                                | 27 |

|     |                                                                                                                                              | 37 |

| 4.3 | Analog versus Digital Control of a Clock Synchronizer for 3Gb/s Data with 3.0V Differential ECL                                              | 39 |

| 4.4 | A Pseudo-Synchronous Skew-Insensitive I/O Scheme for High Bandwidth Memories                                                                 |    |

|     | S. Kim, K. Lee, D. Jeong and Y. Choi                                                                                                         | 41 |

| 4.5 | A CMOS 500 Mbps/pin Synchronous Point to Point Link Interface                                                                                |    |

|     | S. Sidiropoulos, C.K. Yang and M. Horowitz                                                                                                   | 43 |

| 4.6 | Low Power Chip Interconnection by Dynamic Termination                                                                                        |    |

|     | T. Kawahara, M. Horiguchi, J. Etoh, T. Sekiguchi and M. Aoki                                                                                 | 45 |

| 4.7 | An Active Substrate MCM System                                                                                                               | 47 |

| Ru  | mp Sessions                                                                                                                                  |    |

| R1  | Future High Performance Microprocessor Implementation Tradeoffs [Iolani I]I. Young and T. Sakurai                                            | 49 |

| R2  | Flash EEPROM: A Challenger to DRAM [lolani II]                                                                                               | 49 |

| R3  | Low Power/Low Voltage Technologies: A Joint Circuits &Technology Session [lolani IV]                                                         |    |

|     | W. Bidermann, Y. Nakagome and N. Lu                                                                                                          | 49 |

| R4  | Strategies for Digital Picture Compression and Coding [Honolulu I]T. Meng and H. Yamauchi                                                    | 50 |

| R5  | Data Converter Design Challenges at Very Low Power Supply Voltages [Honolulu II]                                                             |    |

|     | J. Khoury and T. Matsuzawa                                                                                                                   | 50 |

| Ses | ssion 5: Plenary Session II [Tapa II]                                                                                                        |    |

| 5.1 | Present and Future Directions for Multichip Module TechnologiesT. Sudo                                                                       | 51 |

| 5.2 | Future Directions in Microprocessor Technology                                                                                               | 55 |

| Ses | sion 6: Flash EEPROMs [Tapa II]                                                                                                              |    |

| §.1 | An 18Mb Serial Flash EEPROM for Solid-State Disk Applications                                                                                |    |

|     | D. Lee, H. Cernea, M. Motidi, S. Mehrotra, E. Chang, W. Chien, L. Goh, J. Yuan, A. Mihnea, G. Samachica                                      |    |

|     | Y. Fong, D. Guterman, R. Norman, K. Sato, H. Onishi, K. Ueda, F. Noro, K. Miyamoto, M. Morita, K. Umeda and K. Kubo                          | 59 |

| 6.2  | High-Speed Programming and Program-Verify Methods Suitable for Low-Voltage Flash Memories                                                                                             | 61 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 6.3  | An Over-Erasure Detection Technique for Tightening Vth Distribution for Low Voltage Operation NOR type Flash Memory                                                                   |    |

|      | Y. Miyawaki, T. Nakayama, M. Mihara, S. Kawai, M. Ohkawa, N. Ajika, M. Hatanaka, Y. Terada and T. Yoshihara                                                                           | 63 |

| 6.4  | A Quick Boosting Charge Pump Circuit for High Density and Low Voltage Flash Memories                                                                                                  | 65 |

| Ses  | sion 7: Digital System Chips [Tapa III]                                                                                                                                               |    |

| 7.1  | A 100MHz Embedded RISC MicrocontrollerS. Ozaki, Y. Nishimichi, T. Kakiage, H. Yamamoto, M. Sumita, G. Inoue, M. Urano, H. Yamashita, T. Maeda and T. Nishiyama                        | 67 |

| 7.2  | Cache-Processor Coupling: A Fast & Wide On-Chip Data Cache Design                                                                                                                     | 69 |

| 7.3  | A 110MHz MPEG2 Variable Length Decoder LSIE. Komoto and M. Seguchi                                                                                                                    | 71 |

| 7.4  | Asynchronous Transfer Mode Switching LSIs with 10Gbit/s Serial Inputs and Outputs                                                                                                     | 73 |

| Sess | sion 8: Dynamic Memory Concepts [Tapa II]                                                                                                                                             |    |

| 8.1  | A Staggered NAND DRAM Array Architecture for a Gbit Scale IntegrationS. Shiratake, D. Takashima, T. Hasegawa, H. Nakano, Y. Oowaki, S. Watanabe, K. Ohuchi and F. Masuoka             | 75 |

| 8.2  | An Automatic Temperature Compensation of Internal Sense Ground for Sub-Quarter Micron DRAMs                                                                                           | 77 |

| 8.3  | A 200MHz 16Mbit Synchronous DRAM with Block Access Mode                                                                                                                               | 79 |

| 8.4  | A 150-MHz 4-Bank 64M-bit SDRAM with Address Incrementing Pipeline SchemeY. Kodama, M. Yanagisawa, K. Shigenobu, T. Suzuki, H. Mochizuki and T. Ema                                    | 81 |

| 8.5  | Battery Operated 16M DRAM with Post Package Programmable and Variable Self RefreshD. Choi, Y. Kim, G. Cha, J. Lee, S. Lee, K. Kim, E. Haq, D. Jun, K. Lee, S. Cho, J. Park and H. Lim | 83 |

| 8.6  | A 256M DRAM with Simplified Register Control for Low Power Self Refresh and Rapid Burn-In                                                                                             |    |

|      | J. Han, E. Haq, S. Yoon, S. Jeong, B. Kim, J. Lee, T. Jang, H. Kim, C. Park, D. Seo, C. Choi, S. Cho and C. Hwang                                                                     | 85 |

| 8.7  | Automatic Voltage-Swing Reduction (AVR) Scheme for Ultra Low Power DRAMs                                                                                                              | 87 |

| 8.8  | An Experimental Cascade Cell Dynamic Memory                                                                                                                                           | 89 |

## Session 9: Signal Processing [Tapa III]

| 9.1  | • A Median Peak Detecting Servo Analog Processor for Hard Disk Drive                                                                                                                                  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9.2  | A 3.3V 36Mbps Single-Chip Data Channel Processor with Wide Programmable Range Filter for Disk Drives                                                                                                  |

| 9.3  | 2 to 12V, Single Supply, 40MHz, Video Operational Amplifier with Rail to Rail Input and Output Operation  A. Gusinov 95                                                                               |

| 9.4  | A 64-Site Multiplexed Low-Profile Neural Probe with n-Chip CMOS Circuitry                                                                                                                             |

| 9.5  | A 256-Element Associative Parallel Processor                                                                                                                                                          |

| 9.6  | A High Resolution Multibit Sigma-Delta Modulator with 9.6Individual Level AveragingF. Chen and B. Leung 101                                                                                           |

| 9.7  | An Oversampling ADC with Non-Linear Quantizer for PCM-CODECS. Sakiyama, S. Dosho, M. Maruyama, G. Hayashi, S. Inagaki, T. Moriiwa, M. Matsushita, K. Mochizuki and S. Ito 103                         |

| 9.8  | A Programmable Clock Generator Using Noise Shaping and Its Application in a Switched-Capacitor Filter P. Hurst and B. Rothenberg 105                                                                  |

| Sess | sion 10: SRAM [Tapa I]                                                                                                                                                                                |

| 10.1 | A 6-ns 4-Mb CMOS SRAM with Offset-Voltage-Insensitive Current Sense Amplifiers                                                                                                                        |

| 10.2 | A 0.65ns, 72kb ECL-CMOS RAM Macro for a 1Mb SRAMH. Nambu, K. Kanetani, Y. Idei, T. Masuda, K. Higeta, M. Ohayashi, M. Usami, K. Yamaguchi, T. Kikuchi, T. Ikeda, K. Ohhata, T. Kusunoki, N. Homma 109 |

| 10.3 | Circuit Techniques for an 8-ns ECL 100K Compatible 3.3V 16Mb BiCMOS SRAM with Minimum Operation Voltage of 2.3V                                                                                       |

| 10.4 | A Novel Synchronous Timing Control for 200MHz Mega-bits BiCMOS SRAM at 2.5V Operation                                                                                                                 |

| 10.5 | A Dynamic Current-Offset Calibration (DCC) Sense Amplifier with Fish-Bone Shaped Bitline (FBB) for High-<br>Density SRAMs                                                                             |

| 10.6 | A 2.6-ns Wave-Pipelined CMOS SRAM with Dual-Sensing-Latch                                                                                                                                             |

| 10.7 | The Source Sensed SRAM (S³) Cell                                                                                                                                                                      |

| 8.0  | Folded-Read and Open/Folded-Restore Bit-Line Scheme for Giga Scale 6F <sup>2</sup> DRAM Cell                                                                                                          |

χ

# Session 11: Communication Circuits [Tapa II]

| 11.1 | 3.0Gb/s, 272mW, 8:1 Multiplexer and 4.1Gb/s, 388mW, 1:8 Demultiplexer                                         |     |

|------|---------------------------------------------------------------------------------------------------------------|-----|

| 11.2 | A CMOS Serial Link for 1Gbaud Fully Duplexed Data Communication                                               |     |

|      | K. Lee, S. Kim, G. Ahn and D. Jeong                                                                           | 125 |

| 11.3 | A Fully Monolithic 1.25GHz CMOS Frequency Synthesizer                                                         | 127 |

| 11.4 | A 622MHz CMOS Phase-Locked Loop with Precharge-Type Phase Frequency Detector                                  |     |

|      | H. Notani, H. Kondoh and Y. Matsuda                                                                           | 129 |

| 11.5 | A 3GHz 25mW CMOS Phase-Locked LoopB. Razavi, K. F. Lee, R. Yan and R. Swartz                                  | 131 |

| 11.6 | A 900 MHz CMOS RF Power Amplifier with Programmable Output                                                    |     |

|      | M. Rofougaran, A. Rofougaran, C. Olgaard and A. Abidi                                                         | 133 |

| 11.7 | Completely Integrated 1.5GHz Direct Conversion Transceiver                                                    |     |

|      | P. Weger, W. Simbürger, H. Knapp, T. Leslie, N. Rohringer, J. Popp, G. Schultes, A. Scholtz and L. Treitinger | 135 |

# The IRIDIUM<sup>TM/SM1</sup> Personal Communication System

Mark Borota Communications Payload Manager

> Dr. Raymond J. Leopold Chief Engineer

Ken Johnson Advance Development Manager

> Dr. Ann Miller Chief Software Engineer

Motorola Commercial Space Business Unit 2501 South Price Road Chandler, Arizona 85248 USA

#### Abstract

Extensive use of VLSI technology allows the IRIDIUM Satellite System to be built at an affordable size and cost. The use of a new application specific integrated circuit (ASIC) methodology has improved development cycle times by a factor of two while simultaneously allowing the gate count per ASIC to increase by a factor of four.

#### Introduction

The goal of the IRIDIUM System is to make instant global communications a reality. At first thought, it would seem that we already have global communications. From the U.S., we can place calls to a vast number of domestic and international locations. However, there are many areas without telephone service, not only in emerging countries, but in developed nations as well. Consider that in Russia, with a population of 250 million, there are only 10 million telephones. In India, there are tens of thousands of villages without telephone service. There are some countries whose telephone system is so archaic that thunderstorms routinely disrupt service; some countries have service within their boundaries, yet lack the capability of international calling. Our mission of world-wide, world-class communications is decidedly a reach-out goal.

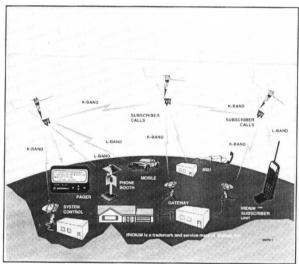

The system originally conceived utilized 77 satellites networked together orbiting the earth resembling the 77 electrons orbiting the nucleus in the atomic element iridium. In the years following the original system conception, several size, weight, performance and ctradeoffs have yielded the current design which uses 66 satellites. The satellites are networked together via crossostlinks, and with a system control facility, gateways, and subscriber

Figure 1 - IRIDIUM System Overview

units. The IRIDIUM System is overviewed in Figure 1.

We'll consider each element briefly and, no, we are not changing our name to dysprosium (the element with atomic number 66).

#### The Constellation

A network of orbiting satellites will be utilized to provide global coverage. We call this network a "constellation", analogous to natural constellations in space. The minimum number of satellites required for full-earth coverage depends on the altitude chosen. At higher altitudes fewer satellites are needed since they would be in "view" over a greater percentage of the earth. In fact, if the altitude were increased all the way to the geo-stationary level (35,786 Km), just three satellites would suffice. Unfortunately the

<sup>&</sup>lt;sup>1</sup>IRIDIUM is a registered trademark and service mark of Iridium, Inc.

Km), just three satellites would suffice. Unfortunately the complexity and size of each satellite increases as the required number of satellites decreases in order to maintain call capacity and link performance.

The satellite's antenna arrays get more complex at higher altitudes since the satellite must communicate directly with handheld telephone units having small, low gain antennas. Message-turnaround delays also increase with altitude which is undesirable. For geostationary satellites, the minimum delay would typically exceed 250ms., which is undesirable.

Conversely, lower altitudes require more, but simpler satellites. However, when considering lower and lower altitudes, a point is reached where the launch costs and logistics of more satellites becomes prohibitive. Also, the drag of the earth's atmosphere gets greater at lower altitudes which reduces orbital lifetime.

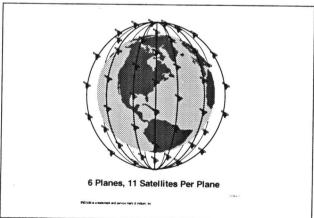

After considerable tradeoffs and optimizations, we have chosen an orbital altitude of nominally 780 kilometers, with 66 satellites configured in 6 polar orbital planes of 11 satellites each. The IRIDIUM Constellation is depicted in Figure 2.

The IRIDIUM System is being designed to use the principles of cellular telephony to provide reliable coverage from and to virtually any spot on earth. Three antennas on a satellite form a honeycomb pattern of 48 beams on the ground. As the satellites orbit the earth, the user would be handed-off from one beam to the next. Some handoffs would be intra-satellite, that is, within the 48-beam footprint of a single satellite. Once a user is within a boundary or edge beam of one satellite, the handoff will be inter-satellite. Instead of stationary cells and mobile users as in terrestrial cellular systems, the IRIDIUM System is designed to have relatively stationary users and mobile cells. Even the Concorde moves slowly compared to a

Figure 2 - The IRIDIUM Constellation

satellite which orbits the earth in 100 minutes.

The satellites in the six orbits will converge as they approach the poles, and their beams will overlap. Some of the outer beams will be "turned off" to eliminate the overlap and to conserve power.

The satellites are networked together via 23 GHz crosslinks to allow the relay of calls. Each satellite will have four crosslinks, allowing each to communicate with the satellite immediately ahead and behind in its own plane, as well as to the nearest satellites in each of the two adjacent corotating planes.

The satellites will be small, each weighing only 700 Kg. Current plans call for production line assembly of satellites (yes, this is a new paradigm in manufacturing!), with the complete network of 66 satellites on orbit and operational in 1998.

#### **System Control Facility**

Obviously, there has to be ground control over the satellites. This will be performed in the System Control Facility (SCF), which is to manage the constellation by tracking telemetry and attitude control information for each satellite to keep it in its appropriate envelope within its orbit and by monitoring the electrical/power and other support subsystems. Also, the facility will manage the communications network, informing satellites if a node is down so as to re-route calls. Two System Control Facilities, geographically separated, will be built to help assure continuous operation.

#### Gateways

An IRIDIUM Gateway, shown in the Systems Overview of Figure 1, is designed to interconnect the IRIDIUM Constellation with the Public Switched Telephone Network (PSTN). The Gateway is intended to handle call set-up, caller location, and collection of the necessary data to support billing. Caller location is necessary because, an IRIDIUM Subscriber who resides in Phoenix could carry and operate the unit in Singapore or Tel Aviv, or any other location with an operating license.

Gateways, through their incorporated switch and other interface electronics, are designed to interconnect the IRIDIUM Network to the world's PSTN. In this manner, calls could not only be placed between two IRIDIUM Subscribers, but also between an IRIDIUM Subscriber and a PSTN telephone.

In the current design, the Gateways would typically employ a minimum of three 3.3 meter tracking dish antennas that are separated by around 30 Km. At least two dishes are needed because as a satellite disappears over the horizon another will have appeared at a different location above the

horizon, and the handover from one to another is to be virtually instantaneous. Most Gateways are planned to have at least three tracking dishes to help ensure the availability of the communications link during maintenance activities.

The antenna separation would provide optional communication paths for avoidance of rain/thunderstorm cells during adverse weather conditions. It also would provide an option to avoid "looking" into the sun; a source of considerable radio noise. These options would reduce the amount of link margin (and peak transmitter power) required to maintain communication during these potentially detrimental conditions.

#### **Subscriber Units**

Subscriber units will be offered in a variety of shapes and sizes. Initial development includes the individual portable/handheld unit, the mobile unit which can be installed in an automobile or boat, the transportable unit that can be moved between remote fixed locations, and a variety of paging products. The current concept for an individual handheld unit is illustrated in Figure 3.

Motorola has plans to manufacture dual-mode, handheld subscriber units which will be compatible with both terrestrial cellular systems as well as the IRIDIUM System. Where the terrestrial system is available at home or as a roamer, the user could use the terrestrial cellular system. Where a terrestrial cellular system is not available, and an IRIDIUM Service is authorized, an IRIDIUM dial tone should be available.

The portable/handheld unit is currently designed to operate for 24 hours on a single recharge in a combination of standby (able to receive a "ring" indicating an incoming call) and active modes. The system is now being designed to be operated with subscriber unit transmit power levels comparable to those of handheld cellular telephones.

#### The Communications Network

The IRIDIUM System is often viewed as a space system (for obvious reasons), but, when you consider the functional objective, it isn't a space system. Fundamentally, the IRIDIUM System is a personal communications system that happens to have some of its infrastructure located in space. This subtle distinction is of paramount importance to our engineering team. The emphasis has always been on the personal communications device, the *handset*, which could be easily carried in a pocket, which will operate on rechargeable batteries, and which will operate in environments typical of today's cellular telephones. The inclusion of satellites in this system is not of much concern to those who will buy and use the handsets. They do not generally care whether there are telephone poles, undersea cables, microwave towers, or satellites involved in their

Figure 3 - The IRIDIUM Subscriber Unit

calls. They care about the voice quality, the availability of a dial tone, the cost, and the convenience of reliable service. The system is currently designed to support voice, transparent data, and compatible facsimile services.

The IRIDIUM System would employ communication links in two portions of the spectrum. The up/down links between the satellites and the subscriber units would operate within the 1610.0 - 1626.5 MHz region of L-Band. This band was allocated for satellite-based personal communications at the 1992 World Administrative Radio Conference (WARC) in Torremolinos, Spain.

The satellite crosslinks, as well as the up/down feeder links to the gateways, are designed for operation in the 20 - 30 GHz region of K-band. Licenses are required for operation in each Country; some are pending now.

#### ASIC Methodology

The satellite payload electronics extensively utilizes large gate count ASIC circuitry to achieve very high density packaging and low cost manufacturing. The entire spacecraft is manufactured using surface mount components and assembled on highly automated robotic manufacturing lines.

A new ASIC design methodology was developed that integrates several computer aided design (CAD) tools together that share common data bases and automatically convert from system level behavioral modeling to Very High -level Descriptive Language (VHDL). Our ASIC manufacturing foundry then converts the VHDL descriptions to gate level and device level implementations and automatically places and routes these complex circuits.

The current payload electronics design is comprised of almost 200 ASIC circuits made up of 14 different ASIC types and up to 200K gates per ASIC. See Table 1. The total design encompassed over 1.4 million gates of new logic designed in less than 12 months time. This represented a new benchmark within Motorola.

Table 1

ASIC Usage in the IRIDIUM Satellite

| Subsystem | ASIC<br>Types | ASICs per<br>Satellite | Total Gates |

|-----------|---------------|------------------------|-------------|

| L-Band    | 5             | 87                     | 560K        |

| K-Band    | 2             | 16                     | 160K        |

| Processor | 7             | 75                     | 720K        |

#### L-Band Links

Satellite L-Band phased arrays form the 48 spot beams to receive and transmit to the hand held telephone units. On board the satellite, hundreds of digital modems process the subscriber unit signals. Extensive use of ASIC circuitry and Digital Signal Processing (DSP) make the L-Band Link size and power achievable for the spacecraft.

The 48 beams provide Spatial Division Multiple Access (SDMA), which, when combined with Time Division Multiple Access (TDMA) and Frequency Division Multiple Access (FDMA), allow a great degree of dynamic reallocation of capacity by geographical location in response to demands for service. The combination of SDMA, TDMA & FDMA also result in very efficient spectral use.

#### K-Band Links

The intersatellite links network all the satellites together in a manner that allows many choices for the phone messages to be routed. On board the satellite, extensive use of Microwave Monolithic Integrated Circuits (MMIC) and digital modems built in ASICs are planned to allow the satellite to achieve its low power and small size.

#### **On-Board Processor**

The satellites are an active part of the message routing network, due to six on-board computers and extensive use of ASIC circuitry which connects the processors together with high speed memory, the modems and the antennas on the satellite.

#### Summary

The IRIDIUM Communications System is designed to be a global, digital, satellite-based, personal communications system primarily intended to provide low-density, portable service via handheld subscriber units, employing low-profile antennas. Calls can be made and received anywhere in the world with a personal, pocket-size, portable unit. A constellation of small, "smart" satellites will be internetted to form the network's backbone. Small, battery-powered, cellular-telephone-like user units would communicate directly with the satellites. Terrestrial Gateways interface the satellite network with the Public Switched Telephone Network. The system is intended to complement the terrestrial telephone network in densely populated areas by providing a similar service everywhere else in the world.

The IRIDIUM System is intended to be much more than a satellite system, much more than a radio, much more than a telephone system, much more than the technologies that allow it to be built. The IRIDIUM System is a vision -- a realizable vision -- for a worldwide portable, personal communications system -- a vision whose greatest realization, like the telephone of a century ago, extends beyond today's imagination. The rest of the story still remains to be written.

Subscribers to IRIDIUM Service will be widespread and varied. An international business person with a portable unit in a coat pocket could have easy access to the home office, and the head of a large multinational corporation could quickly call any colleagues, whether they are at home or traveling, on the earth's surface or in the air, anywhere in the world. The mountain climber, skier, or recreational sailor could continue to communicate with family, friends, or business associates. Developing countries without a telephone infra-structure could have subsidized, solar-powered, centrally-located telephone "booths" in every village. Land and sea mining operations could have continuous worldwide service. And, areas experiencing natural disasters could maintain a reliable communications linkage to the rest of the world.

# ATM in B-ISDN Communication Systems and VLSI Realization

#### Takeo Koinuma and Noriharu Miyaho

# NTT Communication Switching Laboratories 3-9-11 Midori-cho, Musashino-shi, Tokyo,180 Japan

#### **ABSTRACT**

Asynchronous Transfer Mode (ATM) is considered to be the key technology for realizing B-ISDN.

This paper discusses VLSI trends and the application of VLSIs to realize an ATM switching node system for B-ISDN.

The concept of VLSI realization as related to ATM switching under QOS control, virtual channel handling, usage parameter control, and OAM is addressed in addition to analyzing the required hardware amount.

Finally, VLSI requirements and the future ATM switching system image as suggested by expected VLSI developments are introduced.

#### 1. Introduction

Enhancing ISDN(Integrated Services Digital Networks) capability to achieve broadband capacity will significantly advance the telecommunication world. In recent years, broadband ISDN(B-ISDN) has been adopted as the vehicle with which to provide a wide variety of communication services.

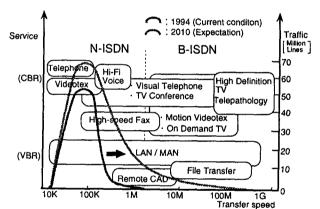

Asynchronous Transfer Mode (ATM) has been widely studied and is recognized as the key technology for implementing B-ISDN. Fig.1 shows possible network services, required transmission speeds, and expected transitions in B-ISDN demands towards the year 2010. The essential functional requirements for B-ISDN services are assumed to be the capability to handle

<1>multi-media traffic from voice to video,

<2>multi-rate traffic from low speed to ultra high speeds, and<3>multi-cast traffic.

ATM has been standardized by ITU-T (International Telecommunication Union - Telecommunication Standardization Sector, formerly CCITT) as the transfer mode for B-ISDN.

Most service specifications, including signaling for B-ISDN, will be finalized by the end of 1994 by ITU-T except the signaling for VBR connection, multi-point connection, bandwidth negotiation and so on.

As the first step in realizing B-ISDN, experimental ATM switching systems and corresponding transmission systems have been built and tested, and some key LSI components have already been developed(1)~(5).

In ATM networks, information such as voice, data, normal video, and super high definition video, is divided into fixed length (53 byte) data blocks, called cells, and these cells are non-periodically transmitted through the networks. This information transfer method realizes the very flexible allocation of transmission capacity.

Furthermore, it will integrate communication technologies and computer technologies so that true multi-media communication services will be achieved. Attractive communication services such as video on demand, tele-pathology, visual telephony and virtual reality can be realized by making full use of the ATM technology.

For implementing practical ATM systems, the requirements shown in Table 1 should be taken into consideration.

ATM systems for B-ISDN should handle various QOS parameters such as cell delay and loss ratio in a multi-media environment.

For example, real time applications such as visual telephony and TV conferencing have strict delay requirements and signals must be delivered within a specified period of time. Other applications such as remote medical examination and network computing have strict cell loss ratio requirements and must be delivered reliably.

Satisfying the above mentioned basic requirements with

Fig. 1 Broadband network services

Table 1. Basic requirements for the practical ATM system

|                                                                | The process Attal System                                   |                                                      |  |

|----------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------|--|

| ltem                                                           | Requirements                                               |                                                      |  |

|                                                                | Initial stage                                              | Mature stage                                         |  |

| (1) Transmission speed<br>(a) Subcriber line<br>(b) Trunk line | (a) ~150Mb/s<br>(b) ~150M/600Mb/s                          | (a) ~ 600Mb/s                                        |  |

| (2) Switching capacity                                         | ~ several tens<br>thousands<br>of 150 Mb/s lines           | ~several thousands of 150 Mb/s lines                 |  |

| (3) Switching performance<br>(a) Delay<br>(b) Cell loss rate   | (a) < 1 m sec<br>(b) < 10 <sup>-6</sup> ~10 <sup>-10</sup> | (a) < several hundred $\mu$ sec<br>(b) < $10^{-11}$  |  |

| (4) Virtual channels / line                                    | several thousands of vertual channels / line               | ~hundreds<br>thousands of virtual<br>channels / line |  |

| (5) Qos classes                                                | one                                                        | many                                                 |  |

| (6) Application                                                | · point to point<br>· CBR                                  | · point to point / multi cast · CBR / VBR            |  |