电子工程系列丛书(影印版)

# DIGITAL INTEGRATED CIRCUITS

A DESIGN PERSPECTIVE

# 数字集成电路

设计透视

JAN M. RABAEY

清华大学出版社 · PRENTICE HALL

# DIGITAL INTEGRATED CIRCUITS

JAN M. RABAEY

清华大学出版社

Prentice-Hall International, Inc.

## (京)新登字 158 号

Digital integrated circuits: a design perspective/Jan M. Rabaev

Copyright © 1996 by Prentice-Hall, Inc.

Original English Language Edition Published by Prentice-Hall Inc., Simon & Schuster/A Viacom Company.

All Rights Reserved.

For sale in Mainland China only.

· 本书影印版由 Prentice-Hall 出版公司授权清华大学出版社在中国境内 (不包括中国香港特别行政区、澳门地区和台湾地区)独家出版发行。

本经出版者书面许可,不得用任何方式复制或抄袭本书的任何部分。

本书封面贴有清华大学出版社激光防伪标签,无标签者不得销售。

北京市版权局著作权合同登记号: 01-98-2059

### 图书在版编目(CIP)数据

数字集成电路:设计透视:英文/拉贝(Rabaey, J. M.)著. - 影印版. - 北京: 清华大学出版社, 1998.9(电子工程系列丛书)

ISBN 7-302-03060-X

I.数… Ⅱ.拉… Ⅲ.数字集成电路-设计-英文 Ⅳ.TN431.2中国版本图书馆 CIP 数据核字(98)第 21435 号

出版者: 清华大学出版社(北京清华大学学研大厦,邮编 100084) http://www.tup.tsinghua.edu.cn

印刷者: 清华大学印刷厂

发行者: 新华书店总店北京发行所

开 本: 850×1168 1/32 印张: 22.625 彩插: 8面

版 次:1999年2月第1版 2000年8月第2次印刷

书 号: ISBN 7-302-03060-X/TN • 101

印 数:5001~7000

定 价:36.00元

## 出版前言

清华大学出版社与 Prentice Hall 出版公司合作推出的"大学计算机教育丛书(影印版)"和"ATM 与 B-ISDN 技术丛书(影印版)"受到了广大读者的欢迎。很多读者通过电话、信函、电子邮件对我们的工作以积极评价,并提出了不少极好的建议,令我们感动和鼓舞。我们除了继续努力完善上述两套丛书以外,还将努力拓宽影印图书的专业范围,以更好地满足读者的需要。

电子工程是信息科学的基础,高等学校新的教学要求指出,计算机专业和电子学专业的学生应相互学习渗透到彼此的专业领域,拓宽知识面,以适应信息技术飞速发展的时代。培养通晓相关专业领域知识的人才,成为面向新世纪的理工科教育的迫切要求。为此,我们挑选了与信息科学、电子学有关的国外优秀著作,组成电子工程系列丛书(影印版),奉献给国内读者。我们希望这套新的丛书能成为国内的大专院校师生和科研单位的工作人员提供新的知识和营养,也衷心期待着读者对我们一如既往的支持。

清华大学出版社 Prentice Hall 出版公司 1998.12

### **PREFACE**

### Why This Book?

Welcome to "Digital Integrated Circuits: A Design Perspective." When you get this book in your hands, your first question very well might be, "With the already abundant number of text and reference books in the digital circuit and VLSI arenas, what is the value of this entry?" The answer is that a review of the existing material in the realm of digital circuit design reveals a major instructional gap between the circuit and system visions on digital design. This book merges both and provides a bridge between the top-down and bottom-up design approaches.

While starting from a solid understanding of the operation of electronic devices and an in-depth analysis of the nucleus of digital design—the inverter—we will gradually channel this knowledge into the design of more complex modules such as gates, adders, multipliers, registers, controllers, and memories. While doing so, we will identify the compelling questions that face the designer of today's complex circuits: What are the dominant design parameters, what section of the design should he focus on and what details could she ignore. Simplification is clearly the only approach to address the increasing complexity of the digital systems. However, oversimplification can lead to circuit failure since global circuit effects such as timing, interconnect, and power consumption are ignored. To avoid this pitfall it is important to design digital circuits with both a circuits and a systems perspective in mind. This is exactly the approach taken in this book, which brings the reader the knowledge and expertise needed to deal with complexity, using both analytical and experimental techniques.

### Design from a System and a Circuit Perspective

The complexity of digital integrated circuits has grown dramatically over the past decades. Circuits with more than 1 million gates clocked at multiple 100 MHz combined with gigabit memories will emerge in the very near future. The sheer complexity of the design process has prompted the design community to respond with a dual solution: design automation and design abstraction. While the former helps the digital circuit designer in circuit generation, synthesis, analysis, and verification, the latter is the most important way

to deal with the complexity issue. A design can be envisioned as a hierarchical composition of modules rather than a chaotic collection of transistors. At each design level, the complex, internal details of each of the composing modules are abstracted away and replaced by a black box view, or model. Examples of modeling levels are the transistor, gate, arithmetic operator, datapath, processor, and system levels. The impact of this divide and conquer approach is dramatic. Instead of having to deal with a myriad of elements, the designer considers only a handful of components, each characterized in performance and cost by a small number of parameters.

This design methodology, combined with an ever-increasing level of automation, suggests that the breed of digital circuit designers is soon to become extinct. This impression is reflected in the VLSI design instructional approach that addresses design in a top-down fashion, hiding the complex behavior of semiconductor devices.

Nothing is less true. While the top-down approach might work for a large number of circuits, the abstraction model suffers from major pitfalls and works only to a certain degree. In a high-performance circuit, for instance, the connection of one module to another influences the performance of both. The interconnect wire and associated parasitics become dominant factors in the circuit performance. The increasing power dissipation of high performance design translates into reduced reliability and increased packaging cost. Ensuring that the circuit operates correctly under these high clock frequencies is another challenge that faces the designer of advanced digital circuits. To address any of these issues requires an in-depth understanding of the underlying electrical concepts and constructs. This textbook covers these crucial concepts in detail and provides insights into factors that have a profound impact on reliability and performance.

In the bottom-up design philosophy, advocated in traditional digital circuit text-books, the behavioral and performance model of a digital component is built starting from the transistor with all its peculiarities. While this approach results in an in-depth understanding of the component operation, it fails to translate this knowledge into a compact and simple model that can percolate upwards to help construct more complex modules. The prime talent of a good digital designer is to know when simplification is appropriate and when it is not. Acquiring this skill requires design experimentation and expertise. By taking a design-experimental approach, this book provides the student and professional the kind of hands-on experience that helps build that expertise.

It is my belief that bringing both circuit and systems views on design together results in a profound understanding of the design of complex digital circuits, while preparing the designer for new challenges that might be waiting around the corner. Only time will tell how successful this undertaking was.

### Other Features This Book Offers

It is worth summarizing some other unique features we deem essential to accomplish the aforementioned goal and that form the underpinning of this textbook.

Design-oriented perspectives are advocated throughout. Design challenges and guidelines are highlighted. Techniques introduced in the text are illustrated with real designs and complete SPICE analysis.

- It is the only current textbook that shows how to use the latest techniques to design complex high-performance, or low-power circuits.

- It covers crucial real-world system design issues such as signal integrity, power dissipation, interconnect, packaging, timing, and synchronization.

- It not only covers MOS but also addresses other high-performance technologies such as bipolar, BiCMOS, GaAs, and superconducting.

- It provides unique coverage of the latest design methodologies and tools, with a discussion of how to use them from a designers' perspective.

- It offers perspectives on how digital circuit technology might evolve in the future.

- The book features outstanding illustrations and a usable design-oriented four-color insert.

- An extensive instructional package is available over the internet from the author's

web site at U.C. Berkeley. It includes design software, transparency masters, design

problems, actual layouts, and hardware and software laboratories.

### How to Use This Book

The core of the text is intended for use in a senior-level digital circuit design class. Around this kernel, we have included chapters and sections covering the more advanced topics. In the course of developing this book, it became obvious quickly that it is hard to define a subset of the digital circuit design domain that covers everyone's needs. On the one hand, a newcomer to the field needs detailed coverage of the basic concepts. On the other hand, feedback from early readers and reviewers indicated that an in-depth and extensive coverage of advanced topics and current issues is desirable and necessary. Providing this complete vision resulted in a text that exceeds the scope of a single-semester class. The more advanced material can be used as the basis for a graduate class. The wide coverage and the inclusion of state-of-the-art topics also makes the text useful as a reference work for professional engineers.

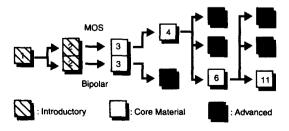

The organization of the material is such that the chapters can be taught or read in a great many ways, as long as a number of precedence relations are adhered to. An overview of these interdependencies is pictured in the chart below. The core of the text consists of Chapters 3, 4, 6, and 11. Chapters 1 and 2 can be considered as introductory. Students with a prior introduction to semiconductors can traverse quickly through Chapter 2. We urge

everyone to do at least that, as a number of important notations and foundations are introduced in that chapter. It is assumed that students taking this course are familiar with the basics of logic design.

Chapters 5, 7, 8, 9, and 10 are of a more advanced nature and can be used to provide a certain focus to the course. A course with a focus on the circuit aspects, for example, can supplement the core material with Chapters 5 and 10. A course focused on the digital system design should rather consider adding (parts of) Chapters 7, 8, and 9. All of these advanced chapters can be used to form the core of a graduate or a follow-on course. Other ordering options are possible. For instance, one might prefer to cover first the MOS parts of Chapters 2 and 3 before tackling the bipolar devices and gates. Sections considered advanced are marked with an asterisk in the text.

A number of possible paths through the material for a senior-level class are enumerated below. Many other variations are feasible. In the *instructor documentation*, provided with this book, we have included a number of complete syllabi similar to those used in school tests.

Basic circuit class (with minor prior device knowledge):

1, 2.1-3, 3.1-3, 4, 2.4-6, 3.4-5, 5.1-5.3, 6, 11.

Somewhat more advanced circuit coverage:

1, (2), 3.1-3, 4, 2.4-6, 3.4-5, 5.1-5.4, 6, 10, 11.

Course with systems focus:

1, (2.1-2.3), 3.1-3, 4, 6, 7, 8, 9, (10), 11.

We have chosen to separate layout-oriented discussions from the main text flow and to intersperse them through the text as *appendices*. Appendices A, C, and E cover design rules, cell layout, and datapath layout, respectively and are by preference covered in concurrence with the chapter they are attached to.

It was (and is) our intention to maintain a consistent flow through each of the chapters. The topics addressed in the chapter are introduced first, followed by a detailed and indepth discussion of the ideas. A Perspective section discusses how the introduced concepts relate to real world designs and how they might be impacted by future evolutions. Each chapter finishes with a Summary, which briefly enumerates the topics covered in the text, followed by To Probe Further and Reference sections. These provide ample references and pointers for a reader interested in further details on some of the material. Each chapter ends with exercises and design projects, which range from the simple to the challenging. Solutions to the problem sets are provided in the instructor's manual. A worldwide web companion provides fully worked-out design problems and a complete set of overhead transparencies, extracting the most important figures and graphs from the text. A laboratory book with worked-out hardware and software experiments is in the making.

### Problems, Exercises, and Design Projects

As the title of the book implies, one of the goals of this book is to stress the design aspect of digital circuits. To achieve this more practical viewpoint and to provide a real perspective, we have interspersed actual design examples and layouts throughout the text. These case studies help to answer questions, such as "How much area or speed or power is really saved by applying this technique?"

To mimic the real design process, we are making extensive use of design tools such as circuit- and switch-level simulation as well as layout editing and extraction. Computer analysis is used throughout to verify manual results, to illustrate new concepts, or to examine complex behavior beyond the reach of manual analysis.

Open-ended design problems, included at the end of most chapters, help to gain the all-important insight into design optimization and trade-off. The use of design editing, verification and analysis tools is recommended when attempting these design problems. Fully worked out versions of the problems can be found in the world-wide web page.

Finally, to facilitate the learning process, there are numerous examples included in the text. Each chapter contains a number of problems or brain-teasers (answers for which can be found in the back of the book), that provoke thinking and understanding while reading. Numerous challenging exercises (more than 200 of them) are included at the end of each chapter. Their goal is to provide the individual reader an independent gauge for his understanding of the material and to provide practice in the use of some of the design tools. Each problem is keyed to the text sections it refers to (e.g. <1.3>), the design tools that must be used when solving the problem (e.g., SPICE) and a rating, ranking the problems on difficulty: (E) easy; (M) moderate and (C) challenging. Problems marked with a (D) include a design or research elements.

### The Worldwide Web Page — A Dynamic Companion

With the advent of modern networking technology, a textbook does not have to be a static entity anymore, but can become a dynamically evolving document. For this reason, we have established a worldwide web page for the book that contains the latest updates, new problem sets and design projects as well as extensive instructor material. Downloadable postscript files are available for complete transparency sets, covering all the material. Even more, we have provided a library of downloadable software tools useful in the context of this book (SPICE, MAGIC, IRSIM). It is our hope that this home page will become a forum for digital circuit design. Instructor contributions in terms of new problem sets or design projects are greatly welcomed and can help to keep your course more attractive and interesting for the students. We already received extra slide sets, addressing more advanced topics even before going to press. Please have a look at the following address: http://infopad.eecs.berkeley.edu/-icdesign. Comments and feedback are appreciated.

### The Contents at a Glance

A quick scan of the table-of-contents shows how the ordering of chapters and the material covered are consistent with the advocated design methodology. Starting from a model of the semiconductor devices, we will gradually progress upwards, covering the inverter, the complex logic gate (NAND, EXOR, Flip-Flop), the functional (adder, multiplier, shifter, register) and the system module (datapath, controller, memory) levels of abstraction. For each of these layers, the dominant design parameters are identified and simplified models are constructed, abstracting away the nonessential details. While this layered modeling approach is the designer's best handle on complexity, it has some pitfalls. This is illustrated in Chapters 8 and 9, where topics with a global impact, such as interconnect parasitics and chip timing, are discussed. To further express the dichotomy between circuit and system design visions, we have divided the book contents into two parts: Part I (Chapters

2-6) addresses mostly the circuit perspective of digital circuit design, while Part II (Chapters 7-11) presents a more system oriented vision.

Chapter 1 serves as a global introduction. After a historical overview of digital circuit design, the concepts of hierarchical design and the different abstraction layers are introduced.

Chapter 2 contains a summary of the primary design building blocks, the semiconductor devices. The main goal of this chapter is to provide an intuitive understanding of the operation of the MOS and bipolar silicon transistors as well as to introduce the device models, which will be used extensively in the later chapters. Some of the artifacts of modern submicron devices are also discussed. Readers with prior device knowledge can traverse this material rather quickly.

Chapter 3 deals with the nucleus of digital design, the *inverter*. First, a number of fundamental properties of digital gates are introduced. These parameters, which help to quantify the performance and reliability of a gate, are derived in detail for two representative inverter structures: the static complementary CMOS and the bipolar ECL inverter. The techniques and approaches introduced in this chapter are of crucial importance, as they are repeated over and over again in the analysis of other gate structures and more complex gate structures.

This fundamental knowledge is extended in Chapter 4 to address the design of simple digital CMOS gates, such as NOR and NAND structures. It is demonstrated that, depending upon the dominant design constraint (reliability, area, performance, or power), other CMOS gate structures besides the complementary static gate can be attractive. The properties of a number of contemporary gate-logic families are analyzed and compared. Techniques to optimize the performance and power consumption of complex gates are introduced.

While CMOS gates are achieving ever higher speeds, other technologies are a necessity when even higher performance is required; for example, BiCMOS, GaAs, and superconducting technologies. While circuits, implemented in one of these processes, represent only a small portion of the total digital design market, an analysis of some representative gates for each technology is definitely worthwhile. Design automation is likely to turn the design of low- to medium-performance circuits into a chore rather than a challenge. The contributions of the digital designer will, rightly so, be focused on the implementation of the highest-performance components of the design. A large number of issues, currently raised in the design of high performance bipolar or GaAs circuits, might soon carry over to CMOS as well. Finally, the analysis of how the choice of a different device affects the nature and the performance of a gate structure is revealing and is instrumental in the building of a fundamental understanding of digital circuit design. High-speed gate design is the topic of Chapter 5 (which is optional for undergraduate courses).

All chapters prior to Chapter 6 deal exclusively with combinational circuits, that is circuits without a sense of the past history of the system. Sequential logic circuits, in contrast, can remember and store the past state. Chapter 6 discusses how this memory function can be accomplished using either positive feedback or charge storage. Besides analyzing the traditional bistable flip-flops, other sequential circuits such as the mono- and astable multivibrators are also introduced.

All previous chapters present a circuit-oriented approach towards digital design. The analysis and optimization process has been constrained to the individual gate. Starting

from Chapter 7, we take our approach one step further and analyze how gates can be connected together to form the building blocks of a system. The design of a variety of complex arithmetic building blocks such as adders, multipliers, and shifters, is discussed first. This chapter is crucial because it demonstrates how the design techniques introduced in chapters 3 and 4 are extended to the next abstraction layer. The concept of the critical path is introduced and used extensively in the performance analysis and optimization. Higher-level performance models are derived. These help the designer to get a fundamental insight into the operation and quality of a design module, without having to resort to an indep'h and detailed analysis of the underlying circuitry.

Chapter 8 discusses the impact of *interconnect wiring* on the functionality and performance of a digital gate. A wire introduces parasitic capacitive, resistive, and inductive effects, which are becoming ever more important with the scaling of the technology. Techniques to efficiently model these parasitic effects are presented. Approaches to minimize the impact of the interconnect parasitics on both performance and circuit reliability are introduced. The impact of packaging technology on circuit operation and performance is discussed.

In order to operate sequential circuits correctly, a strict ordering of the switching events has to be imposed. Without these timing constraints, wrong data might be written into the memory cells. Most digital circuits use a synchronous, clocked approach to impose this ordering. In Chapter 9, the different approaches to digital circuit timing and clocking are discussed. The impact of important effects such as clock skew on the behavior of digital synchronous circuits is analyzed. The synchronous approach is contrasted with alternative techniques, such as self-timed circuits. The chapter concludes with a short introduction to synchronization and clock-generation circuits.

Whenever large amounts of data storage are needed, the digital designer resorts to special circuit modules, called *memories*. Semiconductor memories achieve very high storage density by compromising on some of the fundamental properties of digital gates. Chapter 10 discusses in depth the different memory classes and their implementation. Instrumental in the design of reliable and fast memories is the implementation of the peripheral circuitry, such as the decoders, sense amplifiers, drivers, and control circuitry, which are extensively covered. Finally, as the primary issue in memory design is to ensure that the device works consistently under all operating circumstances, the chapter concludes with a detailed discussion of memory reliability. This chapter as well as the previous one are optional for undergraduate courses.

The book concludes with a discussion of design methodologies. Design automation is the only way to cope with the ever-increasing complexity of digital designs. In Chapter 11, the prominent ways of producing large designs in a limited time are discussed. The chapter presents the common design representation and analysis approaches as well as the different implementation methodologies. The chapter ends with a short discussion of manufacturing tests, an often overlooked component of the digital design process.

### Acknowledgments

The author would like to thank all those who contributed to the emergence, creation and correction of this manuscript. First of all, the graduate students of the University of California at Berkeley, who were an invaluable help in providing examples and improving the

early drafts: Paul Landman, David Lidsky, Anthony Stratakos, Andy Burstein, Anantha Chandrakasan, Renu Mehra, Lisa Guerra, Ole Bentz, Tom Burd, Alfred Yeung, Scarlett Wu, Arthur Abnous, and Steve Lo. Thanks also to the students of the EE141 and EE241 courses at Berkeley, who suffered through many of the experimental class offerings based on this book. I am grateful to the students of the E506 class at Waseda University, Tokyo who represented the first foreign exposure of this material. I also would like to acknowledge the help and advice of a substantial number of people, who helped to review and improve this text: Ingrid Verbauwhede (UCB), Andrew Neureuther (UCB), Kevin Kornegay (IBM and Purdue), Charlie Sodini (MIT), Doug Hoy (Tektronix), Randy Allmon (DEC), Greg Uehara (Univ. of Hawaii), Massoud Pedram (USC), A. Srivastava (Louisiana State Univ.), C. Mastrangelo (Univ. Of Michigan), S. Embabi (Texas A&M), D. Ioannou (George Mason Univ.), T. DeMassa (Arizona State), B. Biderman (DEC), T. Knight (MIT), M. Elmasry (Waterloo), and many others.

I am extremely grateful to the staff at Prentice Hall, who have been instrumental in turning a rough manuscript into an enjoyable book. First of all, I would like to acknowledge the help and constructive feedback of the publishing editor, Alan Apt. The editorial development help of Sondra Chavez was greatly appreciated. Nick Murray was the copy editor and Mona Pompili made it all come together as production editor. Shirley McGuire helped us assemble the instructor's manual.

A special word of thanks for the two persons who taught me more than anyone else about the world of electronics (and much beyond), namely Hugo De Man and Robert Brodersen.

I would like to highlight to role of computer aids in developing this manuscript. All drafts were completely developed on the FrameMaker publishing system (Frame Technology Corporation). Graphs were generated using the xvgr tool (thanks, Paul Turner), Mathematica, and Matlab. For circuit simulations, I used both SPICE 3 (U.C. Berkeley) and HSPICE (Meta-Software). All layouts were generated using the MAGIC layout editor and the LAGER silicon compiler (both from U.C. Berkeley). The IRSIM tool (from Stanford University) was used extensively for the switch-level verification of more complex designs and is also suggested for use in a number of design projects.

Finally, I would like to express my extreme gratitude to my wife and companion Kathelijn for enduring these "lost years" of our life. She has been a constant support, help and encouragement during the writing of this manuscript. Fortunately, we will get some more time for skiing or hiking as of now.

Jan M. Rabaey Berkeley, California

# CONTENTS

| Chapter 1 | l: Introduction                                       | 1  |

|-----------|-------------------------------------------------------|----|

| 1.1       | A Historical Perspective                              | 2  |

| 1.2       | Issues in Digital Integrated Circuit Design           | 4  |

| 1.3       | To Probe Further                                      | 12 |

| 1.4       | Exercises                                             | 15 |

|           | CUIT PERSPECTIVE                                      | 1. |

|           |                                                       |    |

| -         | 2: The Devices                                        | 17 |

| 2.1       | Introduction                                          | 18 |

| 2.2       | The Diode                                             | 18 |

|           | 2.2.1 A First Glance at the Device                    | 19 |

|           | 2.2.2 Static Behavior                                 | 22 |

|           | 2.2.3 Dynamic, or Transient, Behavior                 | 27 |

|           | 2.2.4 The Actual Diode—Secondary Effects              | 36 |

|           | 2.2.5 The SPICE Diode Model                           | 38 |

| 2.3       | The MOS(FET) Transistor                               | 39 |

|           | 2.3.1 A First Glance at the Device                    | 39 |

|           | 2.3.2 Static Behavior                                 | 41 |

|           | 2.3.3 Dynamic Behavior                                | 47 |

|           | 2.3.4 The Actual MOS Transistor—Secondary Effects     | 50 |

|           | 2.3.5 SPICE Models for the MOS Transistor             | 57 |

| 2.4       | The Bipolar Transistor                                | 62 |

|           | 2.4.1 A First Glance at the Device                    | 63 |

|           | 2.4.2 Static Behavior                                 | 64 |

|           | 2.4.3 Dynamic Behavior                                | 72 |

|           | 2.4.4 The Actual Bipolar Transistor—Secondary Effects | 79 |

|           | 2.4.5 SPICE Models for the Bipolar Transistor         | 81 |

| 2.5       | A Word on Process Variations                          | 84 |

| 2.6       | Perspective: Future Device Developments               | 04 |

xiv CONTENTS

| 2.7       | Summary                                                                   | 87         |

|-----------|---------------------------------------------------------------------------|------------|

| 2.8       | To Probe Further                                                          | 89         |

| 2.9       | Exercises and Design Problems                                             | 90         |

| Appendix  | A: Layout Design Rules                                                    | 97         |

| Appendix  | c B: Small-Signal Models                                                  | 105        |

| Chapter 3 | 3: The Inverter                                                           | 108        |

| 3.1       | Introduction                                                              | 109        |

| 3.2       | Definitions and Properties                                                | 109        |

|           | 3.2.1 Area and Complexity                                                 | 109        |

|           | 3.2.2 Functionality and Robustness: The Static Behavior                   | 110        |

|           | 3.2.3 Performance: The Dynamic Behavior                                   | 116        |

| 2.2       | 3.2.4 Power and Energy Consumption                                        | 119        |

| 3.3       | The Static CMOS Inverter 3.3.1 A First Glance                             | 120        |

|           | 3.3.2 Evaluating the Robustness of the CMOS Inverter: The Static Behavior | 120        |

|           | 3.3.3 Performance of CMOS Inverter: The Dynamic Behavior                  | 124<br>129 |

|           | 3.3.4 Power Consumption and Power-Delay Product                           | 141        |

|           | 3.3.5 A Look into the Future: Effects of Technology Scaling               | 146        |

| 3.4       | The Bipolar ECL Inverter                                                  | 150        |

|           | 3.4.1 Issues in Bipolar Digital Design: A Case Study                      | 150        |

|           | 3.4.2 The Emitter-Coupled Logic (ECL) Gate at a Glance                    | 155        |

|           | 3.4.3 Robustness and Noise Immunity: The Steady-State Characteristics     | 160        |

|           | 3.4.4 ECL Switching Speed: The Transient Behavior                         | 165        |

|           | 3.4.5 Power Consumption 3.4.6 Looking Ahead: Scaling the Technology       | 176        |

| 3.5       | Perspective: Area, Performance, and Dissipation                           | 177        |

| 3.6       | Summary                                                                   | 179        |

| 3.7       | To Probe Further                                                          | 179        |

| 3.8       | Exercises and Design Problems                                             | 180        |

|           |                                                                           | 181        |

|           | : Designing Combinational Logic Gates in CMOS                             | 189        |

| 4.1       | Introduction                                                              | 190        |

| 4.2       | Static CMOS Design                                                        | 191        |

|           | 4.2.1 Complementary CMOS 4.2.2 Ratioed Logic                              | 191        |

|           | 4.2.3 Pass-Transistor Logic                                               | 202        |

| 4.3       | Dynamic CMOS Design                                                       | 210        |

|           | 4.3.1 Dynamic Logic: Basic Principles                                     | 222<br>223 |

|           | 4.3.2 Performance of Dynamic Logic                                        | 225        |

|           | 4.3.3 Noise Considerations in Dynamic Design                              | 227        |

|           | 4.3.4 Cascading Dynamic Gates                                             | 231        |

| 4.4       | Power Consumption in CMOS Gates                                           | 234        |

|           | 4.4.1 Switching Activity of a Logic Gate                                  | 234        |

|           | 4.4.2 Glitching in Static CMOS Circuits                                   | 240        |

|           | 4.4.3 Short-Circuit Currents in Static CMOS Circuits                      | 242        |

|           | 4.4.4 Analyzing Power Consumption Using SPICE                             | 244        |

|          | /X |

|----------|----|

| CONTENTS | •  |

|                                                   | 4.4.5 Low-Power CMOS Design                            | 246  |

|---------------------------------------------------|--------------------------------------------------------|------|

| 4.5                                               | Perspective: How to Choose a Logic Style               | 252  |

|                                                   | Summary                                                | 253  |

|                                                   | To Probe Further                                       | 254  |

|                                                   | Exercises and Design Problems                          | 255  |

|                                                   | C: Layout Techniques for Complex Gates                 | 264  |

| • •                                               | : Very High Performance Digital Circuits               | 269  |

| •                                                 | Introduction                                           | 270  |

|                                                   | Bipolar Gate Design                                    | 270  |

| J.2                                               | 5.2.1 Logic Design in ECL                              | 270  |

|                                                   | 5.2.2 Differential ECL                                 | 272  |

|                                                   | 5.2.3 Current Mode Logic                               | 278  |

|                                                   | 5:2.4 ECL with Active Pull-Downs                       | 281  |

|                                                   | 5.2.5 Alternative Bipolar Logic Styles                 | 283  |

| 5.3                                               | The BiCMOS Approach                                    | 287  |

|                                                   | 5.3.1 The BiCMOS Gate at a Glance                      | 288  |

|                                                   | 5.3.2 The Static Behavior and Robustness Issues        | 291  |

|                                                   | 5.3.3 Performance of the BiCMOS Inverter               | 293  |

|                                                   | 5.3.4 Power Consumption                                | 297  |

|                                                   | 5.3.5 Technology Scaling                               | 298  |

|                                                   | 5.3.6 Designing BiCMOS Digital Gates                   | 299  |

| 5.4                                               | Digital Gallium Arsenide Design *                      | 300  |

|                                                   | 5.4.1 GaAs Devices and Their Properties                | 301  |

|                                                   | 5.4.2 GaAs Digital Circuit Design                      | 307  |

| 5.5                                               | Low-Temperature Digital Circuits *                     | 312  |

|                                                   | 5.5.1 Low-Temperature Silicon Digital Circuits         | 312  |

|                                                   | 5.5.2 Superconducting Logic Circuits                   | 314  |

| 5.6                                               | Perspective: When to Use High-Performance Technologies | 321  |

| 5.7                                               | Summary                                                | -322 |

| 5.8                                               | To Probe Further                                       | 323  |

| 5.9                                               | Exercises and Design Problems                          | 325  |

| Appendix                                          | D: The Schottky-Barrier Diode                          | 330  |

| Chapter 6: Designing Sequential Logic Circuits 33 |                                                        | 332  |

| 6.1                                               | Introduction                                           | 333  |

| 6.2                                               | Static Sequential Circuits                             | 333  |

|                                                   | 6.2.1 Bistability                                      | 333  |

|                                                   | 6.2.2 Flip-Flop Classification                         | 335  |

|                                                   | 6.2.3 Master-Slave and Edge-Triggered FFs              | 338  |

|                                                   | 6.2.4 CMOS Static Flip-Flops                           | 341  |

|                                                   | 6.2.5 Bipolar Static Flip-Flops                        | 345  |

| 6.3                                               | Dynamic Sequential Circuits                            | 347  |

|                                                   | 6.3.1 The Pseudostatic Latch                           | 348  |

|                                                   | 6.3.2 The Dynamic Two-Phase Flip-Flop                  | 350  |

|                                                   | 6.3.3 The C2MOS Latch                                  | 351  |

| xvi | CONTENTS |

|-----|----------|

|     |          |

|               | 6.3.4 NORA-CMOS—A Logic Style for Pipelined Structures                                                    | 355        |

|---------------|-----------------------------------------------------------------------------------------------------------|------------|

| _             | 6.3.5 True Single-Phase Clocked Logic (TSPCL)                                                             | 359        |

| 6.4           | Non-Bistable Sequential Circuits                                                                          | 362        |

|               | 6.4.1 The Schmitt Trigger 6.4.2 Monostable Sequential Circuits                                            | 363        |

|               | 6.4.3 Astable Circuits                                                                                    | 369<br>371 |

| 6.5           | Perspective: Choosing a Clocking Strategy                                                                 | 374        |

|               | Summary                                                                                                   | 374<br>375 |

|               | To Probe Further                                                                                          |            |

|               |                                                                                                           | 375        |

|               | Exercises and Design Problems                                                                             | 376        |

| PART II: A SY | STEMS PERSPECTIVE                                                                                         |            |

| Chapter :     | 7: Designing Arithmetic Building Blocks                                                                   | 383        |

| 7.1           | Introduction                                                                                              | 384        |

| 7.2           | Datapaths in Digital Processor Architectures                                                              | 384        |

| 7.3           | The Adder                                                                                                 | 386        |

|               | 7.3.1 The Binary Adder: Definitions                                                                       | 386        |

|               | 7.3.2 The Full Adder: Circuit Design Considerations                                                       | 389        |

|               | 7.3.3 The Binary Adder: Logic Design Considerations                                                       | 396        |

| 7.4           | The Multiplier                                                                                            | 408        |

| •             | 7.4.1 The Multiplier: Definitions                                                                         | 408        |

|               | 7.4.2 The Array Multiplier                                                                                | 408        |

| 7.5           | 7.4.3 Other Multiplier Structures The Shifter                                                             | 412        |

| 1.3           | 7.5.1 Barrel Shifter                                                                                      | 414        |

|               | 7.5.2 Logarithmic Shifter                                                                                 | 414        |

| 76            | Other Arithmetic Operators                                                                                | 416        |

|               | Power Considerations in Datapath Structures                                                               | 417        |

| /./           | 7.7.1 Reducing the Supply Voltage                                                                         | 418        |

|               | 7.7.2 Reducing the Effective Capacitance                                                                  | 418        |

| 7.8           | Perspective: Design as a Trade-off                                                                        | 421        |

|               | Summary                                                                                                   | 424        |

|               | To Probe Further                                                                                          | 425        |

|               | Exercises and Design Problems                                                                             | 426        |

|               |                                                                                                           | 427        |

|               | E: From Datapath Schematics to Layout                                                                     | 434        |

|               | : Coping with Interconnect                                                                                | 438        |

|               | Introduction                                                                                              | 439        |

| 8.2           |                                                                                                           | 439        |

|               | 8.2.1 Modeling Interconnect Capacitance                                                                   | 439        |

|               | 8.2.2 Capacitance and Reliability—Cross Talk                                                              | 445        |

|               | 8.2.3 Capacitance and Performance in CMOS                                                                 | 446        |

| Q 2           | 8.2.4 Capacitance and Performance in Bipolar Design Resistive Parasitics                                  | 461        |

| 6.3           |                                                                                                           | 464        |

|               | 8.3.1 Modeling and Scaling of Interconnect Resistance 8.3.2 Resistance and Reliability—Ohmic Voltage Drop | 464        |

|               | and renavinty—Online voltage DTOD                                                                         | 467        |

| CONTENTS    |                                                                                                          | xvi        |

|-------------|----------------------------------------------------------------------------------------------------------|------------|

|             | 8.3.3 Electromigration                                                                                   | 469        |

|             | 8.3.4 Resistance and Performance—RC Delay                                                                | 471        |

| 8.4         | Inductive Parasitics                                                                                     | 477        |

|             | 8.4.1 Sources of Parasitic Inductances                                                                   | 477        |

|             | 8.4.2 Inductance and Reliability—Voltage Drop 8.4.3 Inductance and Performance—Transmission Line Effects | 478<br>482 |

| 0.6         |                                                                                                          | 493        |

| 8.3         | Comments on Packaging Technology<br>8.5.1 Package Materials                                              | 493        |

|             | 8.5.2 Interconnect Levels                                                                                | 494        |

|             | 8.5.3 Thermal Considerations in Packaging                                                                | 499        |

| 8.6         | Perspective: When to Consider Interconnect Parasitics                                                    | 500        |

| 8.7         | Chapter Summary                                                                                          | 501        |

| 8.8         | To Probe Further                                                                                         | 502        |

| 8.9         | Exercises and Design Problems                                                                            | 503        |

| Chapter 9   | 9: Timing Issues in Digital Circuits                                                                     | 510        |

| -           | Introduction                                                                                             | 511        |

|             | Clock Skew and Sequential Circuit Performance                                                            | 511        |

| 7. <b>2</b> | 9.2.1 Single-Phase Edge-Triggered Clocking                                                               | 513        |

|             | 9.2.2 Two-Phase Master-Slave Clocking                                                                    | 515        |

|             | 9.2.3 Other Clocking Styles                                                                              | 517        |

|             | 9.2.4 How to Counter Clock Skew Problems                                                                 | 517        |

|             | 9.2.5 Case Study—The Digital Alpha 21164 Microprocessor                                                  | 520        |

| 9.3         | Self-Timed Circuit Design*                                                                               | 522        |

|             | 9.3.1 Self-Timed Concept                                                                                 | 522        |

|             | 9.3.2 Completion-Signal Generation 9.3.3 Self-Timed Signaling                                            | 525<br>528 |

| 9.4         | Synchronizers and Arbiters*                                                                              | 533        |

| 2.4         | 9.4.1 Synchronizers—Concept and Implementation                                                           | 533        |

|             | 9.4.2 Arbiters                                                                                           | 538        |

| 9.5         | Clock Generation and Synchronization*                                                                    | 538        |

|             | 9.5.1 Clock Generators                                                                                   | 538        |

|             | 9.5.2 Synchronization at the System Level                                                                | 540        |

| 9.6         | Perspective: Synchronous versus Asynchronous Design                                                      | 543        |

| 9.7         | Summary                                                                                                  | 544        |

| 9.8         | To Probe Further                                                                                         | 544        |

| 9.9         | Exercises and Design Problems                                                                            | 545        |

| Chapter 1   | 0: Designing Memory and Array Structures                                                                 | 551        |

| 10.1        | Introduction                                                                                             | 552        |

| 10.2        | Semiconductor Memories—An Introduction                                                                   | 552        |

|             | 10.2.1 Memory Classification                                                                             | 552        |

|             | 10.2.2 Memory Architectures and Building Blocks                                                          | 555        |

| 10.3        | The Memory Core                                                                                          | 559        |

|             | 10.3.1 Read-Only Memories                                                                                | 559        |

|             | 10.3.2 Nonvolatile Read-Write Memories 10.3.3 Read-Write Memories (RAM)                                  | 573        |

|             | 10.3.3 Reau-write Memories (KAM)                                                                         | 578        |