# DESIGNING EFFICIENT ALGORITHMS FOR PARALLEL COMPUTERS

Michael J. Quinn

## DESIGNING EFFICIENT ALGORITHMS FOR PARALLEL COMPUTERS

Michael J. Quinn University of New Hampshire

## McGraw-Hill Book Company

New York St. Louis San Francisco Auckland Bogotá Hamburg Johannesburg London Madrid Mexico Milan Montreal New Delhi Panama Paris São Paulo Singapore Sydney Tokyo Toronto This book was set in Times Roman by Aldine Press.

The editors were Kaye Pace and Larry Goldberg;

the cover was designed by Albert Cetta;

the cover photograph was taken by A. Diakopoulos/Stock, Boston;

the production supervisor was Diane Renda. The drawings were done by ANCO/Boston.

R. R. Donnelley & Sons Company was printer and binder.

#### Flaure Credits

Figures 2-1 and 4-18: Aho, Hopcroft, and Ullman, The Design and Analysis of Computer Algorithms, ©1974, Addison-Wesley, Reading, Massachusetts, page 5, Figure 1.3, and page 264, Figure 7.5. Reprinted with permission.

Figures 2-6 and 2-8: Reprinted from Computational Aspects of VLSI by Jeffrey D. Ullman, ©1984, with the permission of the publisher, Computer Science Press, Inc., 1803 Research Blvd., Rockville, MD 20850 USA.

Figures 2-11, 2-12, 2-13, and 2-14: Reprinted from Parallel Computers by R. W. Hockney and C. R. Jesshope, ©1981, with the permission of the publisher, Adam Hilger, Bristol, England.

Figure 4-9: Robert Sedgewick, Algorithms, ©1983, Addison-Wesley, Reading, Massachusetts, page 465 (figure). Reprinted with permission.

Figure 4-12: Donald E. Knuth, The Art of Computer Programming, Volume 3, Sorting and Searching, ©1973, Addison-Wesley, Reading, Massachusetts, page 237, Figure 56. Reprinted with permission.

## DESIGNING EFFICIENT ALGORITHMS FOR PARALLEL COMPUTERS

Copyright © 1987 by McGraw-Hill, Inc All rights reserved. Printed in the United States of America. Except as permitted under the United States Copyright Act of 1976, no part of this publication may be reproduced or distributed in any form or by any means, or stored in a data base or retrieval system, without the prior written permission of the publisher.

1,2 3 4 5 6 7 8 9 0 DOCDOC 8 9 4 3 2 1 0 9 8 7

## ISBN 0-07-051071-7

#### Library of Congress Cataloging-in-Publication Data

Quinn, Michael J. (Michael Jay)

Designing efficient algorithms for parallel computers.

(Supercomputing & artificial intelligence)

Bibliography; p.

Includes index.

1. Parallel processing (Electronic computers)

2. Algorithms. I. Title. II. Series.

QA76.5.Q56 1987 004'.35 86-27230

ISBN 0-07-051071-7

A few years ago parallel computers could be found only in research laboratories. Now they are available commercially. For this reason we are entering an exciting period, when work on parallel algorithms can progress beyond design and analysis into implementation and use. This book has two primary goals: to familiarize the reader with classical results and to provide practical insights into how algorithms are made to run efficiently on processor arrays, multiprocessors, and multicomputers.

Chapter 1 puts parallel computing in perspective, showing the need for higher-performance computers and summarizing methods used in the past to increase computer performance. Chapter 2 begins with a presentation of a number of fundamental processor organizations and continues with a description of three parallel computer architectures: the processor array, the multiprocessor, and the multicomputer. Chapter 3 addresses many of the efficiency issues confronting the designer of parallel algorithms.

The chapters after Chapter 3 are more specialized. Chapter 4 presents some important results in parallel sorting from the large body of work done in this area. Chapter 5 discusses dictionary operations and illuminates trade-offs between the complexity of the underlying sequential algorithm and the potential for keeping a large number of processors busy doing useful work. Matrix multiplication is a fundamental component of many numerical and nonnumerical algorithms. Results in parallel matrix multiplication appear in Chapter 6. Chapter 7 describes parallel numerical algorithms to solve recurrence relations, partial differential equations, and systems of linear equations. Chapter 8 surveys parallel algorithms for searching graphs and finding connected components, minimum spanning trees, and shortest paths in graphs.

The final three chapters address current trends and past successes. Areas in which parallel computing may have a significant impact in the future include artificial intelligence and logic programming. Chapter 9 describes potential parallelism in the solution of combinatorial search problems. These problems occur in artificial intelligence, operations research, and graph theory, among other areas. Chapter 10 introduces Prolog, a logic programming language, and summarizes approaches to executing logic

programs in parallel. Pipelined vector processors have been of great historical importance; two well-known machines, the Cray-1 and Cyber-205, are surveyed in Chapter 11.

The principal audience for this text is intended to be seniors and graduate students in computer science. Suggested prerequisites are calculus, high-level language programming, data structures, operating systems, computer architecture, and the analysis of algorithms.

The book includes many parallel algorithms written in a machine-independent, high-level pseudocode. Experimental results from implementations of parallel algorithms have been included wherever possible. Important results have been presented as theorems, to make them easier to reference. Each chapter ends with a set of exercises. They range from the elementary to the difficult. A Glossary of parallel computing appears after Chapter 11. References are given throughout the text, and a large bibliography appears at the end of the book. A solutions manual is available to instructors only.

I have taught a one-semester graduate-level course in parallel computing at the University of New Hampshire, using earlier drafts of this book. I recommend that you supplement the exercises with actual programming assignments on a parallel computer or a simulator. Programming a parallel computer is a new, difficult, and exciting experience for most students, and they learn a great deal from their efforts. In addition, graduate students should read recent journal articles and conference papers. With these supplements, there is more than enough material for a one-semester course, giving the instructor some latitude. I have usually taken an "historical" approach, covering Chapters 1, 11, 2, and 3 before the midterm examination and Chapters 4, 5, 6, 8, 9, and 10 in less depth after the midterm.

Kai Hwang, B. Jayaraman, and Vipin Kumar provided many helpful suggestions that led to a substantial improvement in the quality of the text between the first and second drafts. Kaye Pace, my editor at McGraw-Hill, always made me feel as if I were her only responsibility. Let me extend my thanks to everyone involved in the production of the book.

I feel fortunate to have had as my dissertation advisor Narsingh Deo, who introduced me to the area of parallel algorithms. I am grateful to Donald Knuth and numerous unknown support people, who made the TeX typesetting system public, and to L. Michael Gray, who installed and maintained the TeX environment at the University of New Hampshire. I had felt for some time that there was a book in me, waiting to get out. Seeing my words transformed into beautifully typeset output was all the catalyst I needed.

Finally, I would like to thank my teachers throughout the years who provided me with such an inspiring example.

Michael J: Quinn

## CONTENTS

|         |     | Preface                                            |   | xv          |

|---------|-----|----------------------------------------------------|---|-------------|

| Chapter | 1   | Introduction                                       |   | i           |

|         | 1-1 |                                                    |   | 2           |

|         |     | Weather Prediction                                 |   | 2           |

|         |     | Computational Aerodynamics                         |   | 3<br>3<br>3 |

|         |     | Artificial Intelligence                            |   | 3           |

|         |     | Remote Sensing                                     |   | 3           |

|         |     | Nuclear Reactor Safety                             |   | 4           |

|         |     | Military Uses                                      | ş | . 4         |

|         | 1-2 | Methods Used to Achieve Higher Performance         |   | 4           |

|         |     | Bit-Parallel Memory and Bit-Parallel Arithmetic    |   | 5           |

|         |     | I/O Processors (Channels)                          |   | 5           |

|         | ,   | Interleaved Memory                                 |   |             |

|         |     | Cache Memory                                       |   | 6<br>7      |

|         |     | Instruction Look-Ahead                             |   | 8           |

|         |     | Multiple Functional Units                          |   | 8           |

| 136     |     | Instruction Pipelining                             |   | . 9         |

| , *'    |     | Pipelined Functional Units                         |   | 10          |

|         |     | Data Pipelining                                    |   | 10          |

|         |     | Processor Arrays                                   |   | 10          |

|         |     | Multiprogramming, Timesharing, and Multiprocessing |   | - 11        |

|         |     | Data Flow Computers                                |   | 11          |

|         |     | Computer Generations                               |   | 12          |

|         |     | Differences between Pipelining and Parallelism     |   | 13          |

|         | 1-3 |                                                    |   | 15          |

|         |     | Flynn's Taxonomy                                   |   | 16          |

|         |     | Händler's Classification                           |   | 17          |

|         | 1-4 |                                                    |   | 18          |

|         | 1-5 |                                                    |   | 20          |

|         | 1-3 | Bibliographic Notes                                |   | 20          |

|         |     | Exercises                                          |   | 20          |

|         |     | LACICIOCO                                          |   | 21          |

#### X CONTENTS

| 2-1 A Model of Serial Computation 2-2 Processor Organizations Mesh Pyramid Shuffle-Exchange Network Butterfly Hypercube (Cube-Connected) Cube-Connected Cycles 2-3 Processor Arrays Shared-Memory SIMD Model Mesh-Connected SIMD Model Other SIMD Models Associative Processors 2-4 Multiprocessors and Multicomputers Tightly Coupled Multiprocessors Loosely Coupled Multiprocessors Multicomputers 2-5 Parallel Computing Terminology Can Speedup Be Greater than Linear? 2-6 Amdahl's Law Revisited 2-7 Summary Bibliographic Notes Exercises  Chapter 3 Designing Parallel Algorithms 3-1 Generalities Insight Has an Important Role Communication Costs Must Be Considered The Algorithm Must Fit the Architecture 3-2 Developing Algorithms for Processor Arrays 3-3 Developing Algorithms for MIMD Computers Categorization of MIMD Algorithms Factors That Limit Speedup 3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages 3-5 Deadlock 3-6 Task Scheduling on MIMD Computers Deterministic Models | 23        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Mesh Pyramid Shuffle-Exchange Network Butterfly Hypercube (Cube-Connected) Cube-Connected Cycles 2-3 Processor Arrays Shared-Memory SIMD Model Mesh-Connected SIMD Model Other SIMD Models Associative Processors 2-4 Multiprocessors and Multicomputers Tightly Coupled Multiprocessors Loosely Coupled Multiprocessors Multicomputers 2-5 Parallel Computing Terminology Can Speedup Be Greater than Linear? 2-6 Amdahl's Law Revisited 2-7 Summary Bibliographic Notes Exercises  Chapter 3 Designing Parallel Algorithms 3-1 Generalities Insight Has an Important Role Communication Costs Must Be Considered The Algorithm Must Fit the Architecture 3-2 Developing Algorithms for Processor Arrays 3-3 Developing Algorithms for MIMD Computers Categorization of MIMD Algorithms Factors That Limit Speedup 3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization to Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages 3-5 Deadlock 3-6 Task Scheduling on MIMD Computers Deterministic Models                                                            | 23        |

| Pyramid Shuffle-Exchange Network Butterfly Hypercube (Cube-Connected) Cube-Connected Cycles  2-3 Processor Arrays Shared-Memory SIMD Model Mesh-Connected SIMD Model Other SIMD Models Associative Processors  2-4 Multiprocessors and Multicomputers Tightly Coupled Multiprocessors Loosely Coupled Multiprocessors Multicomputers  2-5 Parallel Computing Terminology Can Speedup Be Greater than Linear?  2-6 Amdahl's Law Revisited  2-7 Summary Bibliographic Notes Exercises  Chapter 3 Designing Parallel Algorithms  3-1 Generalities Insight Has an Important Role Communication Costs Must Be Considered The Algorithm Must Fit the Architecture  3-2 Developing Algorithms for Processor Arrays 3-3 Developing Algorithms for MIMD Computers Categorization of MIMD Algorithms Factors That Limit Speedup  3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock 3-6 Task Scheduling on MIMD Computers Deterministic Models                                                           | . 25      |

| Shuffle-Exchange Network Butterfly Hypercube (Cube-Connected) Cube-Connected Cycles  2-3 Processor Arrays Shared-Memory SIMD Model Mesh-Connected SIMD Model Other SIMD Models Associative Processors  2-4 Multiprocessors and Multicomputers Tightly Coupled Multiprocessors Loosely Coupled Multiprocessors Multicomputers  2-5 Parallel Computing Terminology Can Speedup Be Greater than Linear?  2-6 Amdahl's Law Revisited  2-7 Summary Bibliographic Notes Exercises  Chapter 3 Designing Parallel Algorithms  3-1 Generalities Insight Has an Important Role Communication Costs Must Be Considered The Algorithm Must Fit the Architecture  3-2 Developing Algorithms for Processor Arrays 3-3 Developing Algorithms for MIMD Computers Categorization of MIMD Algorithms Factors That Limit Speedup  3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock 3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                   | 25        |

| Butterfly Hypercube (Cube-Connected) Cube-Connected Cycles  2-3 Processor Arrays Shared-Memory SIMD Model Mesh-Connected SIMD Model Other SIMD Models Associative Processors  2-4 Multiprocessors and Multicomputers Tightly Coupled Multiprocessors Loosely Coupled Multiprocessors Multicomputers  2-5 Parallel Computing Terminology Can Speedup Be Greater than Linear?  2-6 Amdahl's Law Revisited  2-7 Summary Bibliographic Notes Exercises  Chapter 3 Designing Parallel Algorithms  3-1 Generalities Insight Has an Important Role Communication Costs Must Be Considered The Algorithm Must Fit the Architecture  3-2 Developing Algorithms for MIMD Computers Categorization of MIMD Algorithms Factors That Limit Speedup  3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock 3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                           | 25        |

| Hypercube (Cube-Connected) Cube-Connected Cycles  2-3 Processor Arrays Shared-Memory SIMD Model Mesh-Connected SIMD Model Other SIMD Models Associative Processors  2-4 Multiprocessors and Multicomputers Tightly Coupled Multiprocessors Loosely Coupled Multiprocessors Multicomputers 2-5 Parallel Computing Terminology Can Speedup Be Greater than Linear? 2-6 Amdahl's Law Revisited 2-7 Summary Bibliographic Notes Exercises  Chapter 3 Designing Parallel Algorithms  3-1 Generalities Insight Has an Important Role Communication Costs Must Be Considered The Algorithm Must Fit the Architecture 3-2 Developing Algorithms for Processor Arrays 3-3 Developing Algorithms for Processor Arrays 3-3 Developing Algorithms for MIMD Computers Categorization of MIMD Algorithms Factors That Limit Speedup 3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages 3-5 Deadlock 3-6 Task Scheduling on MIMD Computers Deterministic Models                                                             | 26<br>28  |

| Cube-Connected Cycles  2-3 Processor Arrays Shared-Memory SIMD Model Mesh-Connected SIMD Model Other SIMD Models Associative Processors  2-4 Multiprocessors and Multicomputers Tightly Coupled Multiprocessors Loosely Coupled Multiprocessors Multicomputers  2-5 Parallel Computing Terminology Can Speedup Be Greater than Linear?  2-6 Amdahl's Law Revisited  2-7 Summary Bibliographic Notes Exercises  Chapter 3 Designing Parallel Algorithms  3-1 Generalities Insight Has an Important Role Communication Costs Must Be Considered The Algorithm Must Fit the Architecture  3-2 Developing Algorithms for MIMD Computers Categorization of MIMD Algorithms Factors That Limit Speedup  3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock 3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                | 28        |

| 2-3 Processor Arrays Shared-Memory SIMD Model Mesh-Connected SIMD Model Other SIMD Models Associative Processors  2-4 Multiprocessors and Multicomputers Tightly Coupled Multiprocessors Loosely Coupled Multiprocessors Multicomputers  2-5 Parallel Computing Terminology Can Speedup Be Greater than Linear?  2-6 Amdahl's Law Revisited 2-7 Summary Bibliographic Notes Exercises  Chapter 3 Designing Parallel Algorithms  3-1 Generalities Insight Has an Important Role Communication Costs Must Be Considered The Algorithm Must Fit the Architecture  3-2 Developing Algorithms for MIMD Computers Categorization of MIMD Algorithms Factors That Limit Speedup  3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock 3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                        | 29        |

| Shared-Memory SIMD Model Mesh-Connected SIMD Model Other SIMD Models Associative Processors  2-4 Multiprocessors and Multicomputers Tightly Coupled Multiprocessors Loosely Coupled Multiprocessors Multicomputers  2-5 Parallel Computing Terminology Can Speedup Be Greater than Linear?  2-6 Amdahl's Law Revisited  2-7 Summary Bibliographic Notes Exercises  Chapter 3 Designing Parallel Algorithms  3-1 Generalities Insight Has an Important Role Communication Costs Must Be Considered The Algorithm Must Fit the Architecture  3-2 Developing Algorithms for Processor Arrays 3-3 Developing Algorithms for MIMD Computers Categorization of MIMD Algorithms Factors That Limit Speedup  3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock 3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                             | 30        |

| Mesh-Connected SIMD Model Other SIMD Models Associative Processors  2-4 Multiprocessors and Multicomputers Tightly Coupled Multiprocessors Loosely Coupled Multiprocessors Loosely Coupled Multiprocessors Multicomputers  2-5 Parallel Computing Terminology Can Speedup Be Greater than Linear?  2-6 Amdahl's Law Revisited  2-7 Summary Bibliographic Notes Exercises  Chapter 3 Designing Parallel Algorithms  3-1 Generalities Insight Has an Important Role Communication Costs Must Be Considered The Algorithm Must Fit the Architecture  3-2 Developing Algorithms for Processor Arrays 3-3 Developing Algorithms for MIMD Computers Categorization of MIMD Algorithms Factors That Limit Speedup  3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock 3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                      | 30        |

| Other SIMD Models Associative Processors  2-4 Multiprocessors and Multicomputers Tightly Coupled Multiprocessors Loosely Coupled Multiprocessors Multicomputers  2-5 Parallel Computing Terminology Can Speedup Be Greater than Linear?  2-6 Amdahl's Law Revisited 2-7 Summary Bibliographic Notes Exercises  Chapter 3 Designing Parallel Algorithms  3-1 Generalities Insight Has an Important Role Communication Costs Must Be Considered The Algorithm Must Fit the Architecture  3-2 Developing Algorithms for Processor Arrays 3-3 Developing Algorithms for MIMD Computers Categorization of MIMD Algorithms Factors That Limit Speedup  3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock 3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                                                 | . 31      |

| 2-4 Multiprocessors and Multicomputers Tightly Coupled Multiprocessors Loosely Coupled Multiprocessors Multicomputers  2-5 Parallel Computing Terminology Can Speedup Be Greater than Linear?  2-6 Amdahl's Law Revisited  2-7 Summary Bibliographic Notes Exercises  Chapter 3 Designing Parallel Algorithms  3-1 Generalities Insight Has an Important Role Communication Costs Must Be Considered The Algorithm Must Fit the Architecture  3-2 Developing Algorithms for MIMD Computers Categorization of MIMD Algorithms Factors That Limit Speedup  3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock  3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                                                                                                                                        | 34        |

| Tightly Coupled Multiprocessors Loosely Coupled Multiprocessors Multicomputers  2-5 Parallel Computing Terminology Can Speedup Be Greater than Linear?  2-6 Amdahl's Law Revisited  2-7 Summary Bibliographic Notes Exercises  Chapter 3 Designing Parallel Algorithms  3-1 Generalities Insight Has an Important Role Communication Costs Must Be Considered The Algorithm Must Fit the Architecture  3-2 Developing Algorithms for Processor Arrays  3-3 Developing Algorithms for MIMD Computers Categorization of MIMD Algorithms Factors That Limit Speedup  3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock  3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                                                                                                                               | 35        |

| Loosely Coupled Multiprocessors Multicomputers  2-5 Parallel Computing Terminology Can Speedup Be Greater than Linear?  2-6 Amdahl's Law Revisited  2-7 Summary Bibliographic Notes Exercises  Chapter 3 Designing Parallel Algorithms  3-1 Generalities Insight Has an Important Role Communication Costs Must Be Considered The Algorithm Must Fit the Architecture  3-2 Developing Algorithms for Processor Arrays  3-3 Developing Algorithms for MIMD Computers Categorization of MIMD Algorithms Factors That Limit Speedup  3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock  3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                                                                                                                                                               | 35        |

| Multicomputers  2-5 Parallel Computing Terminology Can Speedup Be Greater than Linear?  2-6 Amdahl's Law Revisited  2-7 Summary Bibliographic Notes Exercises  Chapter 3 Designing Parallel Algorithms  3-1 Generalities Insight Has an Important Role Communication Costs Must Be Considered The Algorithm Must Fit the Architecture  3-2 Developing Algorithms for Processor Arrays  3-3 Developing Algorithms for MIMD Computers Categorization of MIMD Algorithms Factors That Limit Speedup  3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock  3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                                                                                                                                                                                               | 35        |

| 2-5 Parallel Computing Terminology Can Speedup Be Greater than Linear?  2-6 Amdahl's Law Revisited  2-7 Summary Bibliographic Notes Exercises  Chapter 3 Designing Parallel Algorithms  3-1 Generalities Insight Has an Important Role Communication Costs Must Be Considered The Algorithm Must Fit the Architecture  3-2 Developing Algorithms for Processor Arrays  3-3 Developing Algorithms for MIMD Computers Categorization of MIMD Algorithms Factors That Limit Speedup  3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock  3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                                                                                                                                                                                                               | 37        |

| Can Speedup Be Greater than Linear?  2-6 Amdahl's Law Revisited  2-7 Summary Bibliographic Notes Exercises  Chapter 3 Designing Parallel Algorithms  3-1 Generalities Insight Has an Important Role Communication Costs Must Be Considered The Algorithm Must Fit the Architecture  3-2 Developing Algorithms for Processor Arrays  3-3 Developing Algorithms for MIMD Computers Categorization of MIMD Algorithms Factors That Limit Speedup  3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock  3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                                                                                                                                                                                                                                                  | 41        |

| 2-6 Amdahl's Law Revisited 2-7 Summary Bibliographic Notes Exercises  Chapter 3 Designing Parallel Algorithms  3-1 Generalities Insight Has an Important Role Communication Costs Must Be Considered The Algorithm Must Fit the Architecture  3-2 Developing Algorithms for Processor Arrays  3-3 Developing Algorithms for MIMD Computers Categorization of MIMD Algorithms Factors That Limit Speedup  3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock  3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 42<br>44  |

| 2-7 Summary Bibliographic Notes Exercises  Chapter 3 Designing Parallel Algorithms  3-1 Generalities Insight Has an Important Role Communication Costs Must Be Considered The Algorithm Must Fit the Architecture  3-2 Developing Algorithms for Processor Arrays  3-3 Developing Algorithms for MIMD Computers Categorization of MIMD Algorithms Factors That Limit Speedup  3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock  3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 44      |

| Bibliographic Notes Exercises  Chapter 3 Designing Parallel Algorithms  3-1 Generalities Insight Has an Important Role Communication Costs Must Be Considered The Algorithm Must Fit the Architecture  3-2 Developing Algorithms for Processor Arrays 3-3 Developing Algorithms for MIMD Computers Categorization of MIMD Algorithms Factors That Limit Speedup  3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock 3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 43.<br>47 |

| Chapter 3 Designing Parallel Algorithms  3-1 Generalities Insight Has an Important Role Communication Costs Must Be Considered The Algorithm Must Fit the Architecture  3-2 Developing Algorithms for Processor Arrays 3-3 Developing Algorithms for MIMD Computers Categorization of MIMD Algorithms Factors That Limit Speedup  3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock 3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 48        |

| Chapter 3 Designing Parallel Algorithms  3-1 Generalities Insight Has an Important Role Communication Costs Must Be Considered The Algorithm Must Fit the Architecture  3-2 Developing Algorithms for Processor Arrays  3-3 Developing Algorithms for MIMD Computers Categorization of MIMD Algorithms Factors That Limit Speedup  3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock  3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 49        |

| 3-1 Generalities Insight Has an Important Role Communication Costs Must Be Considered The Algorithm Must Fit the Architecture 3-2 Developing Algorithms for Processor Arrays 3-3 Developing Algorithms for MIMD Computers Categorization of MIMD Algorithms Factors That Limit Speedup 3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages 3-5 Deadlock 3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |

| Insight Has an Important Role Communication Costs Must Be Considered The Algorithm Must Fit the Architecture  3-2 Developing Algorithms for Processor Arrays  3-3 Developing Algorithms for MIMD Computers Categorization of MIMD Algorithms Factors That Limit Speedup  3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock  3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 51        |

| Communication Costs Must Be Considered The Algorithm Must Fit the Architecture  3-2 Developing Algorithms for Processor Arrays  3-3 Developing Algorithms for MIMD Computers Categorization of MIMD Algorithms Factors That Limit Speedup  3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock  3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 52        |

| The Algorithm Must Fit the Architecture  3-2 Developing Algorithms for Processor Arrays  3-3 Developing Algorithms for MIMD Computers Categorization of MIMD Algorithms Factors That Limit Speedup  3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock  3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 52        |

| 3-2 Developing Algorithms for Processor Arrays 3-3 Developing Algorithms for MIMD Computers Categorization of MIMD Algorithms Factors That Limit Speedup 3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages 3-5 Deadlock 3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 53      |

| 3-3 Developing Algorithms for MIMD Computers Categorization of MIMD Algorithms Factors That Limit Speedup 3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages 3-5 Deadlock 3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 53        |

| Categorization of MIMD Algorithms Factors That Limit Speedup  3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock  3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 53<br>57  |

| Factors That Limit Speedup  3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock 3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 58        |

| 3-4 Process Communication and Synchronization on MIMD Models Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock 3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 60        |

| Communication and Synchronization Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock 3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |

| Expressing Concurrency Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock 3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 64        |

| Synchronizing with Shared Variables Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock 3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 64        |

| Low-Level Synchronization through Message Passing Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock 3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 66        |

| Remote Procedure Call Classifying Concurrent Programming Languages  3-5 Deadlock 3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 69        |

| 3-5 Deadlock 3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 70        |

| 3-6 Task Scheduling on MIMD Computers Deterministic Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 71        |

| Deterministic Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 72        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 73        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 73        |

| Nondeterministic Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 75        |

| •          |                                                                     | CONTENTS XI           |

|------------|---------------------------------------------------------------------|-----------------------|

| 2.7        | Summary                                                             | . 77                  |

| 3-1        | Bibliographic Notes                                                 | 78                    |

|            | Exercises                                                           | 79                    |

| Chapter 4  | Sorting and the Fast Fourier Transform                              | 81                    |

| 4-1        | Bitonic Merge                                                       | 82                    |

| 4-2        | Sorting on Processor Arrays                                         | 88                    |

|            | Sorting on the SIMD-MC <sup>1</sup> Model                           | 88                    |

|            | Sorting on the SIMD-MC <sup>2</sup> Model                           | . 89                  |

|            | Sorting on the SIMD-CC Model                                        | 93                    |

|            | Sorting on the SIMD-PS Model                                        | 94<br>95              |

| 4-3<br>4-4 | A Multiprocessor Implementation of Quicksort Fast Fourier Transform | بر <del>د</del><br>97 |

| 4-4        |                                                                     | 102                   |

| 4-5        | Bibliographic Notes                                                 | 103                   |

|            | Exercises                                                           | 105                   |

| Chapter 5  | Dictionary Operations                                               | 107                   |

| 5-1        | Complexity of Parallel Search                                       | 108                   |

| 5-2        |                                                                     | 110                   |

|            | Ellis's Algorithm                                                   | 110                   |

|            | Manber and Ladner's Algorithm                                       | 114                   |

| 5-3        |                                                                     | 118                   |

| •          | Bibliographic Notes                                                 | 120                   |

|            | Exercises                                                           | 121                   |

| Chapter 6  | Matrix Multiplication                                               | 123                   |

|            | Sequential Matrix Multiplication                                    | 123                   |

| 6-1        | Algorithms for Processor Arrays                                     | 124                   |

|            | Matrix Multiplication on the SIMD-MC <sup>2</sup> Model             | 124                   |

|            | Matrix Multiplication on the SIMD-CC Model                          | 127                   |

| 6-2        | Matrix Multiplication on the SIMD-PS Model                          | 129<br>129            |

| 6-3        | •                                                                   | 133                   |

| 0-5        | Bibliographic Notes                                                 | 134                   |

| ,•         | Exercises                                                           | 135                   |

| Chapter 7  | Numerical Algorithms                                                | 137                   |

| 7-1        |                                                                     | 138                   |

| 7-2        |                                                                     | 140                   |

| 7-3        | - · · · · · · · · · · · · · · · · · · ·                             | 142                   |

| 7-4        | ·                                                                   | 146                   |

| 7-5        |                                                                     | 150                   |

|            | Bibliographic Notes                                                 | 151                   |

|            | Exercises                                                           | 151                   |

#### xii CONTENTS

| Chapter 8  | Graph Algorithms                                   | 153   |

|------------|----------------------------------------------------|-------|

| 8-1        | Terminology                                        | 154   |

| 8-2        | Algorithms for Processor Arrays                    | 156   |

|            | Searching a Graph                                  | 156   |

|            | Connected Components                               | . 160 |

|            | All-Pairs Shortest Path                            | 165   |

| 8-3        | Algorithms for Multiprocessors                     | 165   |

|            | Minimum Spanning Tree                              | 165   |

| , , ,      | Single-Source Shortest Path                        | 171   |

| 8-4        | Summary                                            | 177   |

|            | Bibliographic Notes Exercises                      | 178   |

|            | Exercises                                          | 180   |

| Chapter 9  | Combinatorial Search                               | 183   |

| 9-1        | Divide and Conquer                                 | 185   |

| 9-2        | Branch and Bound                                   | 185   |

|            | Traveling Salesperson Problem                      | 189   |

|            | Anomalies in Branch and Bound                      | 193   |

| 9-3        | Alpha-Beta Search                                  | 195   |

|            | Parallel Alpha-Beta Search                         | 201   |

| 9-4        | Summary                                            | 202   |

| •          | Bibliographic Notes                                | 203   |

|            | Exercises                                          | 204   |

| Chapter 10 | Logic Programming                                  | 205   |

| 10-1       | Logic Programming                                  | 205   |

| 10-2       | Prolog                                             | 207   |

|            | Potential Parallelism in Prolog                    | 212   |

| 10-3       | Concurrent Prolog                                  | 213   |

| 10-4       | <del></del>                                        | 214   |

| 10-5       | Summary                                            | 217   |

|            | Bibliographic Notes                                | 218   |

|            | Exercises                                          | 218   |

| Chapter 11 | Pipelined Vector Processors                        | 221   |

| 11-1       | Vector Computers                                   | 222   |

| 11-2       | Pipelined Vector Processors                        | 224   |

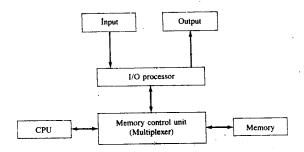

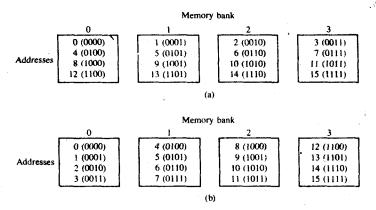

|            | Memory Organization                                | 225   |

| 11-3       | The Cray-1                                         | 22:   |

|            | The Cray X-MP                                      | 22    |

| 11-4       | ,                                                  | 228   |

| 11-5       |                                                    | 230   |

| 11-6       |                                                    | 23:   |

| 11-7       |                                                    | 23:   |

|            | Matrix Multiplication One-Dimensional Table Lookup | 230   |

|            | i ine-i ilmentional Table Lookiin                  | 74    |

| 11-8 | Attached Processors   | 238 |

|------|-----------------------|-----|

| 11-0 | FPS-164/MAX           | 239 |

|      | Matrix Multiplication | 239 |

| 11-9 | Summary               | 241 |

| ,    | Bibliographic Notes   | 242 |

|      | Exercises             | 242 |

|      | Glossary              | 245 |

|      | Bibliography          | 257 |

|      | Index                 | 279 |

CONTENTS XIII

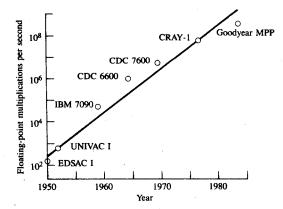

## INTRODUCTION

This book is concerned with parallel computing, the process of solving problems on parallel computers. Parallel computing is a relatively young field: the Illiac IV, a processor array, became operational in 1975; the first Cray-1, a pipelined vector processor, was telivered in 1976; and low-cost multiprocessors were not available before 1984. The advent of very large-scale integration (VLSI) heralded a new era in computing: not only did it make the personal computer possible, but also it made practical the development of large-scale computing devices consisting of tens, hundreds, even thousands of processors, all working together to perform a computation.

Although the study of parallel computing is a new discipline, it is far from unimportant. Many programs that run well on conventional computers are not easily transformed to programs that efficiently harness the capabilities of parallel computers. Conversely, algorithms that are less efficient in a sequential context often reveal an inherent parallelism that makes them attractive bases for parallel programs.

Many claim we are entering "the decade of the parallel computer." Applications demand computers that are many orders of magnitude faster than the fastest computers available today. Parallelism represents the most feasible avenue to achieve this kind of breakthrough, and countries throughout the western world are vigorously developing ever more powerful parallel computers. Some of these computers are quite expensive: the Connection Machine, marketed by Thinking Machines Corporation, contains up to 65,536 processors and costs \$3 million. Other parallel computers cost little more than professional work stations. Low-cost multiprocessors and multicomputers have been announced by Ametek, Aretè, Encore, Intel, NCUBE, Sequent, and other companies.

The remainder of this chapter puts the problem of parallel computing in context. Section 1-1 lists a few applications that demand computers much faster than those presently available. Section 1-2 presents a brief history of architectural advances used to increase the performance of computers over the past 35 years. This section also explores the difference between pipelining and parallelism. Section 1-3 introduces the architectural classification schemes of Flynn and Händler. Finally, Section 1-4 examines reasons that have traditionally been given opposing the feasibility of high-level parallel computation. Some of these reasons can now be refuted easily; others are more weighty. It is good to remember that it takes a special kind of creativity to unleash the full power of a parallel architecture. Perhaps that is the best reason to study parallel computing: Success is more difficult and hence more rewarding.

# 1-1 THE NEED FOR HIGHER-PERFORMANCE COMPUTERS

The increasing power of computers has led to greater visions of what they might be able to do. Hwang and Briggs [1984] point out that mainstream computer usage is gradually becoming more and more sophisticated, progressing from data processing and information processing to knowledge processing and, eventually, intelligence processing. Each level of increasing sophistication demands much more powerful computers. We consider a few examples of current applications that could use extremely powerful computers. Although most of these applications are using computers for "number crunching," other applications are using computers to manipulate symbols or ideas. Hwang and Briggs [1984] are the primary source of information for these examples; their text contains more information about these and other uses.

#### Weather Prediction

Forecasting the weather on a computer requires the solution of general circulation model equations in a spherical coordinate system. A three-dimensional grid partitions the atmosphere by altitude, latitude, and longitude. Time is the fourth dimension; it, too, is partitioned by specifying a time increment. Given a grid with 270 miles on a side and an appropriate time increment, about 100 billion operations must be performed to compute a 24-hour forecast. This can be done in about 100 minutes on a computer capable of performing 100 million operations per second, such as a Cray-1. A grid this coarse is capable of producing a forecast for New York and Washington, D.C., but not for Philadelphia, located approximately halfway between the other two cities. To get a more accurate forecast for Philadelphia, the grid size would have to be halved in all four dimensions, leading to a 16-fold increase in the number of computations required. A computer capable of 100 million floating-point operations per second (100 megaflops), like the Cray-1, would require 24 hours to complete the 24-hour

forecast. Even this new grid size would not be sufficiently fine to allow reliable long-range forecasting. If we want to receive accurate long-range forecasts, much more powerful computers must be developed.

## Computational Aerodynamics

Wind tunnel experiments have a number of fundamental limitations. These include the model size, wind velocity, density, temperature, wall interference, and other factors. Numerical flow simulations have none of these limitations. The replacement of wind tunnels by computers has been limited only by the processing speed and memory capacity of the computer being used. The Burroughs Corporation and Control Data Corporation have proposed supercomputers, known as the numerical aerodynamic simulation facilities, with the goal of eliminating the need for wind tunnels. These supercomputers are designed to perform more than a billion floating-point operations per second (gigaflops).

Researchers at the University of Illinois, supported by a grant from the National Science Foundation, have begun using supercomputers to study wind shear. Using computational aerodynamics to "fly" simulated airplanes through microbursts, they hope to learn more about microbursts and the dangers posed to commercial aviation [USA Today 1985].

### **Artificial Intelligence**

Most current computers have a relatively inflexible input/output (I/O) interface. If computers are to become more "user-friendly," they must be able to interact with humans at a higher level, using speech, pictures, and natural language. Allowing voice, pictorial, and natural language input to be handled in real time requires an enormous amount of computing power, much more than is available on standard architectures.

Japan has begun a project to develop fifth-generation computers. One of the goals of the project is to build a computer capable of making 100 million to 1 billion logical inferences per second. Since one logical inference may take anywhere from 100 to 1000 machine instructions to execute, such a machine would have to be able to perform between 10 billion and 1 trillion instructions per second.

### Remote Sensing

The analysis of earth-resource data broadcast from satellites has many applications in agriculture, ecology, forestry, geology, and land use planning. However, images are often so large that even simple calculations require large amounts of CPU time. For example, a single Thematic Mapper image from the latest Landsat satellite is a 6000-picture element (pixel) by 6000-pixel square. Each pixel is represented by 8 bits; the entire picture is made up of eight images, or bands. A single picture, then, is represented by 288 megabytes of information.

NASA has installed the Massively Parallel Processor (MPP), manufactured by Goodyear Aerospace, to perform satellite image processing.

#### **Nuclear Reactor Safety**