# The 13th International Symposium on Multiple-Valued Logic

Proceedings

73.87237000

# THE THIRTEENTH INTERNATIONAL SYMPOSIUM ON MULTIPLE-VALUED LOGIC

May 23-25, 1983 Holiday Inn Kyoto, Japan

## **SPONSORING ORGANIZATIONS**

IEEE Computer Society

ISMVL-83

ISMVL-Japan

U.S. A.F.O.S.R.

ISSN NUMBER 0-05-623X

IEEE CATALOG/NUMBER 3-0-11885-3

LIBRARY OF CONGRESS NUMBER 79-641110

IEEE COMPUTER SOCIETY ORDER NUMBER 471

IEEN NUMBER 0-8186-0016-0

Additional copies available from:

IEEE Computer Society P.O. Box 80452 Worldway Postal Center Los Angeles, CA 90080

**IEEE Service Center** 445 Hoes Lane Piscataway, NJ 08854

Copyright 1983 The Institute of Electrical and Electronics Engineers, Inc.

8750124

International Symposium on Multiple-Valued Logic.

Proceedings - International Symposium on Multiple -Valued Logic. 1st-

1971-

[New York, etc., IEEE] v. iii. 28 cm. annual.

Title varies slightly.

Symposia for 1971sponsored by the Institute of Electrical and Electronics Engineers and other related bodies; 1979-by the IEEE Computer Society. Key title: Proceedings - International Symposium on Multiple

-Valued Logic, ISSN 0195-623X.

I. Institute of Electrical 1. Many-valued logic-Congresses. and Electronics Engineers. II. IEEE Computer Society. III. Key

QA9.45.1 57a

511.3

79-641110 MARC-S

Library of Congress

79

**Published by IEEE Computer Society Press** 1109 Spring Street Suite 300 Silver Spring, MD 20910

Copyright and Reprint Permissions: Abstracting is permitted with credit to the source. Libraries are permitted to photocopy beyond the limits of U.S. copyright law for private use of patrons those articles in this volume that carry a code at the bottom of the first page, provided the per-copy fee indicated in the code is paid through the Copyright Clearance Center, 21 Congress Street, Salem, MA 01970. Instructors are permitted to photocopy isolated articles for noncommercial classroom use without fee. For other copying, reprint or republication permission, write to Director, Publishing Services, IEEE, 345 E. 47 St., New York, NY 10017. All rights reserved. Copyright © 1983 by The Institute of Electrical and Electronics Engineers, Inc.

> ISSN Number 0195-623X IEEE Catalog Number 83CH1885-3 Library of Congress Number 79-641110 IEEE Computer Society Order Number 471 ISBN Number 0-8186-0016-0

Order from: IEEE Computer Society

Post Office Box 80452 Worldway Postal Center Los Angeles, CA 90080

**IEEE Service Center** 445 Hoes Lane Piscataway, NJ 08854

The Institute of Electrical and Electronics Engineers, Inc.

## General Chairman's Message

The 1983 International Symposium on Multiple-Valued Logic is the thirteenth meeting in a series of annual symposia devoted exclusively to multiple-valued logic. Ten of the past meetings were held in North America, the other two in Europe. The ISMVL-83 in Kyoto, Japan, is the first symposium to be held in Asia. It is dedicated to the investigation of multiple-valued logic to narrow the gap between theory and practice.

The ISMVL-83 is sponsored jointly by the Multiple-Valued Logic Technical Committee of the IEEE Computer Society and ISMVL-Japan. I would like to express my sincere appreciation to both of these bodies.

Planning and organizing for the ISMVL-83 began three years ago. It took many meetings and discussions for solving various problems to reach this stage of welcoming you here in Kyoto. We are indebted to all those whose hard work, dedication, and enthusiasm have made this symposium possible.

I am especially thankful to Professor Y. Tezuka, Chairman of the Steering Committee, Professor T. Kitahashi, Symposium Chairman, and Professor J.T. Butler, Symposium Co-Chairman, for their sincere cooperation, tireless work, and good guidance. Special thanks are also due to Professor M. Goto, Honorary Member of the General Organizing Committee, for his continuing encouragement and invaluable suggestions. It should be emphasized that Professor Goto's pioneering work on multiple-valued logic has led us to hold the ISMVL-83 in Kyoto, Japan.

The Program Committee, under the chairmanship of Professor T. Higuchi with co-chairmen Professor K. Wayne Current and Dr. S.L. Hurst, has put together the outstanding ISMVL-83 program. I am grateful to all members of the Program Committee for their extraordinary effort in organizing the program.

This symposium could not have been held without the support of the many Japanese companies that have donated money to the ISMVL-83. We would like to express our hearty appreciation to them.

Finally, I would like to thank the members of the Organizing Committee of ISMVL-Japan, listed on page vii of this Proceedings, for their generous support.

Hisashi Mine Kyoto University

## Symposium Chairman's Message

the 1983 International Symposium on Multiple-Valued Logic in 770 to, Japan, is the first to be held in Asia. Because there are many researchers in Japan and neighboring countries, this symposium offers a unique opportunity for a large number of multiple-valued logic researchers to meet. An Asian conference will encourage the technological development of mainland China, where there are 3000 mathematicians engaged in the study of fuzzy logic. In addition to many speakers from Japan, we have several newcomers from Thailand, China, and Nigeria.

An Asian conference is appropriate for another reason. Sophisticated logics, such as multiple-valued and fuzzy logic inherit certain characteristics of Oriental philosophy. It is especially appropriate that the first Asian conference be held in Japan, since Professor M. Gold's pioneering work on multiple-valued logic was done here.

This conference is sponsored by the Organization for ISMVL-Japan, the IEEE Computer Society, and the Society's Technical Committee on Multiple-Valued Logic. Operating funds in Japan were provided by many Japanese industries. We are grateful for the generous support of the United States Air Force Office of Scientific Research, which provided funds for the travel of eight U.S. scientists and operating costs in the United States.

We want to recognize the great support of J.T. Butler, Symposium Co-Chairman, and T. Sasao, General Secretary of ISMVL-83, for introducing the Symposium to Japan. Without their efforts, this apposium could not have been held here.

An essential ingredient of any conference is the technical program. We are truly grateful for the continual help and outstanding work of S.L. Hurst, Program Co-Chairman for Europe. Many papers were submitted by North American researchers, and we are grateful for the efforts of W.C. Current, Program Co-Chairman for North America, for processing these papers. Professor Higuchi, General Program Chairman, deserves a special thank you for handling the many papers from Asian authors, as well as for morrdinating the entire program.

Professor Higuchi would like to express his since appreciation to the referees, whose intensive particular and critical comments provided the basis on which decisions of paper acceptance or rejection were based. We also thank the authors, whose research results are the basis for whis conference.

Tadahiro Kitahashi ISMVL-83 Toyohashi University of Technology

ν

### Organizing Committee

Chairman:

Hisashi Mine

Department of Applied Mathematics and Physics

Kyoto University, Kyoto, Japan

Co-Chairman:

Yoshikazu Tezuka

Department of Electrical Communications

Osaka University, Suita, Japan

Members: Motinori Goto

(Meiji University, Japan) Toshiharu Hasegawa (Kyoto University, Japan) (Tohoku University, Japan) (Waseda University, Japan) Tatsuo Higuchi Hiroshi Hirayama

Masayuki Kimura (Tohoku University, Japan)

Tadahiro Kitahashi (Toyohashi University of Technology, Japan)

Yoshiaki Koga

(National Defense Academy, Japan) (Kyushu University, Japan)

Yasuo Komamiya Masao Mukaidono Akira Nakamura Ryosaku Shimada

(Meiji University, Japan) Matsuroh Nakamichi (Chiba University, Japan) (Hiroshima University, Japan) (Tokushima University, Japan) (Nihon University, Japan)

Masaichi Tanaka Tatsuki Watanabe

(Toyo University, Japan)

## Executive Committee

Chairman:

Yoshikazu Tezuka

Department of Electrical Communications

Osaka University, Suita, Japan

Symposium

Chairman:

Tadahiro Kitahashi

School of Information and Computer Sciences

Toyohashi University of Technology, Toyohashi, Japan

Symposium

Co-Chairman:

Jon T. Butler

Department of Electrical Engineering and Computer Science

Northwestern University, Evanston, Illinois, U.S.A.

Program

Chairman:

Tatsuo Higuchi

Department of Electronic Engineering Tohoku University, Sendai, Japan

American

Program Co-Chairman:

K. Wayne Current

Department of Electrical Engineering

University of California-Davis, Davis, California, U.S.A.

European

Program

Co-Chairman:

Stanley L. Hurst

School of Electrical Engineering University of Bath, Bath, England

Treasurer: Masao Mükaidono

(Meiji University, Japan)

General

Secretary: Tsutomu Sasao

(Osaka University, Japan)

Publicity: Okihiko Ishizuka

(Miyazaki University, Japan)

Publication: Michitaka Kameyama (Tohoku University, Japan)

# REFEREES

| T. Aihara                  |

|----------------------------|

| C.M. Allen                 |

| J.R. Armstrong             |

| J.F. Baldwin               |

| A. Beach                   |

| R.G. Bennetts              |

| J. Berman                  |

| J.E. Beynon                |

| M.A. Breuer                |

| J.T. Butler                |

| C. Carlsson                |

| W. Coy                     |

| S.C. Crist                 |

| F. Curl                    |

| K.W. Current               |

| T.T. Dao                   |

| S. Dhar                    |

| J.H. Efstathiou            |

| C. Epstein                 |

| D. Etiemble                |

| K. Fang<br>S. Fujita       |

| S. Fujita                  |

| Y. Fujita                  |

| M. Goto                    |

| S. Gottwald                |

| S. Gottwald<br>S. Guccioni |

| A.S. Gupta                 |

| G. Hachimine               |

| T. Haga                    |

| S.B. Haley                 |

| T. Hasegawa                |

| T. Hasegawa<br>T. Hikita   |

| S.J. Hong                  |

| J.L. Huertas               |

| S.L. Hurst                 |

| S. Imanishi                |

|                            |

| O Tabianto                                            |

|-------------------------------------------------------|

| O. Ishizuka<br>M. Israel<br>W.C. Kabat<br>L.J. Kahout |

| W.C. Kabat                                            |

| I. I Kahout                                           |

| A. Kalis                                              |

| M. Kameyama                                           |

| A. Kandel                                             |

| M. Karpovsky                                          |

| M. Katz                                               |

| L. Kauffman                                           |

| H.G. Kerkhoff, Jr.                                    |

| T. Kitahashi                                          |

| Y. Koga                                               |

| S.C. Lee                                              |

| P. Ligomenides                                        |

| A.W. Maholick                                         |

| E. Mandani                                            |

| J. Mangin                                             |

| E.J. McCluskey                                        |

| Y. Miki                                               |

| M. Mizumoto                                           |

| D.M. Miller                                           |

| C. Moraga                                             |

| H.T. Mouftah                                          |

| M. Mukaidono                                          |

| S. Muta<br>N. Muranaka<br>J. Muzio<br>M. Nakamichi    |

| N. Muranaka                                           |

| J. Muzio                                              |

| M. Nakamichi                                          |

| A. Nakamura<br>Y. Ohkura                              |

| I. Okumura                                            |

| S. Okumura S. Ovchinnikov                             |

| C. A. Danashada                                       |

| C.A. Papachristou                                     |

| P.D. Picton<br>B.W. Pilsworth                         |

| D.W. PIISWOTEN                                        |

|                                                       |

| J. Pla                      |

|-----------------------------|

| J.H. Pugsley                |

| D. Ralescu                  |

| H. Rasiowa                  |

| D.C. Rine                   |

| A. Rose                     |

| I.G. Rosenberg              |

| N. Sanechika                |

| T. Sasao                    |

| R. Shimada                  |

| C.B. Silio                  |

| D. Simovici                 |

| B. Si*ha<br>M. Sinutko, Jr. |

| M. Sinutko, Jr.             |

| W.E. Stein                  |

| R.E. Swartwout              |

| S. Termini                  |

| A. Thayse                   |

| M. Togai                    |

| N. Tomabechi                |

| E. Trillas                  |

| J.G. Tront                  |

| M.P. Tull                   |

| F. Ueno                     |

| Z.G. Vranesic               |

| T. Wesselkamper             |

| L.B. Wheaton                |

| W. Wojcienchowski           |

| A.S. Wojcik                 |

| R.R. Yaeger                 |

| Y. Yamamoto                 |

| Y. Yamamoto<br>K. Yamato    |

| T.C. Yang                   |

| L.n. Lauen                  |

| H.J. Zimmermann             |

|                             |

# TABLE OF CONTENTS

| General Chairman's Message                                                                                                 | iii  |

|----------------------------------------------------------------------------------------------------------------------------|------|

| Symposium Chairman's Message                                                                                               | v    |

| Organizing and Executive Committees                                                                                        | vii  |

| Referees                                                                                                                   | viii |

| <pre>Invited Address Completeness for Uniformly Delayed Circuits</pre>                                                     | 2    |

| Session 1A: Logic Design I A Study of Reduced Dependence in Multi-Valued Sequential Machines                               |      |

| T.C. Yang and A.S. Wojcik A Preprocessing Procedure Method in                                                              | . 12 |

| Ternary Clause Selection                                                                                                   | 21   |

| with Built-in Testing Capability                                                                                           | 28   |

| Session 1B: Philosophy I Axiomatic Characterization and Comparative Analysis of                                            |      |

| Preference on Desirability and Possibility                                                                                 | 36   |

| Quotient Algebras for Logics of Imprecision                                                                                | 42   |

| In the Labyrinth of Many Valued Logics                                                                                     | 47   |

| Session 2A: Circuit and Technology I The New Method of Implementation for                                                  |      |

| Ternary Logic System                                                                                                       | 56   |

| Logic Functions                                                                                                            | 61   |

| Low Power 2-of-3-Valued CMOS Self-Checking Circuits M. Hu, K.C. Smith, and H.T. Mouftah                                    | 64   |

| Session 2B: Threshold Logic Synthesis of Multivalued Logic Circuits Using Hyperplanes                                      | 72   |

| T. Watanabe and M. Matsumoto<br>p-Valued Input, q-Valued Output Threshold Logic<br>and Its Application to the Synthesis of |      |

| p-Valued Logical Networks                                                                                                  | 78   |

| Four or Less Variables                                                                                                     | 84   |

| Session 3A: Logic Design II On the Number of Locations Required in the Content-Addressable Memory Implementation of                                |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Multiple-Valued Functions                                                                                                                          | 94  |

| Expressions of Multiple-Valued Input Binary Functions                                                                                              | 103 |

| The Simplification of Multiple-Valued  Symmetric Functions                                                                                         | 111 |

| Session 3B: Algebra I Selfdual Classes and Automorphism Groups                                                                                     | 122 |

| Automorphism Groups                                                                                                                                | 126 |

| (Quasi)Transitive Algebras                                                                                                                         | 129 |

| Invited Address The Implementation and Use of Multivalued Logic in a VLSI Environment                                                              | 138 |

| H. Fleisher                                                                                                                                        |     |

| Session 4A: Charge-Coupled Devices and Applications Pulse Train Residue Arithmetic Circuit Using Multiple-Valued Charge-Coupled Devices            |     |

| and Its Application to Digital Filter                                                                                                              | 146 |

| N. Tomabechi, M. Kameyama, and T. Higuchi Tolerance Analysis and Related Measurements on MVL-CCD's H.G. Kerkhoff, J. de Groot, and A.C. Brombacher | 152 |

| Tabular Methods for the Design of CCD Multiple-Valued Circuits                                                                                     | 162 |

| Session 4B: Switching Theory                                                                                                                       |     |

| Synthesis Method for Ternary Logic Function Based on NAND-Type Polypheck M. Yanagita, N. Fukuda, Y. Miyoshi, K. Nakashima,                         | 172 |

| and K. Yamato Vector Expansion Transformation of Logic Algebra                                                                                     | 177 |

| Z. Liu and Y. Yuan Roots of N-Valued Switching Functions                                                                                           | 183 |

| Session 5A: Circuit and Technology II A Quaternary Logic Encoder-Decoder Circuit                                                                   |     |

| Design Using CMOS                                                                                                                                  | 190 |

| D.A. Freitas and K.W. Current                                                                                                                      |     |

| Realization and Analysis of a Mask-Programmable I <sup>-</sup> L Multivalued Logic Circuit                                                         | 196 |

| Logic-Type Schmitt Circuit Using Mult1-Valued Gates F. Wakui and M. Tanaka                                                | 201         |

|---------------------------------------------------------------------------------------------------------------------------|-------------|

| Session 5B: Philosophy II  A General Method for the Evaluation of Degree of Completeness                                  | 208         |

| A. Rose Three-Valued Logic and Its Application to the Query Language of Incomplete Information                            | 214         |

| A. Nakamura Towards a Formal Multi-Valued Utility Theory                                                                  | 219         |

| An Approach to Fuziness in the Setting of Lukasiewicz Logic                                                               | 222         |

| Invited Address Synthesis of Axiom Systems for the Three-Valued Predicate Logic by Means of the Special Four-Valued Logic | 228         |

| Session 6A: System Design and Applications Image Processing Algorithms for a Multiple-Valued Array Processor              | 236         |

| M. Kameyama, K. Suzuki, and T. Higuchi Ternary Transmission in Local Area Networks                                        | 242         |

| Some Device Count Comparisons for Reduced Control Stores Using Multiple-Valued MOS Circuits                               | 249         |

| C.B. Silio, Jr. and J.H. Pugsley A Quaternary Cellular Array Complex Number Multiplier T.T. Dao                           | 255         |

| Session 6B: Fuzzy Logic A Comparison of Fuzzy Switching Functions and Multiple-Valued Switching Functions                 | 264         |

| Fuzzy Reasoning under New Compositional Rules of Inference                                                                | 273         |

| M. Mizumoto A Study of Fuzzy Relations and Their Inverse Problem M. Togai and P.P. Wang                                   | 279         |

| Regular Ternary Logic FunctionsTernary Logic Functions Suitable for Treating Ambiguity                                    | 286         |

| Session 7A: Reliable Design Cyclic ST-AN Codes and Modular ST Distance                                                    | 29 <b>4</b> |

| Subfunction                                                                                                               | 300         |

| Maximum Number of Spikes in Combinational and Sequential Circuits                                                         | 3Ø6         |

| Four-Valued Logic, Star Algorithm and Their Applications T. Chen, Y. Yuan, Z. Liu, and Z. Zhang                               | 314 |

|-------------------------------------------------------------------------------------------------------------------------------|-----|

| Session 7B: Algebra II Mx, A Mix-Valued Algebra                                                                               | 328 |

| A Minimization Method for Engineering Estimation                                                                              | 337 |

| The Optimization of GMC over GF(p) D. Fing                                                                                    | 342 |

| Session 8A: Detection and Diagnosis Relations among System Diagnosis Models                                                   |     |

| with Three-Valued Test Outcomes                                                                                               | 350 |

| On System Diagnosis with Multivalued Test Outcomes                                                                            | 356 |

| A Method of Test Generation for Verification of Wiring Correctness                                                            | 361 |

| Session 8B: Logic Design III Automated Design of Combinational Networks under Specific Contraints: A Theorem Proving Approach | 366 |

| Synthesis of Multiple-Valued Logic Functions Based on a Modular Design Approach                                               | 397 |

| Synthesis Algorithm for Minimal Components in T-ULM Networks                                                                  | 4Ø8 |

| <pre>Invited Address A Fuzzy Relational Inference Language for Expert Systems J.F. Baldwin</pre>                              | 416 |

| Late Paper The Suntherie of Mernary Functions under Fixed                                                                     |     |

| The Synthesis of Ternary Functions under Fixed Polarities and Ternary I L Circuits                                            | 424 |

| Author Index                                                                                                                  | 431 |

# **Invited Address**

## COMPLETENESS FOR UNIFORMLY DELAYED CIRCUITS

## I. G. Rosenberg\* and T. Hikita\*\*

\* C.R.M.A., Université de Montréal, Montréal, P.Q. H3C 3J7, Canada \*\* Dept. of Math., Tokyo Metropolitan University, Setagaya, Tokyo 158, Japan

#### Abstract

The paper reports on the progress towards an effective completeness criterion for uniformly delayed multiple-valued combinatorial circuits. In view of previous work by HikitaeNozaki and Hikita it suffices to study periodic closed spectra. The main tool is the use of polyrelations (= sequences of relations on  $\underline{k} := \{0, \ldots, k-1\}$ ) and certain constructions on polyrelations developed by Hikita. We were able to restrict the search to unary polyrelations (almost solved) and three types of binary polyrelations:

- 1) period  $2^m$ ,  $\rho_0$  bounded order,  $\rho_2^{m-1}$  its converse and  $\rho_i = \iota_2 := \{(a, a) \mid a \in \underline{k}\}$  otherwise,

- 2) every nonempty component is of the form  $\{(a, s(a)) \mid a \in \underline{k}\}$  where s is a permutation of  $\underline{k}$ ; the permutations are interrelated,

- 3) components are either (i) all equivalences on  $\underline{k}$  or (ii) all central or  $=\underline{k}^2$ . In both cases they have strong properties in terms of intersecting cliques.

## 1. Introduction

This paper reports on the progress towards an effective completeness criterion for uniformly delayed circuits (this and other rather technical concepts are fully explained in section 2). In the historical retrospective the topic was introduced rather early by Kudrjavcev in 1960 who defined the various basic concepts and gave an effective completeness criterion for the uniformly delayed binary circuits based on precomplete classes [10, 11]. (For the ordinary non-delayed circuits and logic such a criterion was given by Post [25] for k = 2, Jablonskii [8] for k = 3, the first author for  $k \ge 3$  [26-28] and the idea of a precomplete class by Kuznecov [15, 16].) Some of Kudrjavcev's results were rediscovered by Loomis [17]. Other completeness aspects for delayed circuits were studied by Birjukova and Kudrjavcev [2].

After this early Russian start the focus moved to Japan where Nozaki and his school took up and expanded the study of multiple-valued delayed circuits, to the extent that during the past 12 years all papers in this domain (with the lone exception of [18]) were published by the Japanese school. For

uniformly delayed circuits the breakthrough came in Hikita and Nozaki's 1977 paper [7] which reduced the problem to three more manageable types. The first case (type A) is directly solved by Rosenberg's 1965 primality criterion while the third case (type C) was solved by Hikita in 1979 [6]. Meanwhile Hikita also completely classified the ternary case [4] and gave a relational theory for uniformly delayed circuits [5]. This is based on infinite sequences  $\rho = (\rho_0, \rho_1, \dots)$  of relations on the alphabet  $k := \{0, 1, \dots, k-1\}$  of the same arity. For such a sequence, called a polyrelation, an n-ary operation f with nonnegative integer delay  $\delta$  carries  $(\rho_i)^n$  into  $\rho_{i+\delta}$  for all  $i \geq 0$ . This concept replaces the preservation of a single relation which is the basic concept in the non-delayed case.

This address reports on the results towards solving the remaining case of periodic spectra (type B) and the corresponding periodic polyrelations. The precomplete classes obtained are rather exceptional as witnessed by the fact that they are determined by at most binary polyrelations. We have succeeded in limiting them to unary periodic polyrelations (almost solved) and binary polyrelations  $\rho = (\rho_0, \rho_1, \ldots)$  of period p of the following three types:

- 1)  $p=2^m$  (m>0),  $\rho_0$  is a bounded partial order  $\leq$ ,  $\rho_{2^{m-1}}$  is  $\geq$ , and  $\rho_i=\iota_2:=\{(a,a)\mid a\in\underline{k}\}$  for  $0< i<2^m$ ,  $i\neq 2^{m-1}$ . Each of these polyrelations gives a precomplete class [11, 18].

- 2) Every nonempty component is of the form  $\{(a, s(a)) \mid a \in \underline{k}\}$  where s is a permutation of  $\underline{k}$ . The permutations involved are intimately linked and the case is essentially of a group-theoretical nature to be explored in the future.

- 3) All components  $\rho_0$ , ...,  $\rho_{p-1}$  are either equivalences  $\neq 1_2$  or all are central or  $= \frac{k^2}{2}$  (a symmetric relation  $\sigma$  is central if  $1_2 \subseteq \sigma \subset \underline{k}^2$  and  $c \times \underline{k} \subseteq \sigma$  for some  $c \in \underline{k}$ ). In both cases we have strong properties in terms of intersecting cliques which are too complex to be explained here.

The full paper seems to be too long to be included in the proceedings and so we opted for a compromise: we list only definitions and propositions. The preprint of the full paper will be available at

the Symposium and may be obtained by writing to either of the authors.

The project for this work was conceived during A. Nozaki's and T. Hikita's short visits to Montreal in 1979 and the bulk of the work carried out during T. Hikita's one month stay in Montreal in August 1980. The partial financial support provided by NSERC Canada operating grant A-9128 and FCAC Québec Subvention d'équipe Eq-0539 is gratefully acknowledged.

Although the uniformity and the completeness concepts are open to discussion as to their practicality and relation to reality the authors feel that this study is justified as the first step in this direction, and perhaps even more by the richness of the mathematical theory involved. Moreover, the first author thinks that the choice of this topic for an invited talk is only appropriate to express his admiration for the very exciting work done by A. Nozaki and his school in this and other areas of multiple-valued logics and their contributions towards the development of many-valued circuits in the host country of the 13th Symposium.

#### 2. Preliminaries

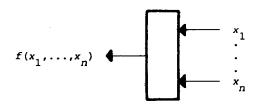

2.1 Switching circuits are built from basic hardware components which we shall henceforth call gates. For simplicity each gate (Fig. 1) is a device with a single output and n inputs (n positive integer). The gate receives and emits signals in the same finite alphabet which will be identified with  $\underline{k} := \{0, \ldots, k-1\}$ . If the signal on the *i*-th input is  $x_i$  (i = 1, ..., n), then the response of the gate is a unique signal completely determined by the *n*-tuple  $(x_1, \ldots, x_n) \in \underline{k}^n$ . Denoting this signal by  $fx_1...x_n$  we can describe the functioning of a gate by an n-ary operation f on  $\underline{k}$  (i.e. a map  $\underline{k}^n \to \underline{k}$ ). For later use  $Q^{(n)}$  stands for the set of all n-ary operations on  $\underline{k}$  and we put  $Q = \sum_{n=1}^{\infty} Q^{(n)}$ . Thus to each gate carries an operation f describing its behavior.

Figure 1.

In reality the physical time dependent signal  $x_1(t)$  on the *i*-th input  $(1 \le i \le n)$  and the output signal  $x_0(t)$  are continuous functions of time. The real situation may be rather complex and so we approximate it by assuming that there are time invariant delays  $\delta_1, \ldots, \delta_n$  such that

$$x_0(t) = f(x_1(t-\delta_1), \dots, x_n(t-\delta_n))$$

(1)

where  $x_i$  (t) (i=0, i..., n) are maps from  $[0, \infty)$  into k and (1) means that the present output depends on the i-th input  $\delta_i$  time units ago (i=1, ..., n). Such gates are called delayed input devices (or d-modules). For simplicity we assume that all  $\delta_i$  belong to the set  $N=\{0,1,\ldots\}$  of nonnegative integers. In this paper we go even further and assume that  $\delta_1=\ldots=\delta_n$ . Such a gate is called a uniformly delayed k-device (or module). It is fully described by the pair  $(f,\delta)\in\mathcal{V}:=\mathcal{Q}\times N$  called a k-valued operation (or function) with delay.

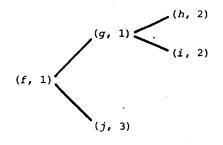

tion of gates by attaching outputs of certain gates to inputs of other gates. Again for simplicity we consider only the combinatorial or feedback free switching circuits. The simplest case is the following. We have a gate F described by  $(f, \delta) \in \mathcal{V}^{(n)} := \mathcal{Q}^{(n)} \times \mathbb{N}$  and n gates G determined  $\binom{m}{i}$  by  $(g_i, \delta_i) \in \mathcal{V}$   $(i = 1, \ldots, n)$ . If we attach the single output of  $G_i$  to the i-th input of F  $(i = 1, \ldots, n)$  the resulting tree-like circuit has  $m := m_1 + \ldots + m_n$  external inputs and realizes the operation  $h := f \otimes (g_1, \ldots, g_n) \in \mathcal{Q}^{(m)}$  defined by

2.2 Switching circuits are obtained from a collec-

$$\begin{array}{l} h(x_{11}, \dots, x_{1m_{1}}, \dots, x_{n1}, \dots, x_{nm_{n}}) \\ = f(g_{1}(x_{11}, \dots, x_{1m_{1}}), \dots, g_{n}(x_{n1}, \dots, x_{nm_{n}})) \end{array}$$

for all  $x_{ij} \in \underline{k}$   $(i=1,\ldots,n,j=1,\ldots,m_i)$ . The delays are  $(\delta+\delta_1,\ldots,\delta+\delta_1,\ldots,\delta+\delta_n,\ldots,\delta+\delta_n)$  and it follows that the circuit will have a uniform delay if and only if  $\delta_1=\ldots=\delta_n$ . Our wish being to stay within uniform delays, we only accept the  $\Theta$ -composition  $(f\otimes (g_1,\ldots,g_n),\delta+\delta')$  with  $(m_i)$   $F:=(f,\delta)\in \underline{\mathcal{V}}^{(n)}$  and  $G_i:=(g_i,\delta')\in \underline{\mathcal{V}}^{(n)}$   $(i=1,\ldots,n)$ . Denote the resulting circuit by  $F\otimes (G_1,\ldots,G_n)$ .

Suppose we have a circuit in the shape of a rooted tree with gates at the vertices distinct from the leaves and external inputs (nor necessarify

Figure 2.

pairwise distinct) at the leaves. Let the sum of the delays be constant on each branch from a leaf to the root. Working from the leaves to the root we can express the delayed function represented by the tree through repeated decomposition (e.g. in the situation of Fig. 2 the function is  $(f \otimes (g \otimes (h, i), j), 4)$ ). Thus the  $\otimes$ -composition suffices for the description of functions associated to combinatorial circuits yielding uniform delays.

It should be stressed that @-composition can be performed iff the inside functions have an identical delay. This restriction differentiates car structure from universal algebras and propositional calculus of most logics in which an unrestricted composition is allowed. However the structure may be described as a suitable partial algebra. As this fact seems to have little impact on completeness, we should not dwell on it.

2.3 In what follows we need the projection (trivial operation)  $e_i^n$ . This is an n-ary operation on  $\underline{k}$  such that  $e_{1}^{n}x_{1}...x_{n} = x_{1}$  for all  $x_{1}, \ldots, x_{n} \in \underline{k}$ . Let  $J := \bigcup_{n} \{e_{\underline{i}}^{n} \mid 1 \le i \le n\}$  denote the set of all projections. For a subset V of V define << V>> as the least subset of V containing  $F \otimes (G_1, \ldots, G_n)$ whenever  $F \in V \cup \langle \langle V \rangle \rangle$  and  $G_i \in \langle \langle V \rangle \rangle \cup (J \times 0)$  (i = 1, ..., n). We have added  $J \times 0$  to allow arbitrary changes of variables (i.e. for  $F \in \langle V \rangle$  the set  $\langle V \rangle$  contains also each F' obtained from F by permuting or identifying (fusing) the variables). Clearly  $V \rightarrow \langle\langle V \rangle\rangle$ is a closure operator on V. The subsets V of Vsatisfying V = <<V>> are called closed uniform classes. A closed uniform class containing  $J \times 0$  is a uniform clone. We say that  $V \subseteq V$  is complete if to every  $f \in Q$  there is  $\delta \in \mathbb{N}$  such that

$(f, \delta) \in \langle v \rangle$ . This was introduced for k = 2 by Kudrjavcev [10, 11] (as completeness in the second sense) and captures the possibility of constructing each operation with some - possibly very large delay. The object of this paper is to give a universal completeness criterion. Before embarking into the technical details a comment on the relation between our model and reality. As pointed out in 2.1 the input delayed gate is already a considerable simplification. For fast circuits the delays should not be ignored (to do so is tantamount to neglect such well-known phenomena like races or hazards) and therefore input delayed devices constitute the first step in the right direction. The restriction to uniformly delayed devices is all pervasive through the literature (with the exceptions [2, 12, 18, 22]) but it is not altogether clear whether it is motivated by mere convenience or rather a hard fact about today's commercially available gates. In practice often several functions gave to be represented simultaneously which could be used as an argument for uniform delays. The completeness concept is open to the obvious criticism: What is the purpose of constructing an F with an enormous delay? We defend our model on the following ground: (1) It

is the simplest possible case, and (2) it makes a nice mathematical theory.

2.4 We conclude this with two minor points. Suppose we have constructed  $(f, \delta)$  and it happens that f is constant (time independent). Of course, there is no observable delay and we can assume that we have all  $(f, \delta')$  with  $\delta' \in \mathbb{N}$ . This is rather academical because usually sources of constant signal are so easy to get and cheap that they can be taken for granted. However it is not accounted for in our model.

Finally, we stress that we are interested in sets of gates with the potential to represent any  $f \in \mathcal{Q}$  (with some delay and assuming an unlimited supply of each type of gates) but ignore completely the optimality: if f can be represented, what is the cheapest way of representing it. This limitation has a good reason because the problem is notoriously hard, depends on the present technology and labor costs and thus, to be meaningful should be closely tailored to a very specific situation which could become obsolete within a very short time.

2.5 We conclude this section with a completeness criterion. First we say that  $P \subseteq Q$  is primal if every  $f \in Q$  is a composition of operations from P (we reserve this term for operations without delays). Put  $e := e_1^1$  (i.e. ex = x for all  $x \in \underline{k}$ ). For  $V \subseteq \underline{V}$  and  $\delta$ ,  $n \ge 0$  put

$$\begin{array}{lll} v^{(n)} & := v \cap v^{(n)}, & v_{\delta} & := \{f \mid (f, \delta) \in v\}, \\ \\ v_{(\delta)} & := \mathop{\cup}_{m=0}^{\infty} v_{m\delta}. \end{array}$$

We have ([11] Thm. 4 for k = 2, [7] and [18] quoted also in [3] Thm. 7.6 p.121 for k > 2):

Proposition 2.6. A closed subset V of U is complete if and only if  $e \in V_{\delta}$  and  $V_{(\delta)}$  is primal for some  $\delta \geq 0$ .

Corollary 2.7. Let V be a closed uniform class. If V is incomplete, then  $F:=(J\times 0)\cup V$  is a uniform incomplete clone.

Needless to say that Proposition 2.6 hardly solves the completeness problem and thus we search for a better criterion. This will be based on sequences of relations introduced and elaborated in the next section.

2.8 A short notational remark. The symbol  $\subset$  stands for strict inclusion, while  $\subseteq$  means inclusion or equality. Whenever possible an n-tuple is written  $x_1 \dots x_n$  instead of the more conventional  $(x_1, \dots, x_n)$ . The same applies to arguments of maps, functions and operations, e.g. we write fx or  $fx_1 \dots x_n$  instead of f(x) or  $f(x_1, \dots, x_n)$ . Sometimes we do not distinguish notationally an element a and the singleton  $\{a\}$  writing e.g.  $A \setminus a$  and  $a \times A$  for  $A \setminus \{a\}$  and  $\{a\} \times A$ .

4

## 3. Polyrelations

3.1 A subset of  $k^h$  is called an h-ary relation on  $\underline{k}$ . An infinite sequence  $\rho = (\rho_0, \rho_1, \ldots)$  of h-ary relations is called an h-ary polyrelation. The set of h-ary polyrelations is denoted  $R_h$  and  $R := \int_{0}^{\infty} R_h$ . For an h-ary relation  $\sigma$  and n positive integer let  $\sigma^{[n]}$  denote the set of  $h \times n$  matrices whose columns are all in  $\sigma$ . For  $f \in Q^{(n)}$  and  $X \in \sigma^{[n]}$  let f[X] stand for the row vector  $(fX_{1\star}, \dots, fX_{h\star})$  where  $X_{i\star}$  denotes the i-th row of X and let  $f[\sigma] := \{f[X] \mid X \in \sigma^{[n]}\}$ . We say that f preserves  $\sigma$  if  $f[\sigma] \subseteq \sigma$  and put  $Pol\sigma := \{f \in Q \mid f$  preserves  $\sigma$ . In universal algebra terms f preserves  $\sigma$  means  $\sigma$  subalgebra of  $\langle k_i, f \rangle^h$ . We say that  $(f,\delta) \in \mathcal{V}$  preserves an h-ary polyrelation  $\rho = (\rho_0, \rho_1, \dots)$  if  $f[\rho_i] \subseteq \rho_{i+\delta}$  for all  $i \geq 0$ . We set

$\begin{array}{ll} \operatorname{Pol}_{\delta} \rho := \{ f \in \mathcal{Q} \ \big| \ f[\rho_{i}] \subseteq \rho_{i+\delta}, \ i=0,1,\dots \} \\ \text{for each } \delta \geq 0, \text{ and} \\ \operatorname{Pold} \rho := \mathop{\delta}^{\infty}_{i=0} \operatorname{Pol}_{\delta} \rho \times \delta. \end{array}$

Example 3.2. Let  $\leq$  be an order (a reflexive, transitive and antisymmetric binary relation). Then  $M:=\operatorname{Pol}\leq$  is the set of  $\leq$ -monotonic operations (i.e.  $f\in\mathcal{Q}^{(n)}$  such that  $fx_1\dots x_n\leq fy_1\dots y_n$  whenever  $x_1\leq y_1,\dots,x_n\leq y_n$ ). Similarly  $f\in\mathcal{Q}^{(n)}$  is  $\leq$ -antimonotonic if  $fx_1\dots x_n\geq fy_1\dots y_n$  whenever  $x_1\leq y_1,\dots,x_n\leq y_n$ . Let A be the set of  $\leq$ -antisymmetric operations and let  $\mu:=(\leq,\geq,\leq,\geq,\ldots)$ . Then  $\operatorname{Pol}_{2i}\mu=M$  and  $\operatorname{Pol}_{2i+1}\mu=A$  for all  $i\geq 0$ .

Lemma 3.3. Let  $\rho=(\rho_0,\rho_1,\ldots)$  be a polyrelation. Then  $\operatorname{Pol}_0\rho=\bigcap_{i\geq 0}\operatorname{Pol}_i$ , and  $\operatorname{Pold}\rho$  is a uniform clone.

We have [5]:

٥

3.4 For an equivalence  $\varepsilon$  on  $\{1, \ldots, h\}$  put  $\Delta_{\varepsilon} := \{a_1 \ldots a_h \in \underline{k}^h \mid \text{ if } i\varepsilon j \text{ then } a_i = a_j\}$  (i.e.  $\Delta_{\varepsilon}$  consists of all h-tuples over  $\underline{k}$  constant on each block of  $\varepsilon$ ). The relations  $\Delta_{\varepsilon}$  are termed diagonal. The diagonal relations and  $\phi$  are called trivial. It is well-known [1, 26-29] that Pol $\sigma = Q$  iff  $\sigma$  is trivial. We say that a polyrelation  $\rho$  is proper if Poldp is incomplete. We characterize improper polyrelations.

Proposition 3.4. A polyrelation  $\rho = (\rho_0, \rho_1, ...)$  is improper if and only if

(i) all  $\rho_i$  are trivial, or

(ii) there are p>0,  $m\in 0$  and the first relations  $\alpha_0,\ldots,\alpha_{p-1}$  such that

$\rho_{i} \subseteq \rho_{i+p} \subseteq \ldots \subseteq \rho_{i+mp} = \rho_{i+(m+1)p} = \ldots = \alpha_{i}$  for all  $i = 0, \ldots, p-1$ .

We say that  $\rho = (\rho_0, \rho_1, ...)$  is periodic, if

there is  $p \ge 0$  such that  $\rho_{i+p} = \rho_i$  for all  $i \ge 0$ . For a periodic  $\rho$  the least  $p \ge 0$  with this property is the *period* of  $\rho$  and denoted  $p_{g}$ .

Corollary 3.5. Let  $\rho$  be a periodic polyrelation with period p. Then  $\rho^t$  is proper if and only if at least one  $\rho$ , is nontrivial.

3.6 For a given polyrelation  $\rho$  put  $[\rho] := \{\tau \in R \mid \text{Pold}\rho \subseteq \text{Pold}\tau\}.$  It would be useful to have a construction  $\psi$  (more precisely a map  $\psi : R_n \to R_h$ ) such that  $\psi(\rho) \in [\rho]$  for all  $\rho \in R_n$ . We give such a map. Let m > 0, n > 0,  $p \ge h > 0$ ,  $A = (a_{ij})$  an  $m \times n$  matrix over  $\{1, \ldots, p\}$  and  $b = (b_1, \ldots, b_m) \in \mathbb{N}^m$ . Given an n-ary polyrelation  $\rho = (\rho_0, \rho_1, \ldots)$  define an n-ary polyrelation  $\tau = \psi_{Abh}(\rho)$  by letting  $\tau_{\ell}$  ( $\ell \ge 0$ ) consist of all  $u_1 \ldots u_h \in \underline{k}^h$  for which there are  $u_{h+1}$ , ...,  $u_p \in \underline{k}$  such that  $u_{h+1} = u_{h+1}$  for all  $u_{h+1} = u_{h+1}$ . We illustrate it on a few examples.

Examples 3.7. (1) Let m=1, n=h=p and s permutation of  $\{1,\ldots,n\}$ . Choosing  $A=[s(1)\ldots s(n)]$  and b=(0) we get  $\tau_{\ell}=\{u_1\ldots u_n\mid u_{s(1)}\ldots u_{s(n)}\in\rho_{\ell}\}.$  (2) Let m=n=h=2, p=3,  $a_{11}=1$ ,  $a_{22}=2$ ,  $a_{12}=a_{21}=3$  and  $b_1=0$ ,  $b_2=1$ . Then, for a binary polyrelation  $\rho$  we get  $\tau=(\rho_0\circ\rho_1,\rho_1\circ\rho_2,\ldots)$  where  $\circ$  denotes the standard relational product.

The definition is justified by:

Lemma 3.8. Let  $\rho$  and  $\tau$  be as in 3.6. Then  $\tau \in [\rho]$  i.e. Pold $\rho \subseteq \text{Pold}\tau$ .

3.9 A uniform incomplete clone is precomplete if every uniform clone properly containing it is already complete (i.e. a maximal element of the poset of incomplete uniform clones ordered by  $\subseteq$ ). A clone  $M \subset Q$  is maximal if  $M \subset M' \subset Q$  for no clone M'.

The maximal clones are completely known [26-28]. They are of the form Polo where the relation  $\sigma$  runs through 6 families. For further use we quote a few of them: (1) proper unary relations (i.e. subsets of  $\underline{k}$  distinct from  $\phi$  and  $\underline{k}$ ), (2) binary relations  $\{as(a) \mid a \in \underline{k}\}$  where s is a permutation with k/p cycles of prime length p, (3) bounded partial orders (transitive, reflexive and symmetric binary relations with a least and greatest element), (4) equivalences, and (5) binary central relations (i.e.  $\sigma$  reflexive, symmetric,  $\neq \underline{k}$  and such that  $\underline{c} \times \underline{k} \subseteq \sigma$  for some  $c \in \underline{k}$ ).

A set  $\Xi$  of proper polyrelations is termed generic if each incomplete uniform clone G extends to Pold $\xi$  for some  $\xi$   $\varepsilon$   $\Xi$ . Our task is to find a small generic set optimally such that each Pold $\xi$  is precomplete. Such a system would provide the best general completeness criterion in the sense that for a given F we have only to test whether  $F \subseteq \operatorname{Pold}\xi$  for all  $\xi$   $\varepsilon$   $\Xi$ . The essential step is Hikita and Nozaki's generic system  $\Xi_0$   $\Xi$ .

For a relation  $\sigma$  put  $\sigma^* := (\sigma, \sigma, \dots)$ . We say that  $\sigma^*$  is of type A if Polo is maximal. Proper periodic polyrelations of arity  $\leq k$  are said to be of type B. For the last type we need the following special binary relations. An equivalence on  $P \subseteq k$  distinct from  $\{aa \mid a \in P\}$  is called a proper partial equivalence on k. A binary polyrelation  $(\rho_0, \rho_1, \rho_2, \rho_2, \rho_3, \rho_4, \rho_5)$  is of type C' if

1)  $\rho_0 = c \times \underline{k}$  for some  $c \in \underline{k}$ , or

2)  $\rho_0$  is a proper partial equivalence, or

3)  $\rho_0 = \{as(a) \mid a \in P\}$  where  $P \subseteq \underline{k}$  and either

i) s is a permutation of P of prime order, or

ii) s is a permutation of  $\underline{k}$ ,  $s \mid P \neq id_{p}$ , and

$s(a) \in P \text{ iff } s(a) = a.$  We have:

Theorem 3.10. [6, 7] The set  $\Xi_0$  is generic. The uniform clones of type A and C' are precomplete.

## 4. Minimal Polyrelations

4.1 It remains to study the set  $\mathcal B$  of polyrelations of type B. Let  $\mathcal D$  denote the set of all polyrelations of type A or C'. A subset  $\Gamma$  of  $\mathcal B$  is B-generic if each  $\beta \in \mathcal B$  is dominated by some  $\xi \in \Gamma \cup \mathcal D$ . In view of Theorem 3.10 it suffices to study B-genericity. Let  $\Xi_1$  consist of all  $\beta \in \mathcal B$  such that  $\{\beta\} \cap \mathcal D = \emptyset$  (where  $\{\beta\}$  is the set of all polyrelations  $\tau$  such that Pold $\beta \subseteq P$  Pold $\tau$ , as defined before). Given  $\rho = (\rho_0, \rho_1, \ldots) \in \mathcal B$  let  $h_\rho$  and  $h_\rho$  (or  $h_\rho$  and  $h_\rho$ ) stand for its arity and period. Let  $h_\rho \in \mathcal B$ . An  $h_\rho$ -ary relation  $h_\rho \in \mathcal B$  (where  $h_\rho := \{a_1 \ldots a_h \in \mathcal B^h \mid a_i = a_j \text{ for some } 1 \le i < j \le h\}$ ). A polyrelation  $h_\rho := \{a_1 \ldots a_h \in \mathcal B^h \mid a_i = a_j \text{ for some } 1 \le i < j \le h\}$ ). A polyrelation  $h_\rho := \{a_1 \ldots a_h \in \mathcal B^h \mid a_i = a_j \text{ for some } 1 \le i < j \le h\}$ ). A polyrelation  $h_\rho := \{a_1 \ldots a_h \in \mathcal B^h \mid a_i = a_j \text{ for some } 1 \le i < j \le h\}$ ). A polyrelation  $h_\rho := \{a_1 \ldots a_h \in \mathcal B^h \mid a_i = a_j \text{ for some } 1 \le i < j \le h\}$ . The next theorem is basic.

Theorem 4.1. If  $\rho \in \Xi_1$  then  $[\rho]$  contains no totally reflexive polyrelation.

A nontrivial relation  $\sigma$  is primitive if it is the union of diagonal relations, and a polyrelation  $\lambda$  is primitive if all  $\lambda_i$  are trivial or primitive, i.e.  $\lambda_i = \Delta_E = \bigcup_{i=1}^{N} \Delta_E$  where  $E = \bigcup_{i=1}^{N} E_h$  ( $i \ge 0$ ), and  $E_h$  is the set of equivalences on  $\{1, \ldots, h\}$ .

Lemma 4.2. If  $\rho \in \Xi_1$ , then  $[\rho]$  contains no primitive periodic polyrelation.

We need the following lemmas. Let  $\mathcal C$  denote the set of constant operations on  $\underline k$ .

Lemma 4.3. Let  $\rho \in \Xi_1$  satisfy (i)  $h_{\rho} > 2$ , (ii)  $[\rho]$  contains no proper binary polyrelation and (iii)  $C \subseteq \text{Pol}_0 \rho$ . Then there is  $0 < i < p_{\rho}$  such that for every  $\theta \in E_{h}$  with exactly two blocks,

(\*) if  $\Delta_{\theta} \stackrel{c}{=} \rho_0$  then  $\Delta_{\theta} \stackrel{c}{=} \rho_i$ .

For integers x and y let x + y denote the inte-

ger z such that  $0 \le z < p$  and  $z \equiv x + y \mod p$ .

Lemma 4.4. Let  $\rho$  satisfy the assumptions of Lemma 4.3 and let  $E\subseteq E_h$  be such that (i) each  $\theta\in E$  has exactly 2 blocks and (ii)  $\cap E$  is the least equivalence. Then  $\Delta_E \not \subseteq \rho_i$  for all  $i\ge 0$ .

4.5 Our goal is to find the smallest possible B-generic system. The strategy is the following: given a B-generic  $\Xi$  we find  $\Xi'\subseteq\Xi$  such that each  $\rho\in\Xi\backslash\Xi'$  is dominated by some  $\rho'\in\Xi'$ . This reduction will be done in several steps. In the first step we reduce the arities. For the ease of presentation  $\rho\in\Xi_1$  is minimal if all proper

$\tau \in [\rho]$  have  $h_{\tau} \ge h_{\rho}$ . Let  $\Xi_2$  be the set of minimal polyrelations. It is almost immediate that  $\Xi_2$  is generic. First we show that  $\Xi_2$  consists of unary and binary polyrelations. In the remainder of the section the polyrelation  $\rho = (\rho_0, \rho_1, \ldots)$  denotes a fixed minimal polyrelation of arity h and period p.

$\sigma_h := \{a_1 \dots a_h \in \underline{k}^h \mid a_i \neq a_j \text{ for } 1 \leq i < j \leq h\},$

$\begin{array}{l} \mathbf{1}_h := \underline{k}^h \backslash \sigma_h, \\ \text{and } \omega_h := \Delta_1 \ldots_h = \{a \ldots_a \in \underline{k}^h \mid a \in \underline{k}\}. \\ \text{We use throughout the notation } \rho_i = \mu_i \cup \nu_i \text{ where} \\ \mu_i = \rho_i \cap \sigma_h \text{ and } \nu_i = \rho_i \cap \mathbf{1}_h \ (i = 0, \ldots, p-1). \ \text{We} \\ \text{start out with the following technical lemmas. For an $h$-ary relation $\sigma$ and $1 \leq i_1 < \ldots < i_k \leq h$ set} \end{array}$

$$pr_{i_1, \dots, i_{\ell}} \sigma = \{ (a_1, \dots, a_{\ell}) \mid \\ a_1 = b_{i_1}, \dots, a_{\ell} = b_{i_{\ell}} \text{ for some } (b_1, \dots, b_h) \in \sigma \}.$$

Lemma 4.6. If  $\theta \in \mathcal{E}_h \setminus \omega_h$ , then every  $v_i \cap \Delta_{\theta}$  is trivial.

An h-ary relation  $\sigma$  is reflexive if  $\sigma$   $\cap$   $\iota_h$  is diagonal or primitive.

Lemma 4.7. If h > 2 then every  $\rho_i$  is empty or reflexive.

Lemma 4.8. If  $\mu_i \neq \phi$ , then  $\operatorname{pr}_{\ell} \rho_i = \underline{k}^{h-1}$  for  $\ell = 1, \ldots, h$ .

Lemma 4.9. No minimal polyrelation has arity greater than 4.

We consider the quaternary minimal polyrelations. Put  $\chi:=\Delta_{12,34}{}^{U}\Delta_{13,24}{}^{U}\Delta_{14,23}$ .

Lemma 4.10. If h=4, then each nonprimitive and nontrivial  $\rho$  contains  $\chi$ .

Proposition 4.11. There is no minimal quaternary polyrelation.

We consider ternary polyrelations.

Lemma 4.12. Let  $\lambda \in \Xi_1$  be ternary and such that  $[\lambda]$  contains no proper binary polyrelation. Then

$\lambda_{i} \cap 1_{3} \in I := \{\phi, \omega_{3}, \Delta_{12}, \Delta_{13}, \Delta_{23}\}$  for all  $i \geq 0$ .