**DE GRUYTER** Juin J. Liou, Shien-Kuei Liaw, Yung-Hui Chung (Eds.) NANO DEVICES AND SENSORS

# Nano Devices and Sensors

Edited by Juin J. Liou, Shien-Kuei Liaw, Yung-Hui Chung

## **Editors**

Prof. Juin J. Liou

University of Central Florida

Dept. Electrical & Computer Engineering

4328 Scorpius Street

Orlando FL 32816, USA

liou@eecs.ucf.edu

Prof. Shien-Kuei Liaw National Taiwan University of Science and Technology Keelung Rd., No. 43, Sec. 4 Taipei 106, Taiwan skliaw@mail.ntust.edu.tw Prof. Yung-Hui Chung National Taiwan University of Science and Technology Keelung Rd., No. 43, Sec. 4 Taipei 106, Taiwan yhchung@mail.ntust.edu.tw

ISBN 978-1-5015-1050-2 e-ISBN (PDF) 978-1-5015-0153-1 e-ISBN (EPUB) 978-1-5015-0155-5 Set-ISBN 978-1-5015-0154-8

## Library of Congress Cataloging-in-Publication Data

A CIP catalog record for this book has been applied for at the Library of Congress.

## Bibliographic information published by the Deutsche Nationalbibliothek

The Deutsche Nationalbibliothek lists this publication in the Deutsche Nationalbibliografie; detailed bibliographic data are available on the Internet at http://dnb.dnb.de.

© 2016 Walter de Gruyter Inc., Boston/Berlin

Cover image: Petrovich9/Signature Collection/istock by Getty Images

Typesetting: Lumina Datamatics

Printing and binding: CPI Books GmbH, Leck

© Printed on acid-free paper

Printed in Germany

www.degruyter.com

Juin J. Liou, Shien-Kuei Liaw, Yung-Hui Chung (Eds.) Nano Devices and Sensors

## Also of interest

The Fundamentals of Electrical Engineering

Felix Hüning, 2014

ISBN 978-3-11-034991-7, e-ISBN 978-3-11-034990-0,

e-ISBN (EPUB) 978-3-11-030840-2

Signals and Systems

Gang Li, Liping Chang, Chen Li

ISBN 978-3-11-037811-5, e-ISBN 978-3-11-037954-9,

e-ISBN (EPUB) 978-3-11-041684-8

Nanophotonics Dennis Couwenberg (Publishing Editor), 1 issue per year ISSN 2192-8614

Opto-Electronics Review

Leszek Jaroszewicz (Editor in Chief), 4 issues per year

ISSN 1896-3757

Energy Harvesting and Systems Shashank Priya, 4 issues per year ISSN 2329-8766

## Editorial/Foreword

The chapters in this edited book are written by some authors who have presented very high quality papers at the 2015 International Symposium of Next-Generation Electronics (ISNE 2015) held in Taipei, Taiwan. The ISNE 2015 was intended to provide a common forum for researchers, scientists, engineers, and practitioners throughout the world to present their latest research findings, ideas, developments, and applications in the general areas of electron devices, integrated circuits, and microelectronic systems and technologies. The scope of the conference includes the following topics:

- A. Green Electronics

- B. Microelectronic Circuits and Systems

- C. Integrated Circuits and Packaging Technologies

- D. Computer and Communication Engineering

- E. Electron Devices

- F. Optoelectronic and Semiconductor Technologies.

The technical program consisted of 4 plenary talks, 23 invited talks, and more than 250 contributed oral and poster presentations. Plenary speakers were recognized experts in their fields, and their talks focused on leading-edge technologies including:

"The Future Lithographic Technology for Semiconductor Fabrication," by Dr. Alek C. Chen, Asia ASML, Taiwan.

"Detection of Single Traps and Characterization of Individual Traps: Beginning of Atomistic Reliability Physics," by Prof. Toshiaki Tsuchiya, Shimane University, Japan.

"The Art and Science of Packaging High-Coupling Photonics Devices and Modules," by Prof. Wood-Hi Cheng, National Chung-Hsing University, Taiwan.

"Prospect and Outlook of Electrostatic Discharge (ESD) Protection in Emerging Technologies," by Prof. Juin J. Liou, University of Central Florida, USA.

After a rigorous review process, the ISNE 2015 technical program committee has selected 10 outstanding presentations and invited the authors to prepare extended chapters for inclusion in this edited book. Of the 10 chapters, five are focused on the subject of electronic devices, and the others cover the circuit designs for various applications. The authors are working at the academia in Austria, United States, Korea, and Taiwan.

The guest editors would like to take this opportunity to express our sincere gratitude to all the members of the ISNE 2015 technical program committees for reviewing the papers and selecting the manuscripts for the edited book. We also thank all the authors for their valuable and excellent contributions to the book.

## **Guest Editors:**

Juin J. Liou University of Central Florida, USA

S. K. Liaw National Taiwan University of Science and Technology, Taiwan

Y. H. Chung National Taiwan University of Science and Technology, Taiwan

## **Contents**

Chunsheng Jiang, Renrong Liang, Jing Wang, and Jun Xu

Subthreshold Behaviors of Nanoscale Silicon and Germanium Junctionless

Cylindrical Surrounding-Gate MOSFETs — 1

Viktor Sverdlov, Dmitri Osintsev, and Siegfried Selberherr

Silicon-on-Insulator for Spintronic Applications: Spin Lifetime and Electric Spin

Manipulation —— 29

Amit Prakash and Hyunsang Hwang

Multilevel Cell Storage and Resistance Variability in Resistive Random Access

Memory —— 49

Yao-Feng Chang, Burt Fowler, Ying-Chen Chen, Fei Zhou, Xiaohan Wu, Yen-Ting Chen, Yanzhen Wang, Fei Xue, and Jack C. Lee Resistive Switching Characteristics and Mechanisms in Silicon Oxide Memory Devices — 73

Yao-Feng Chang, Burt Fowler, Ying-Chen Chen, Fei Zhou, Chih-Hung Pan, Kuan-Chang Chang, Tsung-Ming Tsai, Ting-Chang Chang, Simon M. Sze, and Jack C. Lee

A Synaptic Device Built in One Diode–One Resistor (1D–1R) Architecture with Intrinsic  $SiO_x$ -Based Resistive Switching Memory — 91

Tzung-Je Lee and Yen-Ting Chen

On-chip Wide Range Bidirectional Current Sensor for Li-ion Battery Management

System —— 113

Yung-Hui Chung, Chia-Wei Yen, and Cheng-Hsun Tsai

A 12-bit 1-MS/s 26-µW SAR ADC for Sensor Applications — 135

Chang-Hsi Wu, Hong-Cheng You, and Shun-Zhao Huang

A 5.2/5.8 GHz Dual Band On-Off Keying Transmitter Design for Bio-Signal

Transmission — 159

Shen-Li Chen, Chun-Ju Lin, and Yu-Ting Huang

Impacts of ESD Reliability by Different Layout Engineering in the 0.25-µm 60-V

High-Voltage LDMOS Devices — 177

Billion Abraham, Arif Widodo, and Poki Chen

Impact-Based Area Allocation for Yield Optimization in Integrated Circuits —— 199

Editors - 215

List of authors - 217

Chunsheng Jiang, Renrong Liang, Jing Wang, and Jun Xu

## Subthreshold Behaviors of Nanoscale Silicon and Germanium Junctionless Cylindrical Surrounding-Gate MOSFETs

Abstract: When the traditional planar metal-oxide-semiconductor-field-effect transistors (MOSFETs) encounter insurmountable bottleneck of static power dissipation, junctionless transistor (JLT) becomes a promising candidate for sub-22 nm nanoscale devices due to its simpler fabrication process and better short-channel performances. Subthreshold behaviors dominate the standby power of nanoscale JLTs. In this chapter, a physics-based analytical model of electrostatic potential for both silicon and germanium short-channel junctionless cylindrical surrounding-gate (JLCSG) MOSFETs operated in the subthreshold regime is proposed, in which the full twodimensional (2D) Poisson's equation is solved in the channel region by a method of series expansion. The expression of the proposed electrostatic potential is completely rigorous and explicit. Based on this result, the expressions of threshold voltage, subthreshold drain current, and subthreshold swing for JLCSG MOSFETs are derived. Subthreshold behaviors are studied in detail by changing different device parameters and bias conditions, including doping concentration, channel radius, gate length, gate equivalent oxide layer thickness, drain voltage, and gate voltage. Results predicted by all the analytical models agree well with numerical solutions from the three-dimensional simulator. These analytical models can be used to investigate the operating mechanisms of nanoscale JLCSG MOSFETs and to optimize their device performances.

**Keywords:** Junctionless transistor, analytical model, germanium devices, short-channel effects, subthreshold behaviors, surrounding-gate devices.

## 1 Introduction

Planar metal-oxide-semiconductor-field-effect transistor (MOSFET) has been the work-horse of integrated circuit industry since it was born in 1960 [1]. Performances for planar MOSFETs have been steadily improved due to the scaling down law, which is famous as Moore's law [2]. However, as the gate length of MOSFET scales into sub-22

**Chunsheng Jiang, Renrong Liang, Jing Wang, and Jun Xu,** Tsinghua National Laboratory for Information Science and Technology, Institute of Microelectronics, Tsinghua University, Beijing 100084, China.

nm node, the standby power challenge due to the subthreshold leakage current and the gate tunneling leakage current has become a primary roadblock for low-power applications. The gate tunneling leakage current could be remarkably removed by high-k/metal gate technology [3]. The increase in subthreshold leakage current is mainly caused by the short-channel effects (SCEs), mostly including the threshold voltage roll-off, drain-inducing barrier lowering (DIBL) effect and transverse velocity saturation effect. SCEs result from sharing control over the channel among the source region, drain region, and gate electrode. Multigate transistors, such as double-gate MOSFET, triple-gate MOSFET, Ω-gate MOSFET, ∏-gate MOSFET, and surroundinggate MOSFET, have been proposed to suppress the SCEs by encircling the device channel and the gate controllability could be boosted [4]. Meanwhile, it's another serious challenge for semiconductor manufacture process to produce ultra-sharp source/drain junctions in the range of several nanometers for the nanoscale transistors. Junctionless transistor (JLT) has been proposed to solve this problem [5]. The JLT is basically a gated resistor where the source region, drain region, and channel region have the same dopant type and concentration without any junctions between them.

The advantages of JLTs compared with its inversion-mode MOSFET counterpart are that: (1) it drastically simplifies the fabrication process; (2) it eliminates the lateral impurity diffusion and solves the problem of sharp doping profile formation; (3) it was demonstrated that the short-channel performances, such as DIBL effect and subthreshold slope degradation, were improved when the device sizes were aggressively scaled down [6]; (4) the mobility degradation in the high electric field region is relaxed [7]; (5) the gate dielectric thickness scaling is also relaxed in terms of the intrinsic delay time [5]. Nevertheless, it requires the full depleted channel when JLT works at the off-state in order to turn the device off completely. This is very difficult for the planar structure owing to its weak gate controllability. Thus, multigate structures or three-dimensional (3D) structures can be a good choice to suppress the subthreshold leakage current for JLTs. In practice, almost all of the experimental verifications for JLT concept adopt 3D architectures [8-11]. Another method is replacing the silicon-on-insulator (SOI) substrate with bulk substrate [12]. This method is ideal because the subthreshold leakage current depends on the effective channel layer thickness. In a bulk substrate structure, the effective channel layer thickness can be less than the physical thickness due to the depletion-layer width of p-n junction between the channel and substrate (well) with controllable well doping concentration and/or well bias. Theoretically, the surrounding-gate configuration has the best short-channel performances [13]. As a consequence, junctionless cylindrical surrounding-gate (JLCSG) transistor becomes one of the promising candidates for next-generation digital switch device.

In addition, germanium (Ge) has been considered as one of the promising channel materials in replacement of silicon (Si) for future high-speed CMOS technology because of its high electron mobility (3,900 cm<sup>2</sup>/Vs), hole mobility (1,900 cm<sup>2</sup>/Vs), and best Si compatibility. Ge has been widely investigated in recent years [14-16]. Generally speaking, Ge p-MOSFETs have better performances, whereas Ge n-MOSFETs have exhibited poor drive current and inversion mobility, lower than universal Si mobility, as reported by several different research groups worldwide due to the difficulties in the surface passivation and n-type dopant activation [17-20]. As a result, Ge complementary metal-oxide-semiconductor transistor (CMOS) structure is difficult to be achieved. However, recently, Shoichi Kabuyanagi group [21] demonstrated the high electron mobility in Ge n-channel junctionless FETs compared with Si n-channel MOSFETs. This phenomenon is the resultant effect of the bulk conduction mechanism of junctionless transistors and material properties of Ge. As a result, Ge nchannel JLCSG MOSFET is noteworthy. In this chapter, an analytical short-channel electrostatic model was proposed for Si and Ge JLCSG MOSFETs and their subthreshold behaviors were studied extensively by both proposed analytical model and a 3D commercial numerical simulator [22]. The modeled data are in good agreement with simulated data.

## 2 Silicon junctionless cylindrical surrounding-gate transistors

Si material dominates the present semiconductor manufacturing industry and has best mature fabrication technology because of its good properties and very low cost. Therefore, Si-based JLTs should be studied first. In fact, almost all of the experimental reports on JLTs are based on Si material [23–25].

### The working principle for JLCSG transistor 2.1

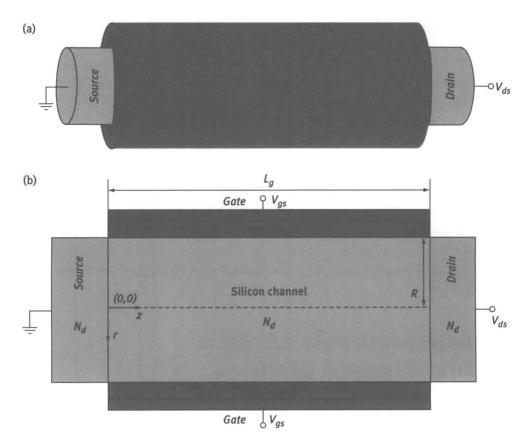

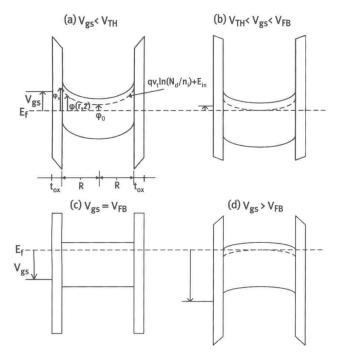

JLT is a kind of intrinsic depletion mode device contrary to the traditional inversionmode MOSFET. Figure 1(a) shows the landscape of an n-type JLCSG MOSFET. Figure 1(b) presents the corresponding cross-sectional schematic diagram along channel direction and coordinates. At zero-gate voltage, a high workfunction (WF) difference between the gate metal and channel material has to be achieved to deplete the entire channel of JLCSG transistors with a suitable threshold voltage value. The operation regimes can be generally classified as full depleted region, partly depleted region, flat-band channel region, and accumulation region [26]. Figure 2 presents the responding energy band diagrams for the four operation regimes.  $V_{th}$  is the longchannel threshold voltage for the n-type JLCSG transistor [27].

Fig. 1: (a) The landscape of an n-type Si JLCSG MOSFET; (b) cross-sectional schematic diagram along channel direction and coordinates of the device.

$$V_{TH} = V_{FB} - \frac{qN_dR^2}{4\varepsilon_{si}} - \frac{qN_dR}{2C_{ox}} \tag{1}$$

and

$$V_{FB} = (\varphi_m - \varkappa - \frac{E_g}{2})/q + \nu_t \ln(\frac{N_d}{n_i})$$

(2)

where  $V_{FB}$  is the flat band voltage; q is the electronic charge;  $N_d$  is the doping concentration of the channel; R is the radius of the channel;  $E_{si}$  is the dielectric constant of Si;  $C_{ox}$  is the capacitance per unit area of the gate dielectric,  $C_{ox} = E_{ox}/[Rln(1 + t_{ox}/R)]$ ;[28]  $E_{ox}$  is the permittivity of the oxide layer;  $t_{ox}$  is the equivalent oxide layer thickness, defined as  $(E_{ox}t_{high-k})/E_{high-k}$ ,  $t_{high-k}$ ,  $E_{high-k}$  are the thickness and permittivity of the high-k gate dielectric materials, respectively [29].  $\varphi_m$  is the workfunction of the gate metal.  $E_{ox}$  is the electron affinity of Si.  $E_{ox}$  is the band gap of Si.  $E_{ox}$  is the intrinsic carrier concentration of Si.  $E_{ox}$  is the thermal voltage, defined as  $E_{ox}$  is the observed

Fig. 2: The energy band diagrams for a n-type JLCSG transistor (a) full depleted region; (b) partly depleted region; (c) flat band region; (d) accumulation region. The potential  $\varphi(r,z)$  is defined as the sum of intrinsic Si midgap level  $(E_{in})$  and  $qv_tln(N_d/n_i)$  referenced to the Fermi level  $(E_f)$ .

from Eqn. (1) that design parameters: R,  $t_{ox}$ ,  $N_d$ , and  $\varphi_m$  must be optimized to achieve better subthreshold performances because the subthreshold leakage current is very sensitive to  $V_{th}$ . Eqn. (1) also indicates the biggest shortcoming of JLTs for digital logic application: the performances depend strongly on the geometry  $(R, t_{ox}, \text{ and } L_g)$  as well as on the doping level of the channel  $(N_d)$  and the process variation is bigger than that of junction-based MOSFETs. However, these parameters can be used to finely tune the operation point of the device, which makes the application of JLTs in low-power sensing systems very promising [30].

It is noteworthy that  $V_{th}$  can be a positive value for the normally off device and be a negative value for the normally on device by adjusting device parameters. Thus, JLTs can satisfy the requirement of multithreshold electronics system easily, which has emerged as a promising technique to reduce leakage power dissipation and boot high performances at the same time [31].

## 2.2 Short-channel effects (SCEs) and subthreshold behavior model

SCEs are very important nonideal secondary effects, mainly including threshold voltage roll-off, DIBL effect, and transverse velocity saturation effect, and so on.

SCEs dominate the subthreshold leakage current, which is the most important component of static power dissipation. For nanoscale JLCSG MOSFETs, analytical models are urgently needed to guide the device design and circuit simulation. However, most studies have concentrated on long-channel models of JLCSG MOSFETs [27, 28, 32, 33], in which the one-dimensional (1D) Poisson's equation is solved based on the gradual channel approximation (GCA). These models are not suitable for short-channel JLCSG MOSFETs, where two-dimensional (2D) effects play a key role. A few studies have been reported that investigate the subthreshold behaviors of JLCSG MOSFETs, in which the quasi 2D Poisson's equation is solved based on the parabolic-profile approximation (PPA) [34-36]. However, PPA is a purely conceptual hypothesis and lacks real physical meaning. For a cylindrical surrounding-gate structure, the conventional separation of variables for series solution to 2D Poisson's equation will introduce a transcendental equation of eigenvalues, which can only be solved numerically [37].

In next sections, a method of series expansion [38, 39] is applied to determine the analytical solutions of the 2D Poisson's equation of JLCSG MOSFETs. This method can avoid the difficulties described above. Thus, the proposed 2D electrostatic potential model is completely rigorous and explicit. Using this model, analytical models for the metrics such as threshold voltage, subthreshold drain current, and subthreshold swing are derived to depict the subthreshold characteristics. The accuracy of all the developed analytical models is verified by numerical simulation using a 3D commercial device simulator.

## An analytical model for Si short-channel junctionless 2.3 cylindrical surrounding-gate MOSFETs

## 2.3.1 Electrostatic potential model

As shown in Figure 1(b), because the doping concentration is very high in the source and drain regions, the voltage drop across these two regions can be ignored. In the subthreshold regime, mobile carriers can be ignored [35]. Furthermore, it is presumed that the channel is fully depleted because of an ultra-small channel radius. For a uniform doped body, Poisson's equation for channel region is

$$\frac{\partial^2 \varphi}{\partial r^2} + \frac{1}{r} \frac{\partial \varphi}{\partial r} + \frac{\partial^2 \varphi}{\partial z^2} = -\frac{qN_d}{\varepsilon_{si}}$$

(3)

where  $-R \le r \le R$  and  $0 \le z \le L_g$ . R is the radius of the channel;  $L_g$  is the gate length.  $\varphi$  is the electrostatic potential.

From refs. [38, 39],  $\varphi$  can be written as

$$\varphi(r,z) = V_{ref} + \frac{V_{ds}}{L_g}z + \sqrt{\frac{2}{L_g}} \sum_{n=1}^{\infty} A_n(r) \sin \frac{n\pi}{L_g}z$$

(4)

where  $V_{ref}$  is the electrostatic potential of the source region relative to the cathode of the power supply.  $V_{ds}$  is the drain voltage. In this work,  $V_{ref}$  is 0.53 V at room temperature.

Substitute Eqn. (4) into (3),  $A_n(r)$  is an auxiliary parameter and satisfies equation:

$$\frac{d^{2}A_{n}(r)}{dr^{2}} + \frac{1}{r}\frac{dA_{n}(r)}{dr} - \lambda_{n}^{2}A_{n}(r) = f_{n}$$

(5)

where

$$\lambda_n = \frac{n\pi}{L_g} \tag{6}$$

and

$$f_n = -\frac{qN_d}{\varepsilon_{si}\lambda_n}\sqrt{\frac{2}{L_g}}[1-(-1)^n]$$

(7)

The general solution of Eqn. (5) is

$$A_n(r) = c_n I_0(\lambda_n r) + d_n K_0(\lambda_n r) - \frac{f_n}{\lambda_n^2}$$

(8)

where  $I_o(x)$  is the zero-order first kind of imaginary Bessel function, and  $K_o(x)$  is the zero-order second kind of imaginary Bessel function. Coefficients,  $c_n$  and  $d_n$  are defined by following boundary conditions:

$$\varphi(r,0) = V_{ref} \tag{9}$$

$$\varphi(r,L) = V_{ds} + V_{ref} \tag{10}$$

$$\frac{\partial \varphi}{\partial r}|_{r=0} = 0 \tag{11}$$

$$C_{ox}[V_{gs} - V_{FB} - \varphi(R, z)] = \varepsilon_{si} \frac{\partial \varphi}{\partial r}|_{r=R}$$

(12)

Eqns. (9) and (10) denote boundary conditions at the source and drain regions, respectively. It is easy to be verified that Eqn. (4) satisfies the boundary conditions of Eqns. (9) and (10) automatically. Eqn. (11) is valid because of the symmetry of the device. Eqn. (12) is derived from Gauss's theorem at the interface of the gate dielectric layer and silicon channel. From Eqns. (8)–(12), we get

$$d_n = 0 (13)$$

$$c_{n} = \left[\frac{f_{n}}{\lambda_{n}^{2}} + \sqrt{\frac{2}{L_{g}}} \frac{L_{g}}{n\pi} (-1)^{n} (V_{ds} + V_{FB} - V_{gs}) - \sqrt{\frac{2}{L_{g}}} \frac{L_{g}}{n\pi} (V_{FB} - V_{gs})\right] / \left[\frac{\varepsilon_{si}}{C_{ox}} \lambda_{n} I_{1}(\lambda_{n}R) + I_{0}(\lambda_{n}R)\right]$$

$$(14)$$

where  $I_1(x)$  is the first-order first kind of imaginary Bessel function. At last, we obtain the expression electrostatic potential:

$$\varphi(r,z) = V_{ref} + \frac{V_{ds}}{L_g} z + \sqrt{\frac{2}{L_g}} \sum_{n=1}^{\infty} \left[ c_n I_0(\lambda_n r) - \frac{f_n}{\lambda_n^2} \right] \sin \frac{n\pi}{L_g} z$$

(15)

where  $c_n$  is given by Eqn. (14). To verify the accuracy of the developed models, the results of analytical models were compared with those of a 3D numerical simulation tool. There are few mobile carriers in the channel when the JLCSG device is operated in the subthreshold regime. Quantum effects can be ignored when  $R \geq 5$  nm in the developed models and simulation [36]. For both analytical calculation and simulation, a dopant-dependence mobility model: Masetti model [40] is used. The device temperature is 300 K, and the workfunction of the gate metal is 4.8 eV.

It should be noted that the Eqn. (15) is an infinite series and we have to used first several terms to approximate  $\varphi(r,z)$ . The convergence of  $A_n$  should be tested firstly. Actually,  $A_n$  converges very quickly with respect to argument n, as presented in Figure 3. It can be observed that high-order terms ( $n \ge 4$ ) are far less than the first three terms. As the gate length increases, the error due to high-order terms increases. This fact indicates that our model is more suitable for short-channel devices  $(10 \text{ nm} \le L_g \le 40 \text{ nm})$ . Even though, the first three order approximations have enough precision to calculate the model expressions for any given gate length and channel radius and the first three order approximations are employed to compute the electrostatic potential, subthreshold drain current and subthreshold swing, only the first order term is considered in the threshold voltage model for simplification.

Figure 4 illustrates the central electrostatic potential along channel direction for different gate lengths. The modeled data match well with simulated data. It can be seen that as the gate length decreases, the position of the minimum central potential is pulled up and leading to a lower threshold voltage. This phenomenon is called the threshold voltage roll-off [41] and deteriorates the device subthreshold performances.