David J. Elliott

# Integrated Circuit Mask Technology

### David J. Elliott

Strategic Planning Manager, Microelectronic Products Shipley Company, Newton, Massachusetts

#### McGraw-Hill Book Company

New York St. Louis San Francisco Auckland Bogotá Hamburg Johannesburg London Madrid Mexico Montreal New Delhi Panama Paris São Paulo Singapore Sydney Tokyo Toronto Library of Congress Cataloging in Publication Data

Elliott, David I.

Intregrated circuit mask technology. Includes index.

1. Integrated circuits—Masks. I. Title. TK7872.M3E44 1985 621.381'73 84-4383 ISBN 0-07-019261-8

Copyright © 1985 by McGraw-Hill, Inc. All rights reserved. Printed in the United States of America. Except as permitted under the United States Copyright Act of 1976, no part of this publication may be reproduced or distributed in any form or by any means, or stored in a data base or retrieval system, without the prior written permission of the publisher.

1234567890 DOC DOC 83210987654

#### 12BN 0-03-0745F7-9

The editors for this book were Roy Mogilanski and Ruth L. Weine, the designer was Elliot Epstein, and the production supervisor was Thomas G. Kowalczyk. It was set in Baskerville by Monotype Composition Company, Inc.

Printed and bound by R. R. Donnelly & Sons, Inc.

## **Preface**

This book details the major fabrication steps and many process techniques used to produce high-resolution masks for integrated-circuit fabrication. Processing parameters for the equipment and chemicals used are presented, giving emphasis to practical details and techniques. Many of the physical parameters, the principles and laws governing the behavior of light and electrons, and the other mask process reactions are explained so as to provide a reference framework for mask makers. The aim of this book is to provide a useful source of practical information on mask-making to facilitate better communication of this subject and to improve the quality of the mask-manufacturing processes.

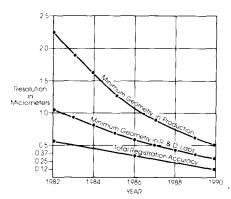

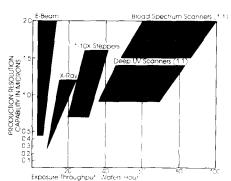

The forces that drive mask technology are reviewed in this book, especially the lithography factors. The charts below summarize both the pattern resolution trends and the lithography technologies used to produce various levels of resolution and wafer throughput.

CHART 1 Integrated circuit feature size and registration control trends (Semiconductor Information Services, Woburn, Mass.)

CHART 2 Wafer exposure system; resolution versus throughput. (Semiconductor Information Services, Woburn, Mass.)

Most experts view lithography as the driving force of both mask and wafer fabrication technology. Special attention has therefore been given in this text to the imaging step in IC fabrication.

## **Acknowledgments**

I would like to acknowledge both Karen Stackpole for her work in preparing the manuscript and the many individuals from our industry worldwide whose technical contributions made the writing of this book possible.

## Contents

|   | Preface                                                                                                                                                                                                                                                                     | xiii |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|   | Acknowledgments                                                                                                                                                                                                                                                             | xv   |

| 1 | PATTERN DESIGN AND DATA PRODUCTION                                                                                                                                                                                                                                          | 1    |

|   | Introduction, 1                                                                                                                                                                                                                                                             |      |

|   | Historical Overview, 2                                                                                                                                                                                                                                                      |      |

|   | Computer-Aided Design Approaches, 6                                                                                                                                                                                                                                         |      |

|   | Design Rules, 7 Impact of Lithography on Design, 9 Pattern Elements and Their Electrical Result, 9 Diffused Regions, 10 Ion-Implant Regions, 10 Polysilicon Regions, 10 Contacts, 11 Metal Layers, 11 Design-Rule Limitations, 12                                           |      |

|   | Pattern Layout, 13  Hand-Drafting, 13  Array Technique, 17  Silicon Compilers, 18  Automatic Placement and Routing, 20  The Routing Step, 20  Hierarchical Design, 20  Symbolic Logic, 23  Fixed-Grid Layout, 24  Building-Block Design and Layout, 26  Device Modeling, 28 |      |

|   | References, 31                                                                                                                                                                                                                                                              |      |

| 2 | MASK-QUALITY GLASS                                                                                                                                                                                                                                                                                                                                                                                                                                        | 33 |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | Introduction, 33                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|   | Glass Melting and Forming, 34  Suitable Optical Transmission, 37  Low Thermal Expansion, 38  Stabilization Time, 40  Material Costs, 40  Low Defect Levels, 42  Cleaning and Handling Resistance, 44  Glass Composition, 45  General Properties of Soda-Lime, Crown Borosilicate, Barium-Aluminum Silicate, and Quartz Glasses, 46  Soda-Lime Glasses, 46  Green Soda-Lime Glass, 46  White Soda-Lime Glass, 47  Borosilicate Glass, 48  Quartz Glass, 49 |    |

|   | Optical Transmission of Glass, 50                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|   | Glass Cleaning, 50 Ultrasonics versus Pinholes, 54 Blank Protection prior to Metallization, 55                                                                                                                                                                                                                                                                                                                                                            |    |

|   | Blank Hardness, 58                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|   | Mask Inspection, 59                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|   | Glass Flatness, 59 Warpage, 63 Plastic Flow, 63 Vacuum-Chuck Distortion, 64 Gravitational Sag, 64 Plate Size versus Thickness, 67 Edge Beveling, 67                                                                                                                                                                                                                                                                                                       |    |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| 3 | COATING FOR MASK BLANKS                                                                                                                                                                                                                                                                                                                                                                                                                                   | 69 |

|   | Introduction, 69                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|   | Mask-Blank Coating Types, 70  Emulsion Mask Characteristics, 70  Advantages of Emulsion Masks, 70  Low Cost, 70  High Photosensitivity, 70  Good Image Resolution and Contrast, 71  Reversal Processing, 71  Enhanced Image-Edge Effects, 73  Weak Points of Emulsions, 74  Diazo Resin Coatings, 75  Resists as Mask Coatings, 76  Iron Oxide Coatings, 77  Chromium, 81                                                                                 |    |

|   | Low-Reflectivity Chromium, 81                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

#### Glass-Blank Cleaning prior to Deposition of the Masking Layer, 83 Glass-Blank Deposition Techniques, 83 Chemical-Vapor Deposition, 84 Vacuum Deposition, 87 Evaporation, 89 Crucible Evaporation, 89 Filament Evaporation, 89 Flash Evaporation, 90 Induction Evaporation, 90 General Vacuum Deposition Criteria, 91 References, 91 4 SUBSTRATE IMAGING 93 Introduction, 93 Imaging, 95 Electron-Beam Imaging, 98 Rapid Turnaround, 100 Optical versus Electron-Beam Processes, 100 Raster versus Vector Scan, 102 Electron-Beam System Capabilities, 104 Throughput, 105 Electron Optics versus Light Optics, 106 Electron Sources, 107 Facilities Requirements, 107 Writing Strategies, 109 Reticles, 114 **MEBES**, 116 Data Format, 116 Vector-Scan Writing in Production, 117 Variable-Shaped-Beam Writing, 122 Contact Printing, 123 Exposure Parameters, 125 Hard- and Soft-Contact Printing, 127 Processing Photoresists and Electron Resists, 128 Exposure Control, 129 Resist Developing, 131 Imaging Sequence for a Positive Optical Resist, 133 Developer Control, 134 COP Negative Electron Resist, 138 PBS Positive Electron Resist, 138 Other Electron Resists, 139 Backscatter in Resist Films, 139 Multilayer Resist Process, 140 AZ-2400 as an Electron Resist, 142 Electron-Beam Resist Troubleshooting, 142

Electron-Beam Resist Selection, 143

#### Pattern Generation, 146

Pattern-Generator Capabilities, 147

Plate Stability, 149

Staging, 149

Control System, 150

Plate Handling, 150

Exposure Energy versus Line Width, 152

Modulation Transfer Function, 153

Depth of Focus, 155

Reflectance versus Resolution, 157

MTF versus Resist and Developer Parameters, 159

Parametric MTF Improvement, 161

Photorepeaters, 161 Reticle Production, 164 Spectral Reflectance, 167 References, 167

#### 5 ETCHING

Introduction, 169

Surfaces to be Etched, 170

Resist Images as Masks, 171

Image Hardening, 173

Post-Bake Parameters, 174

Thermal Flow, 174

Resist Shrinkage, 174

Etch-Resistance Testing, 176

Postexposure Baking, 176

Postdevelopment Exposure, 177

Wet Etching, 178

Chrome Etching, 179

Etch Profiles, 180

Wet Etchants for Chrome, 181

Iron Oxide Etching, 186

Equipment for Wet Etching, 186

Wet versus Dry Etching, 187

#### Dry Etching, 188

Advantages of Dry Etching, 188

Overview, 190

Etch Duration versus Temperature, 191

Etch Rate versus Pressure, 192

Etch Rate versus of Power, 192

Etch Rate versus Oxygen Gas Concentration, 193

RF Power versus Etch Rate for Mixture of CCl<sub>4</sub> and Air, 194

Pattern Width of Master Mask versus Copy Mask, 195

Etch Time versus Line-Width Change, 195

Undercut Profiles, 197

169

|   | Overetching, 200                                                                                                                                                           |     |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   | Reverse Etching, 201                                                                                                                                                       |     |

|   | Resist Removal, 202 Resist-Removal Criteria, 203 Wet-Chemical Resist Removal, 203 Dry-Chemical Resist Removal, 204                                                         |     |

|   | References, 207                                                                                                                                                            |     |

|   |                                                                                                                                                                            |     |

| 6 | PATTERN MEASUREMENT                                                                                                                                                        | 209 |

|   | Introduction, 209                                                                                                                                                          |     |

|   | Optical Microscopy, 212 Image-Shearing Microscopes, 216 Photosensing Devices, 217 TV Scanning Microscopes, 218 Laser Measurement, 219 Scanning-Microscope Measurement, 222 |     |

|   | Thickness Measurement, 231 Interferometry, 231 Stylus Profilometry, 233 Prism-Coupler Measurement, 236 Ellipsometric Measurement, 237 Channel Spectra, 238                 |     |

|   | Applications for Pattern Measurement, 239                                                                                                                                  |     |

|   | References, 241                                                                                                                                                            |     |

|   |                                                                                                                                                                            |     |

| 7 | MASKS IN PRODUCTION                                                                                                                                                        | 243 |

|   | Introduction, 243                                                                                                                                                          |     |

|   | Inspection, 243 Defects, 244 Registration Errors, 245 Critical-Dimension (CD) Checking, 245 Mask-Quality Checks, 246 Overall Inspection Criteria, 246                      |     |

|   | Definitions and Sources of Defects, 247                                                                                                                                    |     |

|   | Mask Quality and Yield, 251                                                                                                                                                |     |

|   | Examples of Mask Defects, 252                                                                                                                                              |     |

|   | Inspection Technique, 255 Optical Comparator Method, 256 Image Enhancement, 257 Adjacent-Die Comparison Method, 258                                                        |     |

|   | Pellicles for IC Mask Protection, 259  Transmission Properties of Pellicles, 262  Midultraviolet Technology and Pellicle Use, 264  Pellicle Particle Protection, 265       |     |

#### Mask Defects and Repair, 268

Defect Removal by Laser, 269

Repair of Transparent Defects, 270

Repair Equipment, 272

Patching Clear Defects, 274

Ink-Dot Repair of Defects, 275

Washing Procedure for Repaired Reticles, 275

#### Mask Cleaning in Production, 276

Forces Affecting Particle Contamination, 276 Cleaning after Deposition, 277 Dry Cleaning of Masks and Reticles, 277 Chemical Cleaning, 278 Cleaning Low-Expansion Glass, 281

References, 281

INDEX 283

此为试读,需要完整PDF请访问: www.ertongbook.com

# Pattern Design and Data Production

#### INTRODUCTION

The use of computers to provide new device designs has become a matter of fact, and recent very large-scale integration (VLSI) integrated-circuit design has leaned heavily on new and more powerful computing capability. Next-generation components will require even more complexity and utilize more computer time. Computer-aided design (CAD) has grown at an incredible rate, reaching into many fields, including architecture, chemical-experiment design, mathematical modeling, aeronautics, organizational studies, and medicine, to name a few.

The use of CAD in VLSI design is now widespread and extensive, and is considered by many experts to be one of the most well-developed applications of CAD. There are several aspects of VLSI CAD, including

- 1. Current VLSI CAD capabilities and trends

- 2. Device modeling

- 3. Logic simulation, device analysis, and time studies

- **4.** Interconnection strategy

- 5. CAD relationship to lithographic processes

- 6. CAD relationship to testing chips and designs

- 7. Future role of CAD in new devices

The level of integration seems to be a common measure of the rise in integrated-circuit (IC) complexity. Early integrated circuits had up to 10 logic gates, and next evolved into medium-scale integration (MSI) integrated circuits that typically had between 10 and 100 logic gates. Beyond MSI came large-scale integration (LSI) with between 100 and 1000 gates. The current VLSI integrated circuits carry over 1000 gates,

and people are already discussing the next layer of integration as being ultralarge-scale integration (ULSI).

#### HISTORICAL OVERVIEW

Integrated-circuit fabrication using photolithography started in the early 1950s with pioneering work at Fairchild Semiconductor and Texas Instruments. The basic steps used to conceive, design, test, fabricate, and chip test are essentially the same ones as were used 30 years ago. The method for handling each step has changed considerably, but basic changes have not been introduced. In summary form, these steps are as follows:

- 1. Define and optimize the IC fabrication and interconnection processes.

- 2. Electrically define circuit elements.

- 3. Design logic schematic.

- 4. Convert logic design to mask patterns (geometries).

- 5. Electrical test simulation of design to detect flaws.

These steps originally involved many hours of engineering time, since all were performed manually. The pattern dimensions were arrived at by evaluating several different geometries and measuring the yield of each test chip. Final pattern geometries were heuristically derived. After building a chip that met initial yield requirements, tests for rejects, electrical properties, and other parameters were run. The final result of this largely trial-and-error approach was a set of specifications for the electrical parameters and design rules (physical parameters) to match. Tolerances for each geometry were specified as they are today, to keep a maximum yield level.

A given customer, in the 1960s, would begin by putting together a drawing of the chip, called a "logic schematic." This sketch would then be built using discrete-component technology, a process called "breadboarding." Assuming all went well after this step, a layout designer would create the mask-pattern dimensions by drawing a set of mask geometries on paper, one for each level of the process. These drawings were then traced onto Rubylith, a red plastic material made by Ulano that served as the photographic master from which optical reductions were made. The Rubylith patterns were inspected for accuracy against the original drawings of the layout designer, a laborious task. Once again, after making any necessary corrections, the Rubylith masters were "shot" with a large reduction camera and reduced over 100 times to make the final emulsion masks. The devices were then built from the

mask sets, and only after chips were complete could manufacturers get an idea of how their products performed.

In the next decade, as device complexity increased, these manual steps became so cumbersome and labor-intensive that shorter, more effective methods had to be devised to preserve overall process economies. The sheer volume of Rubylith sheets needed in a process area was "eating" an inordinate amount of costly facility real estate. The problem was solved by digitally encoding all the IC pattern geometries. The machine that accomplished this task became known as the optical pattern generator. The actual method involved taking the final drawings and converting them into data tapes. This was done by placing an electromechanical digitizer over the drawings and tracing the circuit pattern.

The major advancement made possible by digitizing the art work was computer handling of the IC pattern data. Now the computerized artwork could be run through a design-rule-check (DRC) program to test for open or short circuits or other design flaws. Once a flaw in the IC pattern artwork was detected, it could be easily changed via the digitizing system. In the earlier example, where Rubylith was used, an entirely new piece of artwork would have to be scribed to correct an error.

Once a series of designer drawings had been converted to digital signals that could be manipulated, corrected, and tested, the job of portraying the images on a screen was tackled. The amount of time saved by digitizing artwork was helpful, but many hours still were needed before a given design could be actually tested for defects. A key shortcut was to use the cathode-ray-tube (CRT) screen for laying out all the IC graphics. In the 1970s, interactive graphics, with the use of computers and screens, helped design engineers actually build prototype arrays much faster. For example, a memory section with many identical elements could easily be generated on the interactive graphics systems. This type of equipment would replicate a given common cell many thousands of times on a given device pattern and arrange or configure the pattern, electronically and rapidly. Prior to the advent of interactive graphics, all such configurations would require hand-drawing. All gatearray and memory-array cells had to be placed individually in the IC artwork. The electronic manipulation of interactive graphics saved hundreds of hours of artwork generation time.

By the mid 1970s, several major problems in IC artwork generation had been solved, namely, the digitizing of engineering drawings and the interactive layout process, both allowing for real-time changes and corrections to original design without replotting or recutting artwork. Further time savings were accrued by rapidly placing the thousands of

#### 4 INTEGRATED CIRCUIT MASK TECHNOLOGY

identical pattern elements in an array with the use of interactive graphics terminals. Despite these advancements, all IC geometries for all mask levels needed to be "placed in silicon" before actual testing of the device could occur. The need existed, then, for an IC design simulator. The level of device integration was such that individual ICs could not be tested on the chip, and had to be simulator tested.

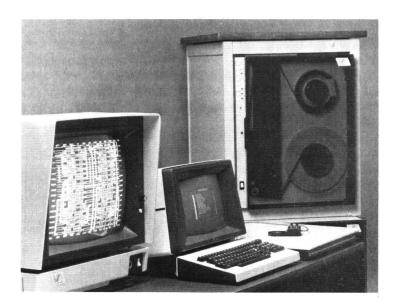

The next innovation was software to simulate the circuit functions. Many different programs were developed to perform IC simulation, resulting in good verification of the layout designers' work. In addition, the interactive graphics equipment could print out a drawing of the final digitized tape after modifications. An important benefit of this software was the ability to automatically verify the match between design layout metallization or interconnections and the balance of the design. An example of an operator working on an interactive CAD system is shown in Fig. 1-1.

In the 1970s, chips could not be modified, as they are today, to correct a defect or modify the result of a design error. This made it especially important to ensure the accuracy of the complete IC design before sending the artwork into manufacturing. However, ensuring accuracy with computer assistance is a far cry from using a computer to generate an entirely new IC design. Several innovations were needed before the automatic IC CAD system could be put into place. These

FIG. 1-1 CAD system with interactive graphics. (VIA Systems, Inc.)

innovations were assisted by the development of standard cell arrays and gate arrays. From this, Stevens and Hashimoto developed a computer algorithm called the "channel router," which was used to design ICs. Further algorithms were developed to provide the metallization or interconnection patterns for a large number of possible circuit designs.

The increased use of automatic-placement computer programs was helped by newer and simpler design styles. The gate arrays, for example, and other designs with standard cells in a regular pattern were more easily designed because of the repeatability of the units. The gate array, or standard slice, shortened the total design time and did not sacrifice precious silicon real estate in the process. Thus, free-form layout began to give way to automatic design and test programs. All new designs, for the first time, had to be testable *before* they were rendered in silicon. Thus, the responsibility for testing was moved from the postfabrication part of the process to the very beginning. Today, untestable designs are not even considered for possible use.

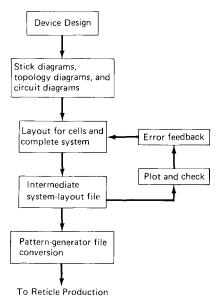

The overall job of producing first a design and second the data from which masks will be made is complex and involves many individual steps. The basic building blocks used to reach the point of reticle production are shown in Fig. 1-2. Automated design has become mandatory because of the rapid increase in device complexity and the

FIG. 1-2 Primary steps in design and data production.

commensurate increase in design time required. A typical 16-bit microprocessor chip requires in excess of 50 worker years of design time alone. The Intel 8086 reportedly required 13 worker years for just the layout phase. An increase in the sophistication of software and hardware has resulted in at least the capability to design even more complex chips than the 32-bit microprocessor. As shown in Fig. 1-3, the design tests are now split into several separate categories, each a separate entity.

#### COMPUTER-AIDED DESIGN APPROACHES

The design of an integrated circuit is a joint task wherein people utilize computers to perform the necessary functions. The trend toward greater interaction between people and computers has been facilitated by additional software for use with interactive graphics systems. Systems are used where a single operator can completely lay out the electronic parameters for a given VLSI design. The more complex systems save

FIG. 1-3 Outline of design tasks. (Diagram by courtesy of T. Sudo.)