# ON-CHIP ESD PROTECTION FOR INTEGRATED CIRCUITS

An IC Design Perspective

### ON-CHIP ESD PROTECTION FOR **INTEGRATED CIRCUITS** An IC Design Perspective

by

Albert Z. H. Wang Illinois Institute of Technology http://www.ece.iit.edu/~awang

KLUWER ACADEMIC PUBLISHERS Boston / Dordrecht / London

Distributors for North, Central and South America:

Kluwer Academic Publishers 101 Philip Drive Assinippi Park Norwell, Massachusetts 02061 USA Telephone (781) 871-6600 Fax (781) 681-9045 E-Mail < kluwer@wkap.com>

#### Distributors for all other countries:

Kluwer Academic Publishers Group

Distribution Centre

Post Office Box 322

3300 AH Dordrecht, THE NETHERLANDS

Telephone 31 78 6392 392

Fax 31 78 6546 474

E-Mail < services@wkap.nl>

Electronic Services < http://www.wkap.nl>

#### Library of Congress Cataloging-in-Publication Data

A C.I.P. Catalogue record for this book is available from the Library of Congress.

Copyright © 2002 by Kluwer Academic Publishers

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher, Kluwer Academic Publishers, 101 Philip Drive, Assinippi Park, Norwell, Massachusetts 02061

Printed on acid-free paper.

Printed in the United States of America

# ON-CHIP ESD PROTECTION FOR INTEGRATED CIRCUITS An IC Design Perspective

## THE KLUWER INTERNATIONAL SERIES IN ENGINEERING AND COMPUTER SCIENCE

#### Acknowledgements

The author wishes to thank all the fellow researchers and IC designers for their shares of contributions to understanding the grand, complex on-chip ESD protection circuit design problem. The book is a selective collection of most of the research advances in the field.

The author acknowledges the sponsorship of a long list of industrial, academic and governmental organizations upon the author's related research activities at the Integrated Electronics Laboratory, Department of Electrical and Computer Engineering, the Illinois Institute of Technology, in various forms.

The author is particularly grateful to his graduate students at the Integrated Electronics Laboratory at IIT for their dedicated and fruitful work on related research topics. Among them are Mr. H. G. Feng for his MS thesis work on mixed-mode ESD simulation-design methodology, Mr. K. Gong for his MS thesis work on ESD-to-circuit interactions and Miss R. Y. Zhan for her PhD dissertation research on ESDcat software development, to name a few. Finally, the author wants to thank Mr. Alexander Greene, Senior Publisher at Kluwer Academic Publishers, for his efforts in producing this book.

#### **Preface**

The author first got in touch with the ESD things in late 1996 when he was a Staff R&D Engineer at the National Semiconductor Corporation, where he was assigned by the boss to develop some on-chip ESD protection circuits for mixed-signal IC chips. Ever since then, the not-so-attractive ESD protection circuit design topics have been on and off the author's table both at the company's cubicle and in the office at the Illinois Institute of Technology, where the author joined its faculty team of Electrical and Computer Engineering in Fall 1998. Exactly like all the other IC designers, the author does not really like the little ESD thing and has no fun in doing ESD protection circuit design. Unfortunately, life is life. One has to deal with some unpleasant issues sometime somewhere somehow. The harsh reality is that an IC designer must find the right ESD protection solution for the IC chips. If there is no ESD protection provided, nobody will buy your chips. If there is no sufficient ESD protection for your chips, you will lose the market to your competitors. Period! What makes an IC designer's life even more miserable is the fact that as IC technologies advance, the customer demands for IC ESD robustness and the complexity of on-chip ESD protection circuit design increase dramatically, as evidenced by the huge amount of related papers published in the past decade. While significant progresses have been made in the field of ESD protection research and design, IC designers are deeply bothered by the situation that there are too much qualitative sayings and too few quantitative analyses on the ESD protection design matters. Hence, very little success in predicting ESD protection circuit design is expected. One question commonly heard in the IC circuit design community is that "how do I design the ESD protection for my chips, with prediction, as a circuit designer?" This book tries to

xvi INTRODUCTION

provide the information necessary to address this tough design challenge from an IC circuit designer's angle.

From IC designers' viewpoint, it is not enough to talk about ESD protection design in the process and device physics language only; and it is unacceptable to continuously rely on the traditional, non-predictive, trialand-error approaches in ESD protection circuit design practices. Since ESD protection phenomena involve complex multiple level process-devicecircuit-electro-thermal coupling effects, the task of ESD protection design is not really about designing a stand-alone ESD protection structure itself. One ought to take into account of the complex interactions between the ESD protection structures and the core circuits being protected in order to successfully achieve full chip level ESD protection. An IC designer ought to be enabled to perform full-scale simulation in order to conduct predictive ESD protection circuit design. With these considerations, the book starts with introduction of ESD protection fundamentals including the ESD origins, ESD test models and standards, etc. It moves on to describe the basic ESD protection devices. ESD protection circuit solutions and advanced ESD protection concepts are then discussed in great details. With these preparations, predictive ESD protection simulation-design methodologies and case studies on the complex ESD-to-circuit interactions are presented. A group of practical ESD protection circuit design examples are provided to enhance the theoretical discussions. Finally, the book concludes with a brief summary on current and future work on ESD protection circuit design. The author wants to point it out clearly to IC designers that, please never try to copy a successful ESD protection circuit, either from this book or anyone else, onto your chips. Most of the time, it will not work for you. It is important to understand that ESD protection circuit design is a custom design and is not portable. It is extremely important to treat ESD protection design as a circuit design task and to conduct ESD design simulation as much as possible. After all, describing a problem quantitatively is more scientific than speaking qualitatively.

An IC designer's best wishes to fellow IC designers: Good Luck!

Albert Z. H. Wang Illinois Institute of Technology Chicago, October 2001.

#### Contents

| Dedication               |                                                                                                |                |

|--------------------------|------------------------------------------------------------------------------------------------|----------------|

| Table of Conte           | nts                                                                                            | vi             |

| Acknowledgem             | pents                                                                                          | xii            |

| Preface                  |                                                                                                | χV             |

| Chapter 1                | INTRODUCTION                                                                                   | 1              |

| 1.1<br>1.2<br>1.3        | A LITTLE HISTORICAL STORY<br>ESD FAILURE – AN IC RELIABILITY PROBLEM<br>ON-CHIP ESD PROTECTION | 1 2            |

| 1.4<br>1.5<br>REFERENCES | - GENERAL REMEDY<br>CHALLENGES IN ESD PROTECTION DESIGN<br>SCOPE OF THIS BOOK                  | 6              |

| Chapter 2                | ESD TEST MODELS                                                                                | 9<br><b>11</b> |

| 2.1<br>2.2               | NATURE OF ESD PHEMONEMA<br>HBM MODEL                                                           | 11<br>14       |

| 2.3<br>2.4               | MM MODEL CDM MODEL                                                                             | 18             |

| 2.5<br>2.6               | TLP MODEL<br>OTHER MODELS                                                                      | 24<br>27       |

| viii           |                                                            | Content. |

|----------------|------------------------------------------------------------|----------|

| 2.7            | ESD ZAPPING TESTS                                          | 30       |

| 2.8            | SUMMARY                                                    | 31       |

| REFERENCES     |                                                            | 33       |

| Chapter 3      | ESD PROTECTION DEVICE SOLUTIONS                            | 35       |

| 3.1            | ON-CHIP ESD PROTECTION MECHANISMS                          | 35       |

| 3.2            | DIODE AS ESD PROTECTION ELEMENT                            | 37       |

| 3.2.1          | Diode Device Physics                                       | 37       |

| 3.2.2          | Diode in ESD Protection Operation                          | 40       |

| 3.2.3          | Diode Parasitic Modelling                                  | 41       |

| 3.3            | BJT AS ESD PROTECTION ELEMENT                              | 42       |

| 3.3.1          | BJT Device Physics                                         | 42       |

| 3.3.2          | BJT in ESD Protection Operation                            | 46       |

| 3.3.3<br>3.4   | BJT Parasitic Modelling                                    | 49       |

|                | MOSFET AS ESD PROTECTION ELEMENT                           | 51       |

| 3.4.1<br>3.4.2 | MOSFET Device Physics ggMOSFET in ESD Protection Operation | 51       |

| 3.4.3          | MOSFET Parasitic Modelling                                 | 54<br>57 |

| 3.4.3          | SCR AS ESD PROTECTION ELEMENT                              | 57<br>59 |

| 3.5.1          | SCR Device Physics                                         | 59<br>59 |

| 3.5.2          | SCR in ESD Protection Operation                            | 64       |

| 3.5.3          | SCR Parasitic Modelling                                    | 67       |

| 3.6            | SUMMARY                                                    | 70       |

| REFERENCES     |                                                            | 71       |

| Chapter 4      | ESD PROTECTION CIRCUIT SOLUTIONS                           | 73       |

| 4.1            | INPUT ESD PROTECTION SCHEMES                               | 73       |

| 4.1.1          | A Primary-Secondary ESD Protection Network                 | 74       |

| 4.1.2          | Multiple-Finger ESD Protection Structure                   | 75       |

| 4.1.3          | Gate-Coupled MOS ESD Protection Structure                  | 77       |

| 4.1.4          | BJT ESD Protection Network                                 | 80       |

| 4.1.5          | SCR ESD Protection Network                                 | 85       |

| 4.2            | OUTPUT ESD PROTECTION SCHEMES                              | 89       |

| 4.2.1          | Dedicated Output ESD Protection Network                    | 90       |

| 4.2.2          | Self-Protection of Output Stages                           | 95       |

| 4.3            | POWER CLAMPS                                               | 95       |

| 4.3.1          | NMOS Power Clamp                                           | 96       |

| 4.3.2          | SCR Power Clamp                                            | 97       |

| 4.3.3          | Diode String Power Clamp                                   | 98       |

| 4.3.4          | Switch as Power Clamp                                      | 102      |

| 4.4            | SUMMARY                                                    | 104      |

ix

| REFERENCES                                                  |                                                                                                                                                                                                                                       | 105                                                  |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Chapter 5                                                   | ADVANCED ESD PROTECTION Mixed-Signal, RF and Whole-Chip ESD Protection                                                                                                                                                                | 107                                                  |

| 5.1<br>5.2<br>5.3                                           | ESD PROTECTION FOR MIXED-SIGNAL ICS<br>ESD PROTECTION FOR RF ICS<br>LOW-PARASITIC MULTIPLE-MODE                                                                                                                                       | 107<br>108                                           |

| 5.3.1<br>5.3.2                                              | SOLUTIONS A Dual-Direction ESD Protection Structure An All-in-One Multiple-Mode ESD Protection                                                                                                                                        | 113<br>115                                           |

| 5.4<br>5.4.1<br>5.4.2<br>5.4.3<br>5.5<br>5.6<br>REFERENCES  | Design WHOLE-CHIP ESD PROTECTION SCHEMES Principles for Full-Chip ESD Protection A Pad + Clamp Scheme A Common ESD Discharge Bus Scheme NON-PORTABILITY IN ESD PROTECTION SUMMARY                                                     | 121<br>126<br>127<br>127<br>129<br>130<br>131        |

| Chapter 6                                                   | ESD FAILURE ANALYSIS AND MODELING                                                                                                                                                                                                     | 135                                                  |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>REFERENCES | WHY ESD FAILURE ANALYSIS? ESD FA TECHNIQUES SOME ESD FAILURE SIGNATURES ESD FA CORRELATION LATENT ESD FAILURE ESD FAILURE MODELING AND CRITERIA SUMMARY                                                                               | 135<br>136<br>138<br>155<br>159<br>162<br>165<br>167 |

| Chapter 7                                                   | LAYOUT AND TECHNOLOGY INFLUENCES<br>ON ESD PROTECTION CIRCUIT DESIGN                                                                                                                                                                  | 171                                                  |

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7               | LAYOUT vs. ESD PROTECTION REGULAR LAYOUT FOR ESD PROTECTION SPECIAL LAYOUT FOR ESD PROTECTION ADVANCED LAYOUT DESIGN CONCEPTS TECHNOLOGY SCALING vs. ESD PROTECTION NEW TECHNOLOGY vs. ESD PROTECTION ESD PROTECTION FOR SOI AND Sige | 171<br>172<br>183<br>193<br>205<br>206<br>210        |

|                                                             |                                                                                                                                                                                                                                       |                                                      |

| X                        |                                                                     | Contents          |

|--------------------------|---------------------------------------------------------------------|-------------------|

| 7.8<br>7.9<br>REFERENCES | ESD PROTECTION FOR NANO TECHNOLOGY SUMMARY                          | 215<br>216<br>217 |

| Chapter 8                | ESD SIMULATION-DESIGN<br>METHODOLOGIES                              | 219               |

| 8.1                      | ESD PROTECTION DESIGN METHODS:                                      |                   |

| 8.2                      | TRIAL-&-ERROR versus PREDICTIVE ESD DESIGN-SIMULATION: DEVICE LEVEL | 219               |

|                          | versus CIRCUIT LEVEL                                                | 221               |

| 8.3                      | ESD PROTECTION DEVICE MODELING                                      | 224               |

| 8.4                      | MIXED-MODE ESD SIMULATION FOR                                       |                   |

| 0.5                      | DESIGN PREDICTION                                                   | 229               |

| 8.5                      | MIXED-MODE ESD SIMULATION:                                          |                   |

| 0.5.1                    | CASE STUDY                                                          | 234               |

| 8.5.1                    | Understanding ESD Simulation Results                                | 235               |

| 8.5.2                    | Case 1: NMOS ESD Protection Structures in                           |                   |

| 0.5.2                    | 0.8μm BiCMOS                                                        | 239               |

| 8.5.3                    | Case 2: MOS ESD Protection Circuit in 0.35μm                        |                   |

| 0 = 1                    | CMOS                                                                | 246               |

| 8.5.4                    | Case 3: Metal Interconnect in ESD Protection                        |                   |

| 8.5.5                    | Design                                                              | 249               |

| 8.3.3                    | Case 4: A Dual-Direction ESD Protection                             |                   |

| 0 6                      | Structure in BiCMOS                                                 | 251               |

| 8.6<br>8.7               | ESD PROTECTION DESIGN VERIFICATION                                  | 255               |

| o. 7<br>REFERENCES       | SUMMARY                                                             | 256               |

| REFERENCES               |                                                                     | 258               |

| Chapter 9                | ESD – CIRCUIT INTERACTIONS                                          | 261               |

| 9.1                      | CHIP-LEVEL ESD PROTECTION DESIGN                                    | 261               |

| 9.2                      | CIRCUIT-TO-ESD INFLUENCES:                                          | 201               |

|                          | PRE-MATURE ESD FAILURES                                             | 262               |

| 9.3                      | ESD-TO-CIRCUIT INFLUENCES:                                          | 202               |

|                          | CIRCUIT PERFORMANCE DEGRADATION                                     | 268               |

| 9.4                      | SUMMARY                                                             | 280               |

| REFERENCES               |                                                                     | 282               |

|                          |                                                                     | 202               |

|                          | CONCLUSION REMARKS AND                                              |                   |

|                          | FUTURE WORK                                                         | 283               |

| Contents     |                                            | xi         |

|--------------|--------------------------------------------|------------|

| 10.1<br>10.2 | CONCLUSION REMARKS<br>FUTURE WORK          | 283<br>285 |

| Appendix A   | SUMMARY FOR ESD TEST STANDARDS             | 287        |

| REFERENCES   | S                                          | 291        |

| Appendix B   | COMMERCIAL ESD TESTING SYSTEMS             | 293        |

| Appendix C   | ESD PROTECTION CIRCUIT DESIGN<br>CHECKLIST | 295        |

| Index        |                                            | 299        |

#### Chapter 1

#### INTRODUCTION

#### 1.1. A LITTLE HISTORICAL STORY

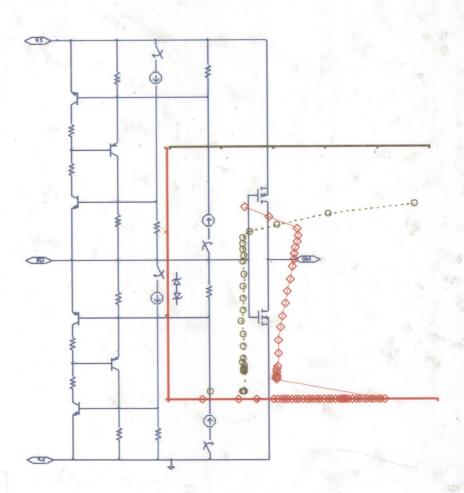

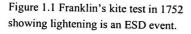

Electrostatics, or, static electricity, is as old as the time itself. Let us take a quick look into the ancient past. In 600 BC, Greeks discovered static electricity in basic experiments, where they rubbed Amber with a piece of fur and observed attraction of lightweight objects to the Amber. That might not be the very first observation of static electricity generation, however, was believed to be the first documented experiment. Interestingly, the English word "electron" derived from the Greek word "electron" for Amber. Serious work on static electricity might have started with the publication of DeMagnete in 1600 by Gilbert, who also made up the word "electricity". Understandings of modern concepts of static electricity were established after a few more centuries of research activities conducted by Gauss, Coulomb, Faraday, etc. Among them, the famous experiments include that performed by Franklin in 1752, as shown in Figure 1.1, when he flew a kite during a storm and observed the Leyden jar placed close to one end of the kite's wire being charged up; and that conducted by Hertz in 1886, as illustrated in Figure 1.2, where he realized wireless communication by using electrostatic discharge (ESD) devices as transceivers. Interested readers can readily find the detailed information by visiting a Science Museum.

Protection against ESD-caused damages also has a long and rich history as that of taking use of electrostatic discharges. As early as in the fifteenth century, European military agencies started to use a variety of means to handle munitions safely. The lightening rod, invented by Franklin soon after his famous kite experiment, which still benefit us all today, was certainly one of the most significant ESD protection devices in the scientific history.

Figure 1.2 Hertz's transmission work in 1886 using ESD spark balls.

Back to today, one could hardly not experience some kind of ESD events in our everyday life. For example, most of us may have experienced the shocking sparks when touching a door handle of a car once and again. One can never image how our everyday life could be without static electricity; meanwhile, one should never overlook the kind of damages caused by ESD as well.

#### 1.2. ESD FAILURE – AN IC RELIABILITY PROBLEM

The ESD problem became a real issue after World War II as highly insulating polymeric materials found widespread usage where substantial static charge accumulation might cause machinery shut downs. However, the devastating ESD damage problem was not taken into serious consideration until the modern microelectronics technologies took the role in our everyday life, which is how ESD failure problem became relevant to semiconductor IC technologies. With the invention of semiconductor transistor in 1947 and development of metal-oxide semiconductor (MOS) technologies in the 1960s, the impact of the invisible ESD phenomena, with a level lower than 1000 volts, became materialized. Some electronic devices can be damaged by an ESD transient of as low as 10 volts. The electronic component and

1. INTRODUCTION 3

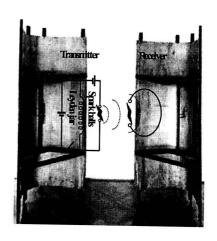

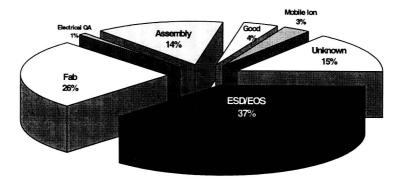

system failures due to ESD events in the electronics industry escalated almost exponentially in the 1970s. Consequently, the military began to develop related standards to govern ESD immunity of electronic products. Particularly, ESD failure is a profound reliability problem to integrated circuits (IC) and poses a grand challenge to the semiconductor industry. This IC ESD failure problem and the ESD protection solution are the topics of this book. As the semiconductor IC technologies advances into the verydeep-sub-micron (VDSM) regime, IC parts become increasingly susceptible to ESD damages. Statistics indicated that up to 30% of all IC failure might be attributed to ESD, as illustrated in Figure 1.3 [1], which costs the semiconductor industry billions of U.S. dollars annually [2]. Such ESDinduced failures are either catastrophic or latent in nature, with the former causes immediate IC malfunction and the latter leads to future failure and lifetime problem. The nature of ESD failures is associated with either high power, i.e., high current, which causes thermal damages to semiconductors and metal interconnect, or, high electric field that ruptures dielectric thin films in ICs. Accordingly, appropriate ESD protection means are developed to protect IC parts against ESD damages.

Figure 1.3 Industrial failure analysis reports substantial IC failure rate due to ESD (data from National Semiconductor Corporation) [1] (Reproduced here by kind permission of the ESD Association and authors).