# MODEL ENGINEERING IN MIXED-SIGNAL CIRCUIT DESIGN

A Guide to Generating Accurate Behavioral Models in VHDL-AMS

## Sorin A. Huss

Kluwer Academic Publishers

1N972

## MODEL ENGINEERING IN MIXED-SIGNAL CIRCUIT DESIGN

## A Guide to Generating Accurate Behavioral Models in VHDL-AMS

by

#### Sorin A. Huss

Darmstadt University of Technology

E200201457

KLUWER ACADEMIC PUBLISHERS

BOSTON / DORDRECHT / LONDON

ISBN 0-7923-7598-X

Published by Kluwer Academic Publishers, P.O. Box 17, 3300 AA Dordrecht, The Netherlands.

Sold and distributed in North, Central and South America by Kluwer Academic Publishers, 101 Philip Drive, Norwell, MA 02061, U.S.A.

In all other countries, sold and distributed by Kluwer Academic Publishers, P.O. Box 322, 3300 AH Dordrecht, The Netherlands.

Printed on acid-free paper

All Rights Reserved

© 2001 Kluwer Academic Publishers, Boston

No part of the material protected by this copyright notice may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system, without written permission from the copyright owner.

Printed in the Netherlands.

#### MODEL ENGINEERING IN MIXED-SIGNAL CIRCUIT DESIGN

## THE KLUWER INTERNATIONAL SERIES IN ENGINEERING AND COMPUTER SCIENCE

#### ANALOG CIRCUITS AND SIGNAL PROCESSING

Consulting Editor: Mohammed Ismail. Ohio State University

#### **Related Titles:**

## CONTINUOUS-TIME SIGMA-DELTA MODULATION FOR A/D CONVERSION IN RADIO RECEIVERS

L. Breems, J.H. Huijsing

ISBN: 0-7923-7492-4

DIRECT DIGITAL SYNTHESIZERS: THEORY, DESIGN AND APPLICATIONS

J. Vankka, K. Halonen

ISBN: 0-7923 7366-9

#### SYSTEMATIC DESIGN FOR OPTIMISATION OF PIPELINED ADCs

J. Goes, J.C. Vital, J. Franca

ISBN: 0-7923-7291-3

#### **OPERATIONAL AMPLIFIERS: Theory and Design**

J. Huijsing

ISBN: 0-7923-7284-0

#### HIGH-PERFORMANCE HARMONIC OSCILLATORS AND BANDGAP REFERENCES

A. van Staveren, C.J.M. Verhoeven, A.H.M. van Roermund

ISBN: 0-7923-7283-2

HIGH SPEED A/D CONVERTERS: Understanding Data Converters Through SPICE

A. Moscovici

ISBN: 0-7923-7276-X

## ANALOG TEST SIGNAL GENERATION USING PERIODIC $\Sigma\Delta$ -ENCODED DATA STREAMS

B. Dufort, G.W. Roberts

ISBN: 0-7923-7211-5

#### HIGH-ACCURACY CMOS SMART TEMPERATURE SENSORS

A. Bakker, J. Huijsing ISBN: 0-7923-7217-4

## DESIGN, SIMULATION AND APPLICATIONS OF INDUCTORS AND TRANSFORMERS FOR SI RF ICs

A.M. Niknejad, R.G. Meyer

ISBN: 0-7923-7986-1

#### SWITCHED-CURRENT SIGNAL PROCESSING AND A/D CONVERSION CIRCUITS:

#### DESIGN AND IMPLEMENTATION

B.E. Jonsson

ISBN: 0-7923-7871-7

## RESEARCH PERSPECTIVES ON DYNAMIC TRANSLINEAR AND LOG-DOMAIN CIRCUITS

W.A. Serdiin, J. Mulder

ISBN: 0-7923-7811-3

#### CMOS DATA CONVERTERS FOR COMMUNICATIONS

M. Gustavsson, J. Wikner, N. Tan

ISBN: 0-7923-7780-X

## DESIGN AND ANALYSIS OF INTEGRATOR-BASED LOG -DOMAIN FILTER CIRCUITS G.W. Roberts, V. W. Leung

ISBN: 0-7923-8699-X

#### VISION CHIPS

A. Moini

ISBN: 0-7923-8664-7

## COMPACT LOW-VOLTAGE AND HIGH-SPEED CMOS, BICMOS AND BIPOLAR OPERATIONAL AMPLIFIERS

K-J. de Langen, J. Huijsing

ISBN: 0-7923-8623-X

#### CONTINUOUS-TIME DELTA-SIGMA MODULATORS FOR HIGH-SPEED A/D

CONVERTERS: Theory, Practice and Fundamental Performance Limits

J.A. Cherry, W. M. Snelgrove

To Monika and to our children Britta, Martin, and Michael. Thank you for your patience!

## Acknowledgments

First of all I would like to thank Dr. Mohammed Ismail, Editor of the Book Series, for his enthusiastic and encouraging support in the conceptual phase of this book. Without his ongoing help this book project would have remained to be just another project. Thanks also to Mark de Jongh of Kluwer Academic Publishers for the pleasant cooperation.

This work is based on research activities in mixed-signal as well as in analog design and modeling performed at my institute over the last decade. I would like to thank my PhD students Wolfgang Boßung, Michael Goedecke, Hatem Hamad, Steffen Klupsch, and Ralf Rosenberger for their significant contributions to this area. Their research results are reflected in this book as well as the implementation work of many undergraduate and graduate students, namely Nadeem Bhatti, Oliver Glier, Karsten Grüner, Tobias Kuckuck, Felix Madlener, Kai Morich, Michael Stini, Wolfram Stumpf and Lars Wehmeyer. Philipp Hahn, Stephan Hermanns, and Stephan Klaus contributed their expertise in generating LaTeX documents, their valuable help in the final phase of this book project is gratefully acknowledged.

All bits and pieces of the considerably large design software suites available at my institute have been kept together by the efforts of Eva Glaser, the system administrator.

Special thanks goes to Elisabeth Hudson. She completed all text processing and figures drawing in an excellent way, a not always easy task. In addition, she morphed my sometimes rather basic English expressions into readable sentences. However, the responsibility for typos, mistakes, and errors remains completely with me.

Commercial trademarks as referred to in this book are assigned to their owners according to my best knowledge. I appologize in advance for any inaccuracy in this matter.

Sorin A. Huss Darmstadt, August 2001

#### **Foreword**

Model engineering is an important activity within the design flow of integrated circuits and signal processing systems. This activity is not new at all in computer engineering, however, and takes a central role in practice. Model engineering of digital systems is based on agreed concepts of abstraction hierarchies for design object representations as well as the expressive power of hardware description languages (HDL). Since their gradual introduction over time HDL have proved to form the foundation of design methodologies and related design flows. Design automation tools for simulation, synthesis, test generation, and, last but not least, for formal proof purposes rely heavily on standardized digital HDL such as Verilog and VHDL.

In contrast to purely digital systems there is an increasing need to design and implement integrated systems which exploit more and more mixed-signal functional blocks such as A/D and D/A converters or phase locked loops. Even purely analog blocks celebrate their resurrection in integrated systems design because of their unique efficiency when is comes to power consumption requirements, for example, or complexity limitations. Examples of such analog signal processing functions are filtering or sensor signal conditioning. In general, analog and mixed-signal processing is indispensable when interfacing the real world (i.e., analog signals) to computers (i.e., digital data processing). Validation of integrated systems, an activity to be executed during the whole design flow, requires a single HDL for model representation in order to handle both partitions of the system model and especially their interaction efficiently.

Therefore, abstract descriptions of analog and mixed-signal systems and components are a new trend in model engineering. Again, modeling of such design objects is not as new as it might seem from the term of 'behavioral' modeling, an almost ubiquitous buzz word nowadays. Structural descriptions from basic components such as transistors and somewhat more abstract representations of analog circuits denoted as macro models have been used in practice for decades by analog circuit designers for analysis purposes exploiting

SPICE-like simulators. The intrinsic behavior of such models is transparent to most design engineers because it is well hidden within predefined component libraries. The availability of HDL for analog and especially for mixed-signal application domains has considerably changed this situation. Now, a modeler is enabled to express directly the behavior of parts of the integrated system without being limited to low-level model primitives such as transistor instances or controlled voltage sources. However, new questions arise, which are quite similar to those in the early days of modeling in the digital domain. These questions address abstraction level hierarchies, modeling concepts and related methods, model calibration and representation (i.e., the whole range of model engineering in mixed-signal systems).

The purpose of this book, therefore, is to combine the main issues of hardware description, characterization methods for the extraction of model parameters, and modeling methodologies for accurate high-level models of mixedsignal components and functional blocks. The work presented here emphasizes — for the first time — an engineering view on model generation and handling, thus providing a unique guide both for practitioners and students of electrical and computer engineering at graduate level. Chapter 1 presents an introduction to the model flow within integrated systems design, to generic model classes as well as to fundamental modeling concepts and representation languages. Chapter 2 is dedicated to the specification of behavior for analog and digital components. Abstraction hierarchies for these components are presented and discussed with respect to mixed-signal applications. Chapter 3 is intended to present a compact introduction to the basic concepts and to the expressivity of the HDL covered by the new IEEE standard 1076.1, also known as VHDL-AMS. Chapter 4 addresses circuit property extraction (i.e., characterization issues of analog building blocks). A new modeling methodology for mixedsignal circuits is proposed in Chapter 5. Finally, Chapter 6 presents results of the outlined model engineering methods for circuit examples of different complexity and operation domains. Several conclusions are summarized at the end of Chapter 6.

## **Contents**

| Li       | st of ]                   | Figures       |                             | iz  |

|----------|---------------------------|---------------|-----------------------------|-----|

| Li       | st of                     | <b>Fables</b> |                             | xii |

| A        | cknov                     | vledgme       | nts                         | XV  |

| Foreword |                           |               | xvi                         |     |

| 1.       | INT                       | RODUC         | CTION                       | 1   |

|          | 1.1                       | Model         | flow in Mixed-Signal Design | 2   |

|          | 1.2                       | Model         | classes                     | 5   |

|          | 1.3                       | Model         | ing languages               | 8   |

| 2.       | SPECIFICATION OF BEHAVIOR |               | 17                          |     |

|          | 2.1                       | Analog        | g Components                | 17  |

|          | 2.2                       | Digital       | Modules                     | 23  |

|          | 2.3                       | Mixed-        | -signal Systems             | 24  |

| 3.       | MODEL REPRESENTATION      |               |                             | 33  |

|          | 3.1                       | Fundar        | mentals of VHDL             | 33  |

|          |                           | 3.1.1         | Behavior                    | 34  |

|          |                           | 3.1.2         | Data flow                   | 35  |

|          |                           | 3.1.3         | Structure                   | 36  |

|          |                           | 3.1.4         | Relations of models         | 36  |

|          | 3.2                       | Introdu       | ection to VHDL-AMS          | 36  |

|          |                           | 3.2.1         | Design objects              | 38  |

|          |                           | 3.2.2         | Extensions to VHDL          | 39  |

|          |                           | 3.2.2.1       | Quantities and Terminals    | 40  |

|          |                           | 3.2.2.2       | Conservation Laws           | 41  |

|          |                           | 3.2.2.3       | Representation of Behavior  | 46  |

|          |                           | 3.2.2.4       | Model Flow Using VHDL-AMS   | 49  |

|          |                           |               | Multi-Nature Systems        | 51  |

|          |                           |               |                             |     |

|    | 3.3   | Mixed-Signal, Multi-Nature Modeling Example        | 54  |

|----|-------|----------------------------------------------------|-----|

|    | 3.3   |                                                    |     |

|    |       | 3.3.1 Partitioning the System                      | 54  |

|    |       | 3.3.2 Models of VDC functional units               | 56  |

|    |       | 3.3.2.1 Testbench                                  | 56  |

|    |       | 3.3.2.2 Environmental Model                        | 57  |

|    |       | 3.3.2.3 Temperature Sensor                         | 58  |

|    |       | 3.3.2.4 Analog/Digital Converter                   | 58  |

|    |       | 3.3.2.5 Digital Block                              | 61  |

|    |       | 3.3.3 Simulation Results                           | 63  |

| 4. | CHA   | ARACTERIZATION OF CIRCUIT PROPERTIES               | 69  |

|    | 4.1   | Role and Principles of Circuit Property Extraction | 69  |

|    | 4.2   | Requirements of Simulation-based Characterization  | 74  |

|    | 4.3   | Visually specified Characterization Plans          | 78  |

|    | 4.4   | Architecture of the ViCE System                    | 83  |

| 5. | ADV   | VANCED MODELING METHODOLOGY                        | 89  |

|    | 5.1   | Motivation                                         | 89  |

|    | 5.2   | Classification of Modeling Approaches              | 90  |

|    | 5.3   | The DEV&DESS Model                                 | 94  |

|    | 5.4   | Basic Methodology and Model Architecture           | 97  |

|    | 5.5   | Model Calibration                                  | 108 |

|    | 5.6   | Case Study: A Linear Dynamic System                | 116 |

| 6. | APP   | LICATION EXAMPLES                                  | 125 |

|    | 6.1   | Overview                                           | 125 |

|    | 6.2   | Active Filter Circuit in Bipolar Technology        | 126 |

|    | 6.3   | A/D Converter in CMOS Technology                   | 137 |

|    | 6.4   | Conclusions                                        | 155 |

| Re | feren | ces                                                | 157 |

## **List of Figures**

| 1.1  | 'Black box' model of a design process               | 2  |

|------|-----------------------------------------------------|----|

| 1.2  | Design flow for systems design                      | 3  |

| 1.3  | Model generation and validation                     | 4  |

| 1.4  | Time- and value-continuous signal waveform          | 6  |

| 1.5  | Event discrete signal waveform                      | 7  |

| 1.6  | Time-discrete signal waveform                       | 8  |

| 1.7  | Causal model                                        | 9  |

| 1.8  | Acausal model                                       | 10 |

| 1.9  | Linear network                                      | 11 |

| 1.10 | Block diagram of the linear network                 | 12 |

| 1.11 | Ideal electrical capacitor models                   | 13 |

| 1.12 | AND gate models                                     | 14 |

| 2.1  | Macro level model of an operational amplifier       | 20 |

| 2.2  | Schematic of a nonlinear CMOS circuit               | 21 |

| 2.3  | Results of transient simulation                     | 22 |

| 2.4  | Specification of component behavior                 | 23 |

| 2.5  | Internal communication within a mixed-signal system | 26 |

| 2.6  | Time scales in mixed-signal systems                 | 26 |

| 2.7  | D/A conversion models                               | 27 |

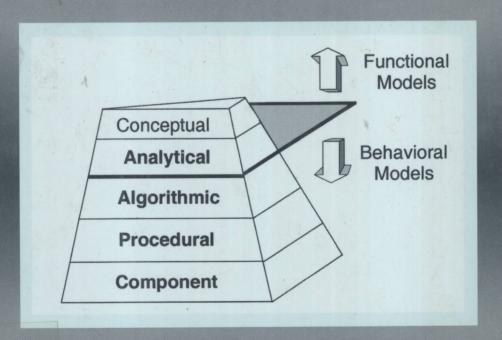

| 2.8  | Abstraction hierarchy for mixed-signal systems      | 29 |

| 2.9  | Interrelationship of model and simulator            | 31 |

| 3.1  | Entity declaration of LFSR                          | 34 |

| 3.2  | Block and black box schematic of LFSR               | 34 |

| 3.3  | Behavioral model of LFSR                            | 35 |

| 3.4  | Data flow model of LFSR                             | 35 |

| 3.5  | Structural model of LFSR                                              | 36 |

|------|-----------------------------------------------------------------------|----|

| 3.6  | Testbench of LFSR                                                     | 37 |

| 3.7  | Combination of signal classes                                         | 39 |

| 3.8  | Connecting functional and behavioral class models                     | 39 |

| 3.9  | Extension to IEEE Standard 1076-1993                                  | 40 |

| 3.10 | Classification of quantities                                          | 41 |

| 3.11 | Simple example for across and through quantities                      | 42 |

| 3.12 | Definition of nature Electrical and some branch quantities            | 42 |

| 3.13 | Nonconservative block                                                 | 43 |

| 3.14 | Mixed causal/acausal block model                                      | 44 |

| 3.15 | Simple analog circuit                                                 | 45 |

| 3.16 | Coding of component behavior model                                    | 46 |

| 3.17 | Code of RC circuit                                                    | 47 |

| 3.18 | Generic model code of a D/A converter                                 | 48 |

| 3.19 | Flow of model instances in systems design                             | 49 |

| 3.20 | Generic harmonic oscillator                                           | 50 |

| 3.21 | Entity declarations for implementation variants                       | 50 |

| 3.22 | Pin compatibility of functional and behavioral models                 | 51 |

| 3.23 | Subset of a multi-nature package                                      | 52 |

| 3.24 | Structural multi-nature model of a diode                              | 53 |

| 3.25 | Multi-nature model of a diode                                         | 53 |

| 3.26 | Composition of the depth gauge                                        | 55 |

| 3.27 | Code of vdc_testbench                                                 | 56 |

| 3.28 | Entity declaration of vdc_sources                                     | 58 |

| 3.29 | Architecture declaration of LakeDive                                  | 59 |

| 3.30 | Equivalent circuit for a temperature sensor                           | 60 |

| 3.31 | Model of temperature sensor                                           | 61 |

| 3.32 | Model of vdc_ADC converter                                            | 62 |

| 3.33 | Entity declaration of vdc_dsp                                         | 63 |

| 3.34 | Architecture declaration of vdc_dsp                                   | 64 |

| 3.35 | Model of aberation monitor vdc_tester                                 | 66 |

| 3.36 | Results of system simulation                                          | 67 |

| 4.1  | Output waveforms of an inverter resulting from fanout load conditions | 71 |

| 4.2  | Role of funcional block characterization                              | 73 |

| 4.3  | Part of a characterization plan coded for SimPilot                    | 76 |

| 4.4  | Characterization on top of procedural simulation                      | 77 |

|      |                                                                       |    |

| X1 |

|----|

|    |

| 4.5  | Extraction of slew rate values coded in CLANG                 | 77   |

|------|---------------------------------------------------------------|------|

| 4.6  | Access windows to the ViCE system                             | 79   |

| 4.7  | Representation of a graph vertex as a glyph                   | 80   |

| 4.8  | Visually represented characterization plan for slew rate      |      |

|      | extraction                                                    | 81   |

| 4.9  | Overview of ViCE                                              | 84   |

| 4.10 | Loop parallelization                                          | 85   |

| 4.11 | Generic communication of scheduler and server pro-            |      |

|      | grams within xpViCE                                           | 86   |

| 4.12 | Outline of graph mapping                                      | 87   |

| 4.13 | User interface of xpViCE                                      | 87   |

| 5.1  | Block schematic of a successive approximation A/D converte    | r 90 |

| 5.2  | Behavioral generic VHDL-AMS model of an A/D converter         | 91   |

| 5.3  | Information flows for model generation                        | 95   |

| 5.4  | DEV&DESS model architecture                                   | 96   |

| 5.5  | Output signal values at discrete points in time               | 98   |

| 5.6  | Response of a dynamic system to an input variable change      | 98   |

| 5.7  | External and internal event queues                            | 99   |

| 5.8  | Generic VHDL-AMS model code for a 1 bit D/A converter         | 100  |

| 5.9  | Simulation of mixed-signal circuits                           | 100  |

| 5.10 | Step response of a dynamic system                             | 103  |

| 5.11 | Integration steps prior to external event processing          | 104  |

| 5.12 | Effect of adjacent events                                     | 105  |

| 5.13 | Generic architecture of a behavioral algorithmic level model  | 107  |

| 5.14 | Model generation methodology                                  | 109  |

| 5.15 | Model calibration by means of the methods library             | 111  |

| 5.16 | Comparison of reference and model behavior by differ-         |      |

|      | ent error norms                                               | 113  |

| 5.17 | Geometrical interpretation of distances                       | 113  |

| 5.18 | Layers of methods library                                     | 115  |

| 5.19 | Pseudo-code of interval segmentation for linear approximation | 115  |

| 5.20 | Linear dynamic system of 2. order                             | 116  |

| 5.21 | DESS model of the linear dynamic system                       | 116  |

| 5.22 | Passive RC circuit                                            | 117  |

| 5.23 | Behavioral model of RC circuit                                | 118  |

| 5.24 | Calibrated parameter function DCtf                            | 119  |

| 5.25 | Calibrated parameter function SlewRate                        | 119  |

| 5.26 | Calibrated parameter function TDly                        | 120      |

|------|-----------------------------------------------------------|----------|

| 5.27 | Functional block model of the linear dynamic system       | 122      |

| 5.28 | Simulation results gained from executing the functional   |          |

|      | block model                                               | 123      |

| 6.1  | Schematic of a biquad filter                              | 127      |

| 6.2  | Schematic of the operational amplifier MOPA1              | 127      |

| 6.3  | Testbench adapter tool                                    | 129      |

| 6.4  | Subset of a visually specified characterization plan      | 130      |

| 6.5  | Calibration of the DC transfer function                   | 131      |

| 6.6  | Calibration of slewing behavior                           | 132      |

| 6.7  | Comparison of dynamic behavior of opamp models            | 133      |

| 6.8  | Output resistance as a function of the load condition     | 134      |

| 6.9  | Comparison of the DC behavior of models at identical      |          |

|      | output load conditions                                    | 135      |

| 6.10 | Comparison of the time domain response of different       |          |

|      | filter models                                             | 136      |

| 6.11 | Context and generic architecture of the A/D converter     | 138      |

| 6.12 | Conversion algorithm of a stage                           | 139      |

| 6.13 | Circuit schematic of a converter stage                    | 140      |

| 6.14 | DC transfer curve of the converter stage                  | 141      |

| 6.15 | Partitioned converter stage                               | 141      |

| 6.16 | DC transfer curves of the ConvSubStage block              | 142      |

| 6.17 | Comparison of the time domain responses of different      |          |

|      | subblock models                                           | 143      |

| 6.18 | Comparison of time domain respones of different con-      |          |

|      | vertrer stage models                                      | 144      |

| 6.19 | Simulation results for mixed-level model of the A/D conve | rter 145 |

| 6.20 | Calibrated generic model of the A/D converter             | 146      |

| 6.21 | Comparison of switching time points for the LSB of        |          |

|      | the A/D converter                                         | 147      |

| 6.22 | Top level model of the A/D converter                      | 149      |

| 6.23 | Model of the converter stage                              | 150      |

| 6.24 | Behavioral model of ConvSubStage                          | 151      |

## **List of Tables**

| 2.1 | Abstraction merarchy for analog components and blocks       | 18  |

|-----|-------------------------------------------------------------|-----|

| 2.2 | Abstraction hierarchy for digital modules and systems       | 25  |

| 2.3 | Different implementation styles of a filter block           | 29  |

| 3.1 | Values of mode subject to PortAttribute                     | 43  |

| 4.1 | Coverage of requirements of characterization plans          | 78  |

| 4.2 | Available control operators                                 | 82  |

| 5.1 | Classes of modeling approaches                              | 92  |

| 5.2 | Fundamental parameter functions of block models             | 107 |

| 6.1 | Testbenches for opamp property extraction                   | 128 |

| 6.2 | Segments and calibrated regression of the method DCtf       | 131 |

| 6.3 | Comparison of requirements in terms of simulation resources | 137 |

| 6.4 | Comparison of simulation times for different models of      |     |

|     | the A/D converter.                                          | 144 |

|     |                                                             |     |

## Chapter 1

#### INTRODUCTION

Analog and mixed-signal integrated circuits (IC) design represents a major challenge for the design of complex information processing systems, especially when it comes to efficient top-down design flows. The generic architecture of mixed analog-digital systems being integrated into one IC, which is known as the System-on-a-Chip (SoC) style, consists of DSP cores and microcontrollers surrounded by A/D and D/A converters, which interface the internal bulk of digital processing to the analog sources and sinks of external information. In the signal processing and integrated circuits community it is widely agreed upon that analog and mixed-signal design expertise will increasingly be exploited for an implementation of powerful and at the same time costeffective products in the areas of communication, consumer and automotive applications. When it comes to discussions on appropriate design flows for such products then two major problem regions may be identified. First, the design tools applied for design tasks in the analog and in the digital domain have to "talk to each other". An explicit need for such a tool communication is present especially in converter design. Secondly, top-down design — a proven adequate design methodology at least for digital systems — has to be adopted to the mixed-signal domain. However, good model-building concepts and efficient tools are essential for a painless transfer of abstract top-down methodologies to engineering practice. In addition, appropriate calibration methods are a precondition to ensure that high-level behavioral models do not diverge from lower-level, detailed models. In this chapter, therefore, we first will be discussing some basic issues related to model flows, modeling concepts, and model representation languages, which are the main means to making models executable (i.e., to get them to work).