# **Integrated Circuit Engineering Establishing a Foundation**

## L. J. Herbst

Division of Electronic and Computer Engineering University of Teesside Middlesbrough

OXFORD NEW YORK TORONTO OXFORD UNIVERSITY PRESS 1996 Oxford University Press, Walton Street, Oxford OX2 6DP

Oxford New York

Athens Auckland Bangkok Bombay

Calcutta Cape Town Dar es Salaam Delhi

Florence Hong Kong Istanbul Karachi

Kuala Lumpur Madras Madrid Melbourne

Mexico City Nairobi Paris Singapore

Taipei Tokyo Toronto

and associated companies in

Berlin Ibadan

Oxford is a trade mark of Oxford University Press

Published in the United States by Oxford University Press Inc., New York

© L. J. Herbst. 1996

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, without the prior permission in writing of Oxford University Press. Within the UK, exceptions are allowed in respect of any fair dealing for the purpose of research or private study, or criticism or review, as permitted under the Copyright, Designs and Patents Act, 1988, or in the case of reprographic reproduction in accordance with the terms of licences issued by the Copyright Licensing Agency. Enquiries concerning reproduction outside those terms and in other countries should be sent to the Rights Department, Oxford University Press, at the address above.

This book is sold subject to the condition that it shall not, by way of trade or otherwise, be lent, re-sold, hired out, or otherwise circulated without the publisher's prior consent in any form of binding or cover other than that in which it is published and without a similar condition including this condition being imposed on the subsequent purchaser.

A catalogue record for this book is available from the British Library

Library of Congress Cataloging in Publication Data Data applied for

> ISBN 0-19-856279-9 (Hbk.) ISBN 0-19-856278-0 (Pbk.)

Printed and bound in Great Britain by The Bath Press, Somerset

Integrabe carcuits

Textbooks in Electrical and Electronic Engineering

#### **Series Editors**

#### G. Lancaster E. W. Williams

- **1.** Introduction to fields and circuits GORDON LANCASTER

- **2.** The CD-ROM and optical disc recording systems E. W. WILLIAMS

- **3.** Engineering electromagnetism: physical processes and computation P. HAMMOND and J. K. SYKULSKI

- **4.** Integrated circuit engineering: establishing a foundation L. J. HERBST

## To my wife

## Preface

Integrated circuits (ICs) occupy a key role in electronics and are to be found in almost every conceivable product of consumer, industrial, and military electronics. They are routinely included in the curriculum of first degrees in electrical/electronic engineering. Many other first degrees in related disciplines like microelectronics and computer engineering also contain substantial material on ICs. The evolution of very-large-scale integration (VLSI) has radically altered the nature of IC engineering. The electronic circuits of a complex system like a computer can now be contained in one or a small number of chips. The nature of VLSI is being brought home to engineers in the form of application-specific ICs (ASICs), which involve customers in their design.

Based on my personal experience of teaching ICs and VLSI on first degrees and on special courses (which I organized) in industry, I perceived the need for a comprehensive text on IC engineering which recognizes the centrality of VLSI, but also embraces lower levels of integration. There is at present a serious gap in such literature. Nothing has been published since 1977 to compare with the comprehensive texts on IC engineering by Hamilton and Howard (1975) and Glaser and Subak-Sharpe (1977). The many books on ICs which have appeared during the last twenty years are generally pitched at a graduate rather than an undergraduate level and tend to be specialized, covering subjects like MOS ICs, VLSI, and IC technology.

This book gives a broad, comprehensive coverage of ICs, embracing fabrication, circuit techniques, and VLSI/ASIC system aspects. Technology is likewise covered in breadth by including bipolar, MOS, and GaAs ICs. It is assumed that readers will have a background in basic transistor operation, analogue and digital circuit practice, and digital design. Alternatively undergraduates may be taught these subjects in parallel with the contents of this book, which is aimed at the second and third years of a British, and the second, third and fourth years of an American degree. The text also meets a vital need for continuing education. Much of the subject matter it contains will probably be new to most engineers and scientists who have graduated some years ago. For that reason this book should prove to be very attractive for career–long learning.

Coming to the details of the contents, the text begins with a general survey (Chapter 1). Device fabrication and packaging (Chapter 2) come next. Chapter 3 covers the formation of transistors, resistors and capacitors, and Chapter 4 outlines device behaviour and modelling. Circuit techniques form the subjects of Chapter 5 (digital) and Chapter 6 (analogue). The last few years have seen a distinct swing towards more analogue and mixed-mode (analogue and digital) ICs, brought about largely by the growth in telecommunications. That situation is reflected

in the contents of Chapter 6, the largest chapter in the book, and the inclusion of mixed-mode ASICs in Chapter 10. Chapter 7 on semiconductor memories initiates the VLSI/ASIC sector, which extends to the end of the book. An overview of ASIC design styles in Chapter 8 paves the way for a fuller treatment of ASICs in Chapters 9 to 11. Chapter 9 describes programmable logic devices (PLDs) with a strong emphasis on field programmable gate arrays (FPGAs). Chapter 10 deals with the characteristics and design issues of ASICs, including economics and design for testability, and Chapter 11 covers ASIC design techniques. Finally Chapter 12 looks at submicron scaling and projections of ICs for the immediate future. Electronics abounds with acronyms and jargon, which are defined in a glossary at the end of the text for ease of reference.

The style of presentation departs in a number of ways from the orthodoxy found in the majority of books on ICs. My first and foremost consideration has been to highlight the engineering dimension. Many publications within the last two decades on the teaching of engineering have urged the need for more material on engineering practice and design, and less on analysis (ASEE 1987; Finniston 1980). Inspite of this there is a continuing trend towards a concentration on analysis.

The roles of analysis and synthesis in this book embody some ideas which I advanced at two conferences in the US (Herbst 1987 and 1989). Analysis has been greatly reduced relative to the traditional presentation in many established texts on ICs. Second synthesis has been carefully structured to illustrate current engineering practice. Last synthesis is often placed before analysis, frequently in the form of an overview at the beginning of a chapter. My approach bears some resemblance to the inverted curriculum proposed by Cohen (1987 and 1992). Extensive quotations of IC specifications and performance bring home the capabilities of current ICs, and this information is continually interwoven with the rest of the text, sometimes even within the analytical sections. The profuse quotations of current IC performance are open to the charge that such material will soon become dated. There is a characteristic American saying that if a piece of equipment works it is out of date. However the probable changes in the performance of future ICs, mainly due to continuing miniaturization, are dealt with, and readers should be able to appreciate the capabilities of new products emerging within the next few years without undue difficulty (Mead and Conway 1980).

The accent on engineering design and applications in this text is long overdue. Much of the engineering science and mathematics of an engineering undergraduate curriculum is unnecessary and can be eliminated, making way for material on synthesis, design and applications (Finniston 1980, pp.94–5). Nevertheless a balance must be maintained between analysis and synthesis: the danger of overemphasizing the engineering aspects to the detriment of fundamental concepts is very real.

Muller and Kamins (1986) hold successful engineering to rest on two foundations, physical concepts and technology. Zorpette (1984) warns against excessive emphasis on what he calls the technology of the moment. Everitt (1980) defined the fundamental difference between science and engineering to be the difference between analysis and synthesis, and went on to say that synthesis can only be accomplished after a thorough grounding in analysis. G.M. Trevelyan (1946), the late great English his-

It remains for me to express my gratitude for the help I have received from various sources. Apart from obtaining databooks from semiconductor vendors, I had countless conversations with staff from these establishments to clear up matters on which I felt uncertain, or to obtain additional information. This help was given most willingly without exception and has been of tremendous value. The manuscript has been produced and typeset with the aid of computer typesetting software by Trevor and Rose Atkinson, who have very effectively accommodated special requirements regarding style and have been most helpful throughout. I am indebted to Colin Gregg, who has drawn all the diagrams with the aid of computer graphics, and has in many cases improved on the originals submitted to him. The help and cooperation of the publishers at all stages of the production is gratefully acknowledged.

Last and most I am indebted to my wife for her unstinting support for this undertaking, which made a severe inroad on the time for normal domesticity. It is only her encouragement and understanding which have made this book possible.

Middlesbrough September 1995 L.J.H.

#### References

- ASEE. (1987). A national action agenda for engineering education. A report of the task force on the national agenda for engineering education. American Society for Engineering Education (ASEE), USA.

- Cohen, B. (1987). The education of the information systems engineer. Electronics and Power, 33, pp.203–5.

- Cohen, B. (1992). The inverted curriculum. National Economic Development Office, England.

- Everitt, W.L. (1980). The phoenix-a challenge to engineering education. Reprinted from the Proceedings of the IRE, 32, September 1944, 509–13. *IEEE Transactions on Education*, 23, pp.179–83.

- Finniston, M. (1980). Engineering our future. Report of the committee of enquiry into the engineering profession. Her Majesty's Stationery Office, England.

- Glaser, A.B. and Subak-Sharpe, G.E. (1977). Integrated circuit engineering. Addison-Wesley, USA.

- Hamilton, D.J. and Howard, W.D. (1975). Basic integrated circuit engineering. McGraw-Hill, USA.

- Herbst, L.J. (1987). Analysis and synthesis in honours engineering degrees. Proceedings of the 1987 Frontiers in Education Conference, IEEE and ASEE, Terre Haute, Ind., USA.

- Herbst, L.J. (1989). Placing synthesis before analysis. Proceedings of the 1989 Frontiers in Education Conference, IEEE and ASEE, Bingham, N.Y., USA.

- Mead, C. and Conway, L. (1980). Introduction to VLSI systems, p.vi. Addison-Wesley, USA.

- Muller, S. and Kamins, T.I. (1986). Device electronics for integrated circuits, (2nd edn), p.57. Wiley, USA.

- Trevelyan, G.M. (1946). English social history, (3rd edn), p.viii. Longmans, England.

- Zorpette, G. (1984). EE programs. IEEE Spectrum, 21, (11), 44-50.

# Acknowledgements

The following industrial establishments have kindly given permission to quote from their databooks and/or datasheets.

Actel

Altera

Advanced Micro Devices (AMD)

**Analog Devices**

ASM Lithography

Austria Mikro Systeme International (AMS)

Burr Brown

Cadence

Compass

Cypress Semiconductor

**Fujitsu**

GEC Plessey Semiconductors (GPS)

Harris Semiconductor

Lattice Semiconductor

Mentor Graphics

Micro Linear

Motorola

National Semiconductor (NS)

NEC

Philips Semiconductors

Synopsys

Technology Modeling Associates (TMA)

Texas Instruments (TI)

VLSI Technology

Xilinx

Great care has been taken to give due acknowledgement for the use of data, whether in tabulations or in the text. Trademarks have also been listed, especially in the Glossary. Alternatively the introduction of an acronym has been directly linked with its originator, thereby establishing its proprietary nature. The author apologizes if inadvertently the proper acknowledgement has not been made, or if a trademark has been omitted. Such cases and errors in the data should be brought to the notice of the publishers, so that they can be put right in a reprint. The same observation applies to permissions for using information from textbooks.

Philips Semiconductors have requested the insertion of the following disclaimer:

#### xii Acknowledgements

Philips Semiconductors and North American Philips Corporation Products are not designed for use in life support appliances, devices or systems where a malfunction of a Philips Semiconductor and North American Philips Corporation Product can reasonably be expected to result in a personal injury. Philips Semiconductors and North American Phillips Corporation customers using or selling Phillips Semiconductors and North American Phillips Corporation Products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors and North American Philips Corporation for any damages resulting from such improper use or sale.

On a more general note, the author advises that the quotations of data from the establishments listed are only guidelines, but that fuller information, sometimes going beyond what is available in databooks and datasheets, should be consulted for actual designs.

# Contents

| 1 | Overview            |                                                                                              |          |

|---|---------------------|----------------------------------------------------------------------------------------------|----------|

|   | 1.1                 | IC structure                                                                                 | 1        |

|   | 1.2                 | Historical perspective                                                                       | 4        |

|   | 1.3                 | IC spectrum                                                                                  | 8        |

|   |                     | 1.3.1 VLSI                                                                                   | 8        |

|   |                     | 1.3.2 SSI and MSI                                                                            | 9        |

|   |                     | 1.3.3 PLDs                                                                                   | 10       |

|   |                     | 1.3.4 Analogue ICs                                                                           | 10       |

|   |                     | 1.3.5 ASICs                                                                                  | 11       |

|   |                     | 1.3.6 Summary                                                                                | 12       |

|   |                     | References                                                                                   | 13       |

| 2 | Fab                 | rication and packaging                                                                       | 15       |

|   | 2.1                 | Processing outline                                                                           | 15       |

|   | 2.2                 | Processing sequence for transistors                                                          | 18       |

|   | 2.3                 | Wafer preparation                                                                            | 22       |

|   | 2.4                 | Deposition and growth                                                                        | 25       |

|   |                     | 2.4.1 Oxidation                                                                              | 25       |

|   |                     | 2.4.2 Epitaxy                                                                                | 30       |

|   |                     | 2.4.3 Diffusion                                                                              | 31       |

|   |                     | 2.4.4 Ion implantation                                                                       | 34       |

|   |                     | 2.4.5 Dielectric and polysilicon films                                                       | 39       |

|   |                     | 2.4.6 Interconnects                                                                          | 40       |

|   | 2.5                 | 0 1 0                                                                                        | 44       |

|   |                     | 2.5.1 Introduction                                                                           | 44       |

|   |                     | 2.5.2 Lithographic technology                                                                | 44       |

|   |                     | 2.5.3 Resists                                                                                | 50       |

|   | 0.0                 | 2.5.4 Etching                                                                                | 52       |

|   | 2.6                 |                                                                                              | 56       |

|   |                     | 2.6.1 Introduction                                                                           | 56<br>57 |

|   |                     | <ul><li>2.6.2 Packages available</li><li>2.6.3 Packaging and mounting technologies</li></ul> | 57<br>59 |

|   |                     | 2.6.4 Package selection                                                                      | 63       |

|   |                     | 2.6.5 Multichip modules                                                                      | 65       |

|   | 2.7                 | Overview                                                                                     | 67       |

|   |                     | References                                                                                   | 69       |

| 3 | Component formation |                                                                                              | 73       |

|   | 3.1                 | Introduction                                                                                 | 73       |

|   | 3.2                 | CMOS                                                                                         | 73       |

|   | 3.3                 | Silicon bipolar transistors                                                                  | 78       |

|   |                     |                                                                                              |          |

|   | 3.4 | BiCMOS                                        | 81                |

|---|-----|-----------------------------------------------|-------------------|

|   | 3.5 | GaAs transistors                              | 82                |

|   | 3.6 | Resistors and capacitors                      | 84                |

|   | 3.7 | Design rules and device areas                 | 87                |

|   |     | References                                    | 91                |

| 4 | De  | vice behaviour and modelling                  | 93                |

|   | 4.1 | Introduction                                  | 93                |

|   | 4.2 | Transient response and bandwidth              | 93                |

|   | 4.3 | MOSFET characteristics                        | 96                |

|   |     | 4.3.1 DC characteristics                      | 96                |

|   |     | 4.3.2 Capacitances                            | 100               |

|   |     | 4.3.3 Channel transit time                    | 103               |

|   |     | 4.3.4 Hot carriers                            | 103               |

|   |     | GaAs MESFET characteristics                   | 103               |

|   | 4.5 |                                               | 105               |

|   | 4.6 | The role of SPICE                             | 109               |

|   | 4.7 |                                               | 111               |

|   |     | 4.7.1 Introduction                            | 111               |

|   |     | 4.7.2 MOSFET models                           | 111               |

|   |     | 4.7.3 GaAs MESFET model                       | 112               |

|   |     | 4.7.4 BJT model<br>4.7.5 Junction diode       | 112               |

|   |     | References                                    | 112               |

|   |     |                                               | 113               |

|   |     | Further reading                               | 114               |

| 5 |     | ital circuits — techniques and performance    | 117               |

|   | 5.1 | Introduction                                  | 117               |

|   | 5.2 | Logic Circuits                                | 117               |

|   |     | 5.2.1 Design criteria                         | 117               |

|   |     | 5.2.2 Overview of logic familes<br>5.2.3 nMOS | 118               |

|   |     | 5.2.4 CMOS                                    | 119               |

|   |     | 5.2.5 ECL/CML                                 | $\frac{121}{129}$ |

|   |     | 5.2.6 TTL                                     | 132               |

|   |     | $5.2.7 	 I^2L$                                | 135               |

|   |     | 5.2.8 BiCMOS                                  | 138               |

|   |     | 5.2.9 GaAs                                    | 141               |

|   | 5.3 | Bistables                                     | 145               |

|   | 5.4 | Dynamic CMOS                                  | 150               |

|   | 5.5 | Survey of logic circuits                      | 152               |

|   |     | 5.5.1 Overview                                | 152               |

|   |     | 5.5.2 Characterization and performance        | 157               |

|   |     | 5.5.3 Comparison of GaAs with Si              | 172               |

|   |     | Appendix—SPICE parameters                     | 175               |

|   |     | References                                    | 177               |

|   |     | Further reading                               | 179               |

| 6 | Ana                    | alogue circuits—techniques and performance           | 181        |

|---|------------------------|------------------------------------------------------|------------|

|   | 6.1                    | Introduction                                         | 181        |

|   | 6.2                    | Operational amplifiers                               | 181        |

|   |                        | 6.2.1 Basic concepts                                 | 181        |

|   |                        | 6.2.2 Circuit techniques                             | 186        |

|   |                        | 6.2.3 Specification and performance                  | 194        |

|   | 6.3                    | Voltage comparators                                  | 206        |

|   | 6.4                    | Voltage references and regulators                    | 209        |

|   |                        | 6.4.1 Voltage references<br>6.4.2 Voltage regulators | 209<br>215 |

|   | c r                    |                                                      | 213        |

|   | 6.5                    | Analogue signal processing<br>6.5.1 Introduction     | 224        |

|   |                        | 6.5.2 Analogue filters                               | 226        |

|   |                        | 6.5.3 ADCs                                           | 232        |

|   |                        | 6.5.4 DACs                                           | 242        |

|   |                        | 6.5.5 Specification and performance                  | 244        |

|   |                        | 6.5.6 Oversampling sigma–delta converters            | 249        |

|   |                        | References                                           | 258        |

|   |                        | Further reading                                      | 260        |

| 7 | Semiconductor memories |                                                      | 261        |

|   | 7.1                    | Introduction                                         | 261        |

|   | 7.2                    | Organization and operation                           | 263        |

|   | 7.3                    | SRAMs                                                | 267        |

|   | 7.4                    | DRAMs                                                | 271        |

|   | 7.5                    | ROMs                                                 | 277        |

|   | 7.6                    | Characterization and performance                     | 284        |

|   |                        | References                                           | 290        |

|   |                        | Further reading                                      | 291        |

| 8 | ASIC design styles     |                                                      | 293        |

|   | 8.1                    | Introduction                                         | 293        |

|   | 8.2                    | Categories                                           | 293        |

|   | 8.3                    | Gate arrays                                          | 294        |

|   | 8.4                    | Standard cells                                       | 296        |

|   | 8.5                    | Cell-based ASICs                                     | 297        |

|   | 8.6                    | Mixed-mode and analogue ASICs                        | 298        |

|   | 8.7                    | PLDs                                                 | 298        |

|   |                        | 8.7.1 PLA and PAL                                    | 298        |

|   |                        | 8.7.2 Field programmable gate arrays                 | 300        |

|   | 8.8                    | Overview                                             | 301        |

|   |                        | Further reading                                      | 302        |

| 9 | ASI                    | Cs—Programmable logic devices                        | 303        |

|   | 9.1                    | Overview                                             | 303        |

|   | 9.2                    | PAL-based PLDs                                       | 304        |

|   |                        | 9.2.1 Structures                                     | 304        |

|           |       | 9.2.2 PAL characteristics                                   | 313        |

|-----------|-------|-------------------------------------------------------------|------------|

|           | 9.3   | FPGAs                                                       | 318        |

|           |       | 9.3.1 Introduction                                          | 318        |

|           |       | 9.3.2 Selected families                                     | 319        |

|           | 9.4   | Design outline                                              | 332        |

|           |       | References                                                  | 336        |

|           |       | Further reading                                             | 337        |

| 10        | AS    | Cs—Characteristics and design issues                        | 339        |

|           | 10.1  | Introduction                                                | 339        |

|           | 10.2  | Design methodology and design tools                         | 342        |

|           | 10.3  | Design for testability                                      | 344        |

|           | 10.4  | Economics                                                   | 356        |

|           | 10.5  | Characteristics and performance                             | 362        |

|           |       | 10.5.1 Design styles                                        | 362        |

|           |       | 10.5.2 Gate arrays                                          | 365        |

|           |       | 10.5.3 Standard cells<br>10.5.4 Cell-based ASICs            | 370        |

|           |       | 10.5.4 Cen-based ASICs 10.5.5 Mixed-mode and analogue ASICs | 371        |

|           | 10.6  | Overview                                                    | 372<br>380 |

|           |       | References                                                  | 383        |

|           |       | Further reading                                             | 384        |

| 11        | A CIT | 0                                                           |            |

| 11        |       | Cs—Design techniques Overview                               | 385        |

|           | _     |                                                             | 385        |

|           |       | Design flow and methodology                                 | 387        |

|           |       | Hardware description languages                              | 398        |

|           |       | Simulation and checking                                     | 406        |

|           |       | Commercial design tools                                     | 409        |

|           |       | FPGA design tools                                           | 417        |

|           | 11.7  | Conclusions References                                      | 419        |

|           |       |                                                             | 421        |

|           |       | Further reading                                             | 423        |

| <b>12</b> |       | micron scaling                                              | 425        |

|           |       | Overview                                                    | 425        |

|           | 12.2  | MOSFET scaling                                              | 431        |

|           |       | BJT scaling                                                 | 437        |

|           | 12.4  | Interconnection scaling                                     | 439        |

|           | 12.5  | The immediate future                                        | 444        |

|           |       | References                                                  | 449        |

|           | Glos  | sary                                                        | 453        |

|           | Inde  | x                                                           | 465        |

|           |       |                                                             |            |

### Overview

#### 1.1 IC structure

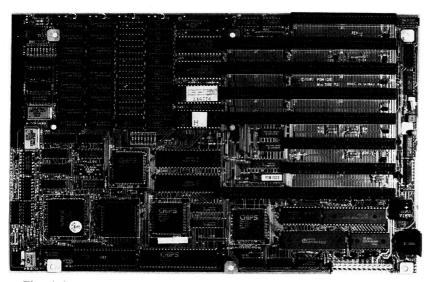

The nature of electronic equipment based on integrated circuits (ICs) is illustrated in Fig. 1.1, the photograph of a motherboard, a printed circuit board (PCB) for a personal computer (PC). The motherboard is the core of the electronics for the computer. It contains numerous ICs of various types and sizes, in addition to a few discrete components (resistors, capacitors, crystal oscillators), and sockets for interconnecting the motherboard to other PCBs. The ICs have transistor counts ranging from about 100 to 250 000 per package, and are interconnected to form a highly sophisticated system. The complexity of an IC in this era of very-large-scale integration (VLSI) is evident from the photograph in Fig. 1.2, which shows the surface of a die (signifying an unencapsulated chip). That die contains over 100 000 transistors, has 68 bonding pads, and measures about  $8\times 8~\text{mm}^2$ . It is encapsulated in a 68-pin square package not much larger than the die. This section presents a very brief outline of the structure and the processing leading to an IC.

Figure 1.3 shows the profile of a die. The electrodes of all active (transistors and diodes) and passive (resistors and capacitors) components are

Fig. 1.1 PC motherboard photograph (Courtesy of Opus Technology)