# INTRODUCTION TO DIGITAL MICROELECTRONIC CIRCUITS

GOPALAN

# Introduction to Digital Microelectronic Circuits

K. "Gopal" Gopalan

Purdue University Calumet

#### **IRWIN**

Chicago • Bogotá • Boston • Buenos Aires • Caracas London • Madrid • Mexico City • Sydney • Toronto

In recognition of the fact that our company is a large end-user of fragile yet replenishable resources, we at IRWIN can assure you that every effort is made to exceed Environmental Protection Agency (EPA) recommendations and require-

meet or exceed Environmental Protection Agency (EPA) recommendations and requirements for a "greener" workplace.

To preserve these natural assets, a number of environmental policies, both companywide and department-specific, have been implemented. From the use of 50% recycled paper in our textbooks to the printing of promotional materials with recycled stock and soy inks to our office paper recycling program, we are committed to reducing waste and replacing environmentally unsafe products with safer alternatives.

#### © The McGraw-Hill Companies, Inc., 1996

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher.

"MicroSim<sup>TM</sup> PSpice<sup>®</sup> is a registered trademark of MicroSim Corporation in the United States and other countries throughout the world. All other MicroSim product names, including MicroSim<sup>TM</sup>, are trademarks of MicroSim Corporation. Representations of MicroSim PSpice and other MicroSim products are used by permission of and are proprietary to MicroSim Corporation. Copyright 1995 MicroSim Corporation."

#### Irwin Book Team

Sponsoring editor: Scott Isenberg Marketing manager: Brian Kibby Project editor: Paula M. Buschman Production supervisor: Bob Lange Designer: Laurie J. Entringer

Manager, graphics and desktop services: Kim Meriwether

Compositor: Interactive Composition Corporation

Typeface: 10/12 Times Roman

Printer: R. R. Donnelley & Sons Company

#### Library of Congress Cataloging-in-Publication Data

Gopalan, K. Gopal

Introduction to digital electronic circuits / K. Gopal Gopalan.

p. cm. Includes index. ISBN 0-256-12089-7

1. Digital electronics. 2. Semiconductors. I. Title.

TK7868.D5G664 1996

621.39'5-dc20

95-49218

Printed in the United States of America

2 3 4 5 6 7 8 9 0 DO 2 1 0 9 8 7

#### To Kalaichelvi,

Ilango,

and

Elil

for their

love, understanding, and support

எப்பொருள் யார்யார்வாய்க் கேட்பினும் அப்பொருள் மெய்ப்பொருள் காண்ப தறிவு

To discern the truth in everything heard from whomsoever is knowledge.

Thirukkural, Chapter 42, Verse 3

Thiruvalluvar, Tamil Sage, 35 B.C.

### **PREFACE**

Of all the new technologies that have evolved in the last few decades, perhaps the digital integrated circuit (IC) technology is the one that continues to experience a phenomenal growth in terms of overall circuit complexity, switching speed, and power dissipation. This growth has created a pivotal place for teaching digital electronics in the undergraduate electrical and computer engineering curricula. The vast amount of material arising from innovative circuit designs and newer device technologies, however, requires that the circuit analysis aspects of digital electronics be covered in a first course, separated from device design and chip layout considerations. While the chip level design and layout are important in the design of Very Large Scale Integration (VLSI) systems and Application-Specific Integrated Circuits (ASIC), clear understanding of the performance characteristics of available devices is required for designers of systems using 'off the shelf' ICs. Therefore, the pedagogical approach taken in this book is to cover the analysis and performance comparison of different gate level logic circuits. Since the logic design course covers the building block implementation of a digital system, it is appropriate that the digital electronics course consider the analysis aspects of these building blocks arising from different technologies, primarily at the circuit level. A strong background in the analysis and comparative strengths of available technologies, from the circuits point of view, is required to make practical design trade-offs. For a systems architect interested in developing noncustomized systems by interconnecting standard ICs, such a background can be readily developed in a course without the chip or the physical level of design. Furthermore, with newer IC technologies appearing every few years, a thorough treatment cannot be given in a single course covering both the technologies and the circuit designs. Finally, the availability of computer-aided VLSI design tools still requires the user of these tools to choose the appropriate technology based on the requirements of a given application. Thus, the circuit level analysis provides an appreciation of the circuit design techniques and equips students for the efficient design of digital systems.

Subscribing to this philosophy of analyzing digital circuits in a single course, *Introduction to Digital Microelectronic Circuits* covers the basic gates in all of the presently available logic families. In addition, circuit configurations for VLSI implementation, interfacing of logic families, regenerative logic circuits, analog-digital interfacing, semi-conductor memories, and programmable logic devices are discussed. Where applicable, design examples based on logic level requirements are presented.

MicroSim™ PSpice® simulation of the logic families is emphasized throughout the book. PSpice is chosen because of its availability and convenience compared to other simulation tools. Since the basic logic circuits in each family typically have no more than 10 transistors, the student version of MicroSim PSpice, available at no cost from MicroSim, can readily handle the analysis. It has been the author's experience that with PSpice and personal computers, students tend to complete the simulation of a circuit and analyze the results more conveniently, and also better appreciate the importance of simulation.

Emphasis is placed on the analysis of IC gates available in the market in each logic family, while theoretical circuit configurations are considered only as possible examples.

With this emphasis and the laboratory experiments using IC and discrete (simulated) versions of gates from each family, students gain insight into the relative merits of different circuit configurations in each of the logic families studied.

#### **KEY FEATURES**

Every attempt has been made to offer a distinctive perspective on the subject of digital microelectronic circuits. In particular, this book:

- Develops the study of semiconductor devices and digital electronics for students with a background in basic circuit analysis and some exposure to physics and electronics.

- Presents a complete treatment of the analysis of bipolar logic gates, from the early RTL to the popular TTL families and the advanced Schottky TTL families.

- Provides comprehensive coverage of the basic, 10K, 10KH and 100K series of ECL gates, and the I<sup>2</sup>L gates.

- Explains thoroughly the implementation of logic gates using different configurations of MOS devices.

- Extends the analysis of digital IC families to cover the more recent BiCMOS and GaAs technologies.

- Gives a balanced treatment of regenerative logic circuits using bipolar and MOS discrete and integrated circuits.

- Includes coverage of popular methods of analog-digital data conversions.

- Introduces LSI and VLSI systems with memories and gate arrays.

- Incorporates MicroSim PSpice modeling and simulation throughout.

#### ORGANIZATION AND OUTLINE OF CHAPTERS

The book is organized into 10 chapters. Each chapter begins with an introduction and ends with a summary of key points covered, references, review questions, problems, and experiments. End-of-chapter problems serve as exercises, and are also used frequently to illustrate and/or extend some of the concepts presented in the text. Problems requiring computer simulation for analysis or design verification and those involving lengthy calculations are indicated by \*. Experiments at the end of each chapter are used to extract device parameters for readily available bipolar and MOS devices and to provide an understanding of the performance characteristics of basic logic circuits using these devices.

Chapter 1 outlines the basic steps in the design of a digital system, and the importance of analyzing a system at various levels of design. Ideal and practical logic inverter characteristics are presented.

Fundamentals of semiconductors and current conduction mechanisms are described in Chapter 2. Operation and modeling of junction diodes are discussed.

Chapter 3 gives a brief description of the structure and operation of bipolar junction transistors (BJTs). Ebers-Moll, hybrid- $\pi$ , charge-control, and MicroSim PSpice models are presented.

Static and dynamic characteristics of BJT saturation logic families are analyzed in Chapter 4. Performance improvements of different TTL families are compared.

Chapter 5 presents the analyses of different current mode logic families and their implementations in large-scale integration systems. Interfacing of saturation and current mode logic families is studied.

Chapter 6 provides a brief description of the structure and operation of MOSFETs and MESFETs. Simplified models for hand calculations and MicroSim PSpice models are presented for these devices.

Analyses of different structures of MOSFETs, BiCMOS, and gallium arsenide MES-FET logic circuits are treated in Chapter 7. Interfacing of BJT and MOS logic families is discussed.

Multivibrator circuits as a class of sequential circuits are analyzed in Chapter 8. Both discrete and integrated circuit implementations using bipolar and MOSFET devices are considered.

Chapter 9 presents various analog-digital conversion techniques.

Chapter 10 provides an introduction to the implementation of bipolar and MOS memories. Different programmable logic devices are discussed as examples of VLSI systems.

#### AUDIENCE

This text is intended for a one-semester, upper-level undergraduate course in electrical and computer engineering.

Basic knowledge of circuit analysis at the level of a first engineering circuit analysis course is assumed. Introductory level of knowledge in semiconductors and electronics is helpful, but not required. Enough material, however, is included to cover logic device characteristics, currents in semiconductors, and the structure, characteristics, and models of diodes, BJTs, and the FETs. Additionally, a concurrent (or previous) course in digital logic fundamentals is helpful.

Most of the material in this text has been used at Purdue University Calumet in a one-semester, upper-level course. The course is required for computer engineering and optional for electrical engineering students with a background in basic analog electronic circuits at the diode, BJT, and FET level. With two hours of lecture and three hours of laboratory per week, all the chapters are covered at least partially. A minimum of 12 laboratory experiments covers the characteristics of devices, logic families, multivibrators, and data converters. Most of the experiments require students to determine the performance characteristics of logic families in the lab and compare them with calculated and simulated results.

#### **ACKNOWLEDGMENTS**

The author wishes to acknowledge the reviewers for their comments at various stages of the manuscript.

The encouragement and support of the Department of Engineering, Purdue University Calumet are greatly appreciated.

# **CONTENTS**

|                                    | roduction 1                                                                                                                                                                                                                                                                                      | <ul> <li>2.4.2 Forward-Biased Diode 46</li> <li>2.4.3 Reverse-Biased Diode 51</li> <li>2.4.4 Ideal Diode Characteristics 53</li> <li>2.4.5 Temperature Dependence 53</li> </ul>                                                                                                                                                            |  |  |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                    | Digital Systems 1 Design of Digital Systems 2 Analysis of Digital Systems 5 Computer-Aided Analysis and Design of Digital Systems 6 Text Objective 7 Basic Logic Inverter Characteristics 8 1.6.1 Ideal Inverter Characteristics 8 1.6.2 Practical Inverter Characteristics 10 mary 19 rences 19 | 2.4.6 Diode Capacitances 56  2.5 Diode Models 59 2.5.1 Simplified Models for Hand Calculations 59 2.5.2 MicroSim PSpice Model 64  2.6 Diode Switching Response 68  2.7 Zener Diode 71  2.8 Schottky Diode 73  2.9 Light-Emitting Diode 75  2.10 Diodes in Digital Circuits 77  2.10.1 Diode Logic Circuits 77  2.10.2 Trigger Generator 78 |  |  |

| Review Questions 20<br>Problems 21 |                                                                                                                                                                                                                                                                                                  | Summary 79 References 79 Review Questions 80 Problems 81                                                                                                                                                                                                                                                                                   |  |  |

| INT<br>ANI                         | roduction to Semiconductors D JUNCTION DIODES 22  Enduction                                                                                                                                                                                                                                      | Chapter 3 Introduction to Bipolar Junction Transistors 84                                                                                                                                                                                                                                                                                  |  |  |

| 2.1 2.2                            | Conduction in Solids 22 Conduction in Semiconductors 26 2.2.1 Charge Carriers in Semiconductors 26 2.2.2 Conductivity of Semiconductors 29                                                                                                                                                       | Introduction 84 3.1 Simplified Structure of a BJT 84 3.2 Currents in a BJT 87 3.3 Ebers-Moll Model of a BJT 90                                                                                                                                                                                                                             |  |  |

| 2.3                                | Doped or Extrinsic Semiconductors 33 2.3.1 Donor and n-Type Doping 33 2.3.2 Acceptor and p-Type Doping 34 2.3.3 Conductivity of a Doped Semiconductor 35                                                                                                                                         | 3.4 Modes of Operation 92 3.5 BJT Characteristics 100 3.5.1 Common-Emitter Characteristics 100 3.5.2 Common-Collector                                                                                                                                                                                                                      |  |  |

| 2.4                                | <ul> <li>2.3.4 Diffusion Current 37</li> <li>2.3.5 Total Current Density 39</li> <li>pn Junction Diode 39</li> <li>2.4.1 Open-Circuit Behavior of pn Junction Diode 41</li> </ul>                                                                                                                | Characteristics 112 3.5.3 Common-Base Characteristics 113 3.6 BJT Capacitances and the Hybrid-π Model 115                                                                                                                                                                                                                                  |  |  |

CONTENTS

| 3.7   | Charge         | e-Control Model 116               |       | 4.4.3   | Standard TTL NAND Circuit 174                               |

|-------|----------------|-----------------------------------|-------|---------|-------------------------------------------------------------|

|       | 3.7.1          | Forward Active Mode 117           |       | 4.4.4   | Transfer Characteristics of Standard                        |

|       | 3.7.2          | Reverse Active Mode 121           |       |         | TTL NAND Gate 177                                           |

|       | 3.7.3          | Complete Charge-Control           |       | 4.4.5   | Fan-Out 179                                                 |

|       |                | Model 122                         |       | 4.4.6   | Propagation Delay and Power                                 |

|       | 3.7.4          | Comparison of Charge-Control      |       |         | Dissipation 182                                             |

|       |                | Model with Ebers-Moll and         |       | 4.4.7   | High-Speed TTL Gate 185                                     |

|       |                | Hybrid- $\pi$ Models 123          |       | 4.4.8   | Schottky TTL Gate 189                                       |

| 3.8   | Micro          | Sim PSpice Model for BJTs 126     |       | 4.4.9   | Advanced Schottky TTL                                       |

| 3.9   |                | Dissipation and Thermal           |       |         | Subfamilies 193                                             |

|       | Effects        |                                   |       | 4.4.10  | Performance Characteristics of TTL                          |

| Sum   | mary           |                                   |       |         | Subfamilies 197                                             |

|       | rences         |                                   |       | 4.4.11  | Tristate TTL Output 197                                     |

|       | ew Que         |                                   |       | 4.4.12  | Open Collector Gates and Expander                           |

|       | olems ]        |                                   |       |         | Gates 201                                                   |

| FIOL  | oleins i       | 133                               |       | 4.4.13  | Logic Functions in TTL                                      |

|       |                |                                   |       |         | Family 205                                                  |

| C h   | a p t e r      | 4                                 |       | 4.4.14  | TTL Circuits for LSI                                        |

| BIP   | OLAR .         | JUNCTION TRANSISTOR               |       |         | Implementation 207                                          |

|       |                | ON LOGIC FAMILIES 138             | Sum   | mary    | 209                                                         |

|       | UKAII          | ON LOGIC FAMILIES 136             | Refe  | rences  | 210                                                         |

|       |                |                                   | Revi  | ew Que  | stions 211                                                  |

| Intro | duction        | 138                               | Prob  | olems 2 | 212                                                         |

| 4.1   | The BJ         | IT Inverter 138                   |       |         |                                                             |

|       | 4.1.1          | Voltage Transfer                  |       |         |                                                             |

|       |                | Characteristics 139               |       |         |                                                             |

|       | 4.1.2          | Logic Levels and Noise            | C h   | aptei   | 5                                                           |

|       |                | Margin 141                        | Cu    | DDENT.  | MODE LOGIC                                                  |

|       | 4.1.3          | Fan-Out 141                       |       | MILIES  |                                                             |

|       | 4.1.4          | Transient Response 144            | r An  | VIILIES | 220                                                         |

|       | 4.1.5          | Switching Speed Improvement 158   |       |         |                                                             |

| 4.2   | Resisto        | r-Transistor-Logic (RTL)          | Intro | duction | 220                                                         |

|       | Family         | 160                               | 5.1   |         | Emitter-Coupled Logic (ECL)                                 |

|       | 4.2.1          | Wired-AND 161                     |       | Circuit |                                                             |

|       | 4.2.2          | Propagation Delay 162             | 5.2   |         | Integrated Circuit ECL OR/NOR                               |

| 4.3   | Diode-         | Transistor-Logic (DTL)            | J.2   |         | 225                                                         |

|       | Family         |                                   |       | 5.2.1   | Voltage Transfer                                            |

|       | 4.3.1          | Discrete DTL NAND Gate 163        |       | J.2.1   | Characteristics 228                                         |

|       | 4.3.2          | IC version of DTL Gate 167        |       | 5.2.2   | Propagation Delay 230                                       |

|       | 4.3.3          | Propagation Delay and Power       |       | 5.2.3   | Power Dissipation 233                                       |

|       |                | Dissipation 169                   |       | 5.2.4   | Fan-Out 234                                                 |

|       | 4.3.4          | Wired-AND of DTL Outputs 169      |       | 5.2.5   | Advantage of the Negative Supply                            |

|       | 4.3.5          | High-Threshold DTL Gate 170       |       | 3.2.3   | Voltage 236                                                 |

| 4.4   |                | stor-Transistor-Logic (TTL)       | 5.3   | Modifi  | •                                                           |

|       | Family         | <b>U</b> ( )                      | 5.5   | 5.3.1   | ed ECL Circuit Configurations 238 The MECL III and 10K/10KH |

|       |                | Basic TTL Inverter 172            |       | J.J.1   | Families of Gates 243                                       |

|       | 4.4            |                                   |       |         |                                                             |

|       | 4.4.1<br>4.4.2 | Multiemitter Transistor and Basic |       | 5.3.2   | The MECL 100K Family OR/NOR                                 |

5.4 ECL Circuits for LSI and VLSI

|            | Implementation 252                                 | MESFETs 320                                          |

|------------|----------------------------------------------------|------------------------------------------------------|

|            | 5.4.1 Wired Logic and Gating of ECL                | 6.7.1 N-Channel Depletion-Type                       |

|            | Circuits 252                                       | MESFET (D-MESFET) 321                                |

|            | 5.4.2 Emitter Function Logic (EFL) 257             | 6.7.2 N-Channel Enhancement-Type                     |

|            | Wiring Considerations for ECL                      | MESFET (E-MESFET) 322                                |

|            | Circuits 260                                       | 6.8 MESFET Models 323                                |

|            | Integrated-Injection Logic 264                     | 6.8.1 Curtice and Raytheon Models 323                |

|            | 5.6.1 Basic DCTL Gate 265                          | 6.8.2 MicroSim PSpice Model 325                      |

|            | 5.6.2 Standard I <sup>2</sup> L Gate 265           | Summary 331                                          |

|            | 5.6.3 Characteristics of Standard I <sup>2</sup> L | References 332                                       |

|            | Gates 271                                          | Review Questions 333                                 |

|            | 5.6.4 Schottky I <sup>2</sup> L and STL Gates 274  | Problems 333                                         |

|            | 5.6.5 Integrated Schottky Logic                    | 110000113 333                                        |

|            | Gate 276                                           |                                                      |

| 5.7        | Interfacing Saturation and Current-Mode            |                                                      |

| 3.1        | Logic Families 277                                 | Chapter 7                                            |

|            | 5.7.1 TTL-to-ECL Interfacing 278                   |                                                      |

|            | 5.7.2 ECL-to TTL Interfacing 279                   | MOSFET Logic Circuits 337                            |

|            | 5.7.3 TTLI <sup>2</sup> L Interfacing 280          |                                                      |

| C          |                                                    | Introduction 337                                     |

|            | •                                                  | 7.1 NMOSFET Inverters 338                            |

|            | rences 282                                         | 7.1.1 NMOSFET Inverter with a Resistive              |

|            | ew Questions 283                                   | Load 338                                             |

| Prob       | lems 284                                           | 7.1.2 NMOSFET Inverter with Saturated                |

|            | _                                                  | E-NMOSFET Load 343                                   |

|            | apter 6                                            | 7.1.3 NMOSFET Inverter with Linear                   |

| INT        | RODUCTION TO METAL-OXIDE-                          | E-NMOSFET Load 347                                   |

| SEL        | MICONDUCTOR FIELD-EFFECT                           | 7.1.4 NMOSFET Inverter with                          |

|            | ANSISTORS 290                                      | Depletion-Type Load 351                              |

| I KA       | ANSISTORS 270                                      | 7.1.5 Switching Response 357                         |

|            |                                                    | 7.1.6 Power Dissipation and Delay-Power              |

| Intro      | oduction 290                                       | Product 368                                          |

| 6.1        | Structure and Operation of                         | 7.1.7 Fan-Out 372                                    |

| 011        | MOSFETs 291                                        | 7.2 Complementary NOSFET (CMOS)                      |

| 6.2        | Enhancement-Type NMOSFET 291                       | Inverter 373                                         |

| 0.2        | 6.2.1 Physical Operation 292                       | 7.2.1 Transfer Characteristics 373                   |

|            | 6.2.2 Static Characteristics 296                   | 7.2.2 Fan-Out and Delay-Power                        |

|            | 6.2.3 Circuit Symbol 301                           | Product 380                                          |

| 6.3        | Depletion-Type NMOSFET                             | 7.2.3 Input Protection and Latch-Up 385              |

| 0.5        | (D-NMOSFET) 303                                    | 7.3 MOSFET Logic Gates 388                           |

| <i>-</i> 1 | p-Channel MOSFETs 305                              | 7.3.1 NMOS Gates 388                                 |

| 6.4        | Effect of Source-to-Substrate Potential:           | 7.3.2 CMOS Gates 392                                 |

| 6.5        |                                                    | 7.3.3 Dynamic and Domino Logic                       |

|            | The Body Effect 308                                | Gates 407                                            |

| 6.6        | MOSFET Equivalent Circuits 311                     | 7.4 BiCMOS Logic Circuits 415                        |

|            | 6.6.1 Circuits for Hand                            | 7.4.1 Basic BiCMOS Gates 416                         |

|            | Calculations 311                                   | 7.4.1 Basic Bickhos Gates 7.4.2 Full-Swing Gates 422 |

|            | 6.6.2 MicroSim PSpice Model 317                    | 7.T.2 1 un 5 ming 5 0000                             |

6.7 Structure and Operation of GaAs

MESFETs 320

хi

| 7.5  |                  | Arsenide MESFET Logic                                  |       | 8.4.1          | Monostable Multivibrator<br>Operation 497              |

|------|------------------|--------------------------------------------------------|-------|----------------|--------------------------------------------------------|

|      | Circuits 7.5.1   | Direct-Coupled FET Logic (DCFL)                        |       | 8.4.2          | Astable Multivibrator                                  |

|      | 7.5.1            | Circuits 424                                           |       | 02             | Operation 499                                          |

|      | 7.5.2            | Buffered FET Logic (BFL)                               | Sum   | mary 5         | 500                                                    |

|      |                  | Circuits 431                                           | Refe  | rences         | 501                                                    |

|      | 7.5.3            | Schottky Diode FET Logic (SDFL)                        | Revie | ew Ques        | tions 501                                              |

|      |                  | Circuits 433                                           | Prob  | lems 5         | 03                                                     |

|      | 7.5.4            | Other MESFET Logic Configurations 434                  |       |                |                                                        |

| 7.6  | Interfac         | sing MOS and Bipolar Logic                             |       |                |                                                        |

| 7.0  | Familie          |                                                        |       |                |                                                        |

|      | 7.6.1            | MOS-LSTTL Interfacing 437                              | 4.    |                |                                                        |

|      | 7.6.2            | MOS-ECL Interfacing 438                                |       | pter           |                                                        |

| 7.7  | Compa            | rison of Logic Families 440                            |       |                | DIGITAL DATA                                           |

| Sun  | mary - 4         |                                                        | Con   | NVERTI         | ERS 511                                                |

| Refe | erences          | 443                                                    |       |                |                                                        |

| Rev  | iew Ques         | tions 444                                              | Intro | duction        | 511                                                    |

| Prol | blems 4          | 45                                                     | 9.1   |                | -to-Analog (D/A)                                       |

|      |                  |                                                        |       | _              | rsion 511                                              |

|      |                  |                                                        |       | 9.1.1          | Binary-Weighted Resistor                               |

| C h  | apter            | 8                                                      |       |                | Network 513                                            |

|      | =                | ATIVE LOGIC                                            |       | 9.1.2          | R-2R Resistor Ladder                                   |

|      | GENERA<br>RCUITS | 451                                                    |       |                | Network 517                                            |

|      | ACUIIS           | <b>4</b> 51                                            |       | 9.1.3          | Charge Redistribution DAC 523                          |

|      |                  |                                                        |       | 9.1.4          | Conversion from Other than<br>Straight Binary Data 525 |

|      | oduction         |                                                        |       | 9.1.5          | Multiplying DACs 530                                   |

| 8.1  |                  | e Multivibrator 452                                    |       | 9.1.6          | D/A Conversion Errors 531                              |

|      | 8.1.1            | Clocked Flip-Flops 455 BJT Bistable Multivibrators and | 9.2   |                | g-to-Digital (A/D)                                     |

|      | 8.1.2            | Flip-Flops 462                                         |       |                | rsion 531                                              |

|      | 8.1.3            | MOSFET Bistable Circuits 470                           |       | 9.2.1          | Parallel/Flash ADC 533                                 |

|      | 8.1.4            | Schmitt Trigger 472                                    |       | 9.2.2          | Sample-and-Hold in ADC                                 |

|      | 8.1.5            | CMOS Schmitt Trigger                                   |       |                | Conversion 536                                         |

|      |                  | Inverter 475                                           |       | 9.2.3          | Successive Approximation                               |

| 8.2  | Monos            | table Multivibrator 479                                |       | 0.2.4          | ADC 537 Charge Redistribution ADC 541                  |

|      | 8.2.1            | Monostable Multivibrator BJT 479                       |       | 9.2.4<br>9.2.5 | Charge Redistribution ADC 541 Tracking and Dual Slope  |

|      | 8.2.2            | TTL NOR Gate Monostable                                |       | 9.2.3          | ADCs 543                                               |

|      |                  | Circuit 484                                            |       | 9.2.6          | ADC Using Voltage-to-Frequency                         |

|      | 8.2.3            | CMOS NOR Gate Monostable<br>Circuit 487                |       |                | Conversion 546                                         |

| 8.3  | Actabl           | e Multivibrator 488                                    | Sun   | ımary          | 546                                                    |

| 0.3  | 8.3.1            | BJT Astable Circuit 489                                | Refe  | erences        | 548                                                    |

|      | 8.3.2            | TTL Astable Circuit 492                                |       | iew Que        |                                                        |

|      | 8.3.3            | CMOS Astable Circuit 493                               |       | blems          |                                                        |

| 8.4  | The 55           | 55 Integrated Circuit Timer 496                        | App   | endix: I       | Basic Op Amp Characteristics 553                       |

# Chapter 10 SEMICONDUCTOR MEMORIES AND VLSI SYSTEMS 555

| Intro | duction  | 555                             |

|-------|----------|---------------------------------|

| 10.1  |          | andom Access Memory             |

|       | Organiz  | zation 55610.2Static Read-Write |

| Mem   | ory Cell | ls 559                          |

|       |          | Bipolar Static RAM Cells 559    |

|       | 10.2.2   | MOS Static RAM Cells 562        |

| 10.3  |          | Dynamic RAM 566                 |

|       | 10.3.1   | Four-Transistor NMOS Dynamic    |

|       |          | RAM 566                         |

|       | 10.3.2   | Three-Transistor NMOS Dynamic   |

|       |          | RAM 568                         |

|       | 10.3.3   | One-Transistor Cell 570         |

| 10.4  | Addres   | s Decoders 575                  |

| 10.5  | Read-C   | Only Memory 580                 |

|       | 10.5.1   | Mask-Programmable ROM 581       |

| 10.5.2 ROM Address Decoders 585           |

|-------------------------------------------|

| 10.5.3 Programmable ROM (PROM) 587        |

| 10.5.4 Erasable Programmable ROM          |

| (EPROM) 589                               |

| 10.5.5 Electrically Erasable Programmable |

| ROM (EEPROM) 591                          |

| 10.6 Sequential Access Memory 595         |

| 10.7 Programmable Logic Devices 596       |

| 10.7.1 Programmable Logic Arrays 599      |

| 10.7.2 Programmable Array Logic           |

| Devices 602                               |

| 10.7.3 Programmable Gate Arrays 605       |

| 10.8 Some VLSI Design Issues 612          |

| Summary 614                               |

| References 615                            |

| Review Questions 617                      |

| Problems 618                              |

#### **INDEX 621**

chapter

1

## Introduction

This chapter provides the motivation for the analysis and design of digital microelectronic circuits. Digital systems are used extensively in all realms of modern life. We find them in applications ranging from home appliances, entertainment systems, and palmtop computers to health care products, high-speed computers, and communication systems. More and more applications using digital techniques appear every year, with high precision, small size, and low power dissipation. Analysis of digital electronic circuits is vital to understanding present technologies of microelectronic circuits and to designing these digital systems at all levels of integration. This chapter outlines the design steps and emphasizes the use of computer-aided tools for the analysis and design of complex digital systems. As a first step in the analysis of digital electronic technologies, we examine the performance characteristics of general inverters.

#### **1.1** DIGITAL SYSTEMS

Digital systems operate on information, or data, represented in discrete form. The most common discrete form used is the binary, with two disjoint sets of voltage levels representing binary low (0) and high (1) states. With each voltage level constrained to vary within a specified range, the output of a digital system is predictable over a wide range of operating conditions. Other advantages of digital systems over analog, or linear, systems (in which information is represented by continuously varying voltages or currents) include low cost, easy extension of data size, long-time storage capability, and programmability.

Digital systems use electronic circuits that operate, most commonly, as switches, with open switch position designated as logic, or binary, 1 (or high), and closed position as 0 (or low). Alternatively, the output of a digital electronic circuit may be one of two well-defined ranges of voltages (or currents) for the two logic states. Semiconductor diodes and transistors are used as switching devices in digital systems, also called *logic* or *switching* systems. *Microelectronics* refers to the technology of fabricating a large number of electronic devices on a single chip of silicon or a compound semiconductor material such as gallium arsenide. The size of the active transistor area in chips has progressively decreased to about  $0.1 \ \mu\text{m}^2$  at present, while a density of over a million transistors is achieved

in an overall chip size of less than 100 mm<sup>2</sup> [1, 2]. Compare this area and density with those of the chips available at the beginning of the integrated circuit era, circa 1966: a chip area of approximately 5 mm<sup>2</sup>, for example, contained 50 active devices with areas of about 0.025 mm<sup>2</sup> each [3]. Simultaneous with high density, high operating speeds of close to a billion operations per second, and high data transfer rates of nearly 10 Gbits/s have recently been achieved. This remarkable increase in performance along with decrease in size is due primarily to advances in the technology of the semiconductor device fabrication process, and to the development of innovative circuit configurations.

In the following section we consider the steps in the design of a digital system.

#### **1.2** DESIGN OF DIGITAL SYSTEMS

Design of a digital system, be it a simple traffic light control system or a complex high-speed computer, proceeds with the following general steps: *specification*, *functional design*, detailed *logic design*, and *fabrication and testing*. As we will see, for the more complex of these applications, two more steps may also be needed before the final fabrication step.

As with any system, the first step in the design is the detailed specification of the requirements of the system. In this step, the design engineer determines the required number and voltage levels of inputs and outputs, speed of performance, range of power supply, physical size, and operating environment.

The next step is to create a functional model of the system. At this phase, the system is described in terms of abstract blocks, which, when interconnected, simulate the intended behavior for the given input and initial conditions. The goal in this phase is to establish the required building blocks and their interconnections to meet the gross operational specifications of the system. This step is also called the *architecture*, or *register level* design, particularly when referring to computer design. The design at this step represents the behavioral, or inputoutput, model of the system. Currently, we describe and specify the behavioral model in an abstract language such as Verilog or VHDL.<sup>1</sup>

In the next step, the *logic*, or *structural*, design considers how to implement the blocks identified in the functional design stage. While some of the blocks may be available as off-the-shelf components, others must be realized from basic elements. A divide-by-N counter, or an N bit sequence detector, for example, may not be available directly for any given value of N. A logic designer carries out the logic design of such blocks in this phase, as well as the interfacing of each block with others, if necessary. This is the primitive level of design, where one chooses the applicable technology for each functional as well as logic block, based on such considerations as power, size, and speed.

<sup>&</sup>lt;sup>1</sup> Verilog is a registered trademark of Cadence Design Systems, Inc. VHDL, which stands for VHSIC (very high speed integrated circuits) Hardware Description Language, was developed with the sponsorship of the U.S. Department of Defense.

The final step is the fabrication of the blocks in printed circuit boards and performance-testing of the assembled system. In this step, all the blocks identified in the previous steps are interconnected with appropriate power and signal sources. A test engineer validates the completed system by supplying or simulating the specified inputs and monitoring the outputs from the system.

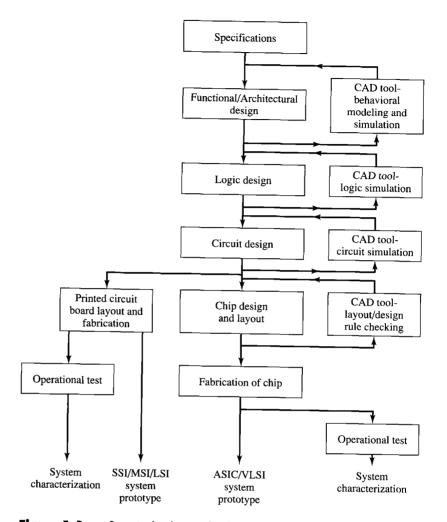

The above process for a system design assumes the use of readily available. off-the-shelf components: at the logic design level, small-scale integration (SSI) circuits for gates and flip-flops, and, at the functional level, medium-scale integration (MSI) circuits such as counters and shift-registers, and, in some cases, large-scale integration (LSI) circuits, such as memory and logic arrays,<sup>2</sup> For a number of applications with low volume, and/or those that will need changes in specifications with time, this design methodology is sufficient. However, the process has several limitations for use in applications where size and power dissipation are also primary considerations. When there are number of different circuits at different integration levels, sizes, power, and cost, these add to the overall cost, power, size, and assembly and testing time. For example, a digital time/temperature display unit or a marquee sign can be built efficiently using SSI, MSI, and LSI components; a wristwatch or a notebook computer, on the other hand, becomes costly and prohibitively large in size, and dissipates a disproportionate amount of power for its application when built with off-theshelf integrated circuits. In addition, the advantages of high-speed technology at the gate and the functional levels would be lost in the system due to the extensive wiring and interconnection needed. To achieve a more appropriate design for such applications the designer extends the previous design steps from the logic (or gate) level of design to the circuit level, then the chip (device) layout level. and, finally, arrives at chip fabrication. Figure 1.1 shows the complete design steps. Because the final product here is a single chip for a given application, it is an application-specific integrated circuit (ASIC). It is also a very large scale integration (VLSI) circuit if its size exceeds 10,000 equivalent gates.

Unlike in MSI/SSI-level design, VLSI and ASIC circuits have stringent constraints while offering flexibility at the circuit and chip level of design. For example, because of its small size, the number of external pins (connections) in an ASIC or VLSI circuit is limited to a few hundred. As a result, some of the input signals may need to be generated internally, and the number of output lines may be limited. This, in turn, could result in lower performance, increased size, more components, and more design changes. Size is also a significant factor in determining maximum power dissipation within the chip and the operating supply voltage. The functional level design must, therefore, consider size with other specifications. Design at the logic level in ASIC and VLSI circuits must minimize redundancy, to ensure the minimum number of gates and to minimize size. In addition, design at the circuit level—which is the primitive level for a given technology of ASIC or VLSI circuits—must obtain optimum gate circuit

<sup>&</sup>lt;sup>2</sup> Generally accepted definitions for scale of integration are: 1 to 10 gates per chip: SSI; 10 to 100 equivalent gates per chip: MSI; 100 to 10,000 equivalent gates, or memory bits per chip: LSI; and over 10,000 equivalent gates: VLSI (very large scale integration). For chips with a million or more equivalent gates, the term ULSI (ultra large scale integration) is sometimes used. In all these cases, a gate represents the basic block—an inverter, typically—in the given technology.

Figure 1.1 Steps in the design of a digital system

configuration in terms of speed, power, and size. Finally, careful layout at the chip level ensures that a compact chip results, with the architecture dsigned at the functional level. Testing of the chip after fabrication verifies that the final circuit meets all of the performance specifications: static, dynamic, power, and environmental.

Because of the interrelationship among the design phases, a digital system design engineer must have expertise in one or more levels and must know enough in all other levels to design and fabricate efficient systems. An architecture for adding N bits of data, for example, may be more efficient using serial addition than parallel addition if the source bits are given serially at a high rate. Therefore, an understanding of the adder implementation at the register level helps the design engineer achieve an efficient design. Similarly, at the logic level, a combi-

nation of multiplexers or a programmable logic device might cut down design time and costly layout of different circuit patterns for realizing multiple logic functions in many variables. An innovative circuit design might, on the other hand, reduce size and power or increase speed of operation. With device technology advancing rapidly, the choices of available technology are crucial in determining overall performance and cost. If a design objective is the operation of a digital system at data transfer rates exceeding hundreds of Mbits/s, then a good choice might be Emitter-Coupled Logic (ECL), Bipolar-Complementary Metal-Oxide Semiconductor (BiCMOS), or gallium arsenide Metal-Semiconductor Field Effect Transistor (GaAs MESFET) technology. If, in addition to high speed, the system must dissipate low power, the choice is narrowed to BiCMOS technology, which has operating speeds rivaling that of ECL but at significantly reduced power dissipation. At present, ECL has the highest power dissipation; GaAs MESFET technology, on the other hand, exceeds ECL in speed but is more expensive due to its low yield and has not attained the same level of maturity as other technologies. However, with advances in GaAs device fabrication technology, data rates exceeding Gbits/s have been achieved. Additionally, we have recently seen the development of high density MOS (Metal-Oxide-Semiconductor) implementation of memory devices with storage capacities in the Gbit range. Clearly, these types of developments in technology must be considered in the design of high-speed, high-density, and low-power digital systems.

#### 1.3 Analysis of Digital Systems

To develop an error-free digital system in the form of a VLSI circuit, one must verify design at every step. Analysis of the functional level design blocks and their interconnections is necessary to check the input-output logic functionality of the system. Logic level analysis verifies the truth table, state table and/or flow table for each block and identifies timing errors (glitches, races, and hazards).<sup>3</sup> Analysis of basic gate circuits in a given technology presents static and dynamic performance characteristics and helps in devising novel configurations to meet overall design objectives. Verification of chip design is essential in a complex circuit to avoid costly and time-consuming errors when laying out active devices and making interconnections. In addition, layout must be checked for parasitic devices, noise sources and, more frequently, capacitances. Clearly, the top-down design approach has local feedback paths at each level so that problems identified during analysis can be corrected. This type of iterative design based on analysis and feedback is indispensable to meet all the performance specifications of the system and to prevent malfunctioning under all operating conditions. Finally, characterization of the final product by testing under

<sup>&</sup>lt;sup>3</sup> For a detailed discussion of these topics, the reader is referred to logic design textbooks such as Roth [7] or Wakerly [8].