# PERGING NANOELECTRONIC DEVICES

Edited by

AN CHEN • JAMES HUTCHBY • VICTOR ZHIRNOV • GEORGE BOURIANOFF

WILEY

# EMERGING NANOELECTRONIC DEVICES

An Chen

GLOBALFOUNDRIES, USA

**James Hutchby**

Semiconductor Research Corporation, USA

Victor Zhirnov

Semiconductor Research Corporation, USA

**George Bourianoff**

Intel Corporation, USA

This edition first published 2015 © 2015 John Wiley and Sons Ltd

Registered office

John Wiley & Sons Ltd, The Atrium, Southern Gate, Chichester, West Sussex, PO19 8SQ, United Kingdom

For details of our global editorial offices, for customer services and for information about how to apply for permission to reuse the copyright material in this book please see our website at www.wiley.com.

The right of the author to be identified as the author of this work has been asserted in accordance with the Copyright, Designs and Patents Act 1988.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, except as permitted by the UK Copyright, Designs and Patents Act 1988, without the prior permission of the publisher.

Wiley also publishes its books in a variety of electronic formats. Some content that appears in print may not be available in electronic books.

Limit of Liability/Disclaimer of Warranty: While the publisher and author have used their best efforts in preparing this book, they make no representations or warranties with respect to the accuracy or completeness of the contents of this book and specifically disclaim any implied warranties of merchantability or fitness for a particular purpose. It is sold on the understanding that the publisher is not engaged in rendering professional services and neither the publisher nor the author shall be liable for damages arising herefrom. If professional advice or other expert assistance is required, the services of a competent professional should be sought

This work is supported in part by Semiconductor Research Corporation (SRC), Defense Advanced Research Projects Agency (DARPA), and the National Science Foundation (NSF).

#### Library of Congress Cataloging-in-Publication Data

Emerging nanoelectronic devices / edited by Dr An Chen, Dr James Hutchby, Dr Victor Zhirnov, Dr George Bourianoff.

pages cm

Includes bibliographical references and index.

ISBN 978-1-118-44774-1 (cloth)

1. Nanoelectronics. 2. Nanoelectromechanical systems. 3. Nanostructured materials. I. Chen, An (Electronics engineer), editor. II. Hutchby, James, editor. III. Zhirnov, Victor V., editor. IV. Bourianoff, George, editor.

TK7874.84.E32 2014

621.381-dc23

2014029299

A catalogue record for this book is available from the British Library.

Set in 10/12 pt TimesLTStd-Roman by Thomson Digital, Noida, India Printed and bound in Malaysia by Vivar Printing Sdn Bhd

# EMERGING NANOELECTRONIC DEVICES

#### To Linda Wilson

### **Preface**

Continued dimensional and functional<sup>1</sup> scaling of CMOS<sup>2</sup> integrated circuit technology is driving information processing<sup>3</sup> systems into a broadening spectrum of new applications. Many of these applications are enabled by performance gains and/or increased complexity realized by scaling. Because dimensional scaling of CMOS eventually will approach fundamental limits, several new alternative information processing devices and microarchitectures for existing or new functions are being explored to sustain the historical integrated circuit scaling cadence and reduction of cost/function in future decades. This is driving interest in new devices for information processing and memory, new technologies for heterogeneous integration of multiple functions (a.k.a. "More than Moore"), and new paradigms for systems architecture.

This book is based on the ITRS Emerging Research Device (ERD) International Technical Work Group's efforts over more than ten years to survey, research, and assess many of these new devices. As such, it provides an ITRS perspective on emerging research nanodevice technologies and serves as a bridge between CMOS and the realm of nanoelectronics beyond the end of CMOS dimensional and equivalent functional scaling. (Material challenges related to emerging research devices are addressed in a complementary ITRS chapter entitled *Emerging Research Materials*.)

An overarching goal of the ERD is to identify, assess, and catalog viable new information processing devices and systems architectures for their long-range potential and technological maturity, and to identify the scientific/technological challenges gating their acceptance by the semiconductor industry as having acceptable risk for further development. The intent is to provide an objective, informative resource for the constituent nanoelectronics communities pursuing: (1) research, (2) tool development, (3) funding support, and (4) investment, each directed to developing a new information processing technology. These communities include universities, research institutes, industrial research laboratories, tool suppliers, research funding agencies, and the semiconductor industry.

<sup>&</sup>lt;sup>1</sup> Functional Scaling: Suppose that a system has been realized to execute a specific function in a given, currently available, technology. We say that system has been functionally scaled if the system is realized in an alternate technology such that it performs the identical function as the original system and offers improvements in at least one of size, power, speed, or cost, and does not degrade in any of the other metrics.

<sup>&</sup>lt;sup>2</sup> Martin Hilbert and Priscila López, 2001, "The World's Technological Capacity to Store, Communicate, and Compute Information", *Science*, 332(6025), 60–65.

<sup>&</sup>lt;sup>3</sup> Information processing refers to the input, transmission, storage, manipulation or processing, and output of data. The scope of this book is restricted to data or information manipulation, transmission, and storage.

xx Preface

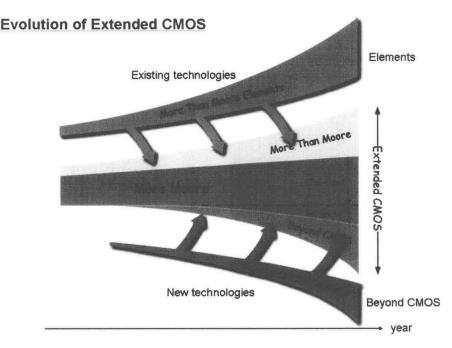

**Figure P.1** Relationship between More Moore, More than Moore, and Beyond CMOS (Source: ERD, Japan)

This goal is accomplished by addressing two technology-defining domains: (1) extending the functionality of the CMOS platform via heterogeneous integration of new technologies, and (2) stimulating the invention of a new information processing paradigm. The relationship between these domains is schematically illustrated in Figure P.1. The expansion of the CMOS platform by conventional dimensional and functional scaling is often called "More Moore". The CMOS platform can be further extended by the "More than Moore" approach which is a relatively new subject. On the other hand, new information processing devices and architectures are often called "Beyond CMOS" technologies and are the main subjects addressed in this book. The heterogeneous integration of "Beyond CMOS" and "More than Moore" onto the "More Moore" platform will extend CMOS functionality to form the ultimate "Extended CMOS".

The book is partitioned into five sections: (1) Introduction, including a fundamental description of the physics of some nanodevices, (2) nanoelectronic memory devices, (3) nanoelectronic logic information processing devices, (4) concepts for emerging architectures, and (5) summary, conclusions, and outlook for nanoelectronic devices. Some detail is provided for each entry regarding operation principles, advantages, technical challenges, maturity, and its current and projected performance. Also included is a device and architectural focus combining emerging research devices offering specialized, unique functions as heterogeneous core processors integrated with a CMOS platform technology. This represents the nearer-term focus of this work, with the longer-term focus remaining on the discovery of an alternate information processing technology to supplement and to eventually replace digital CMOS.

## List of Contributors

Ethan C. Ahn, Department of Electrical Engineering, Stanford University, USA

Masakazu Aono, WPI Center for Materials Nanoarchitectonics, National Institute for Materials Science, Japan

**Tetsuya Asai**, Graduate School of Information Science and Technology, Hokkaido University, Japan

Behtash Behin-Aein, GLOBALFOUNDRIES Inc., USA

Benjamin F. Bory, Eindhoven University of Technology, The Netherlands

George Bourianoff, Components Research Group, Intel Corporation, USA

Geoffrey W. Burr, IBM, USA

An Chen, GLOBALFOUNDRIES Inc., USA

**Donald M. Chiarulli**, Department of Electrical and Computer Engineering, University of Pittsburgh, USA

György Csaba, University of Notre Dame, USA

Shamik Das, Nanosystems Group, The MITRE Corporation, USA

Denver H. Dash, Intel Science and Technology Center, USA

Supriyo Datta, Purdue University, USA

Vinh Quang Diep, Purdue University, USA

S. Burc Eryilmaz, Department of Electrical Engineering, Stanford University, USA

Yan Fang, Department of Electrical and Computer Engineering, University of Pittsburgh, USA

Scott Fong, Department of Electrical Engineering, Stanford University, USA

**Aaron D. Franklin**, Department of Electrical and Computer Engineering and Department of Chemistry, Duke University, USA

Paul Franzon, North Carolina State University, USA

Tsuyoshi Hasegawa, WPI Center for Materials Nanoarchitectonics, National Institute for Materials Science, Japan

xxii List of Contributors

Toshiro Hiramoto, Institute of Industrial Science, The University of Tokyo, Japan

James Hutchby, Semiconductor Research Corporation, USA

Louis Hutin, Department of Electrical Engineering and Computer Sciences, University of California, USA

Adrian M. Ionescu, Ecole Polytechnique Fédérale de Lausanne, Switzerland

Mahdi Jamali, University of Minnesota, USA

Rakesh Jeyasingh, Department of Electrical Engineering, Stanford University, USA

Alexander Khitun, Material Science and Engineering, University of California, USA

Angeline Klemm, University of Minnesota, USA

Takhee Lee, Department of Physics, Seoul National University, Korea

Steven P. Levitan, Department of Electrical and Computer Engineering, University of Pittsburgh, USA

Eike Linn, Institute of Electronic Materials II, RWTH Aachen University, Germany

Tsu-Jae King Liu, Department of Electrical Engineering and Computer Sciences, University of California, USA

Matthew J. Marinella, Sandia National Laboratories, USA

Hao Meng, Data Storage Institute, Singapore

Stephan Menzel, Peter Grünberg Institut (PGI-7), Forschungszentrum Jülich, Germany

Stefan C.J. Meskers, Eindhoven University of Technology, The Netherlands

Michael T. Niemier, University of Notre Dame, USA

**Ferdinand Peper**, Center for Information and Neural Networks, National Institute of Information and Communications Technology, USA

Wolfgang Porod, University of Notre Dame, USA

Mark A. Reed, Departments of Electrical Engineering and Applied Physics, Yale University, USA

Frank Schwierz, Technical University of Ilmenau, Germany

Hyunwook Song, Department of Applied Physics, Kyung Hee University, Korea

Narayan Srinivasa, Center for Neural and Emergent Systems, HRL Laboratories LLC, USA

Ken Takeuchi, Chuo University, Japan

Jian-Ping Wang, University of Minnesota, USA

**Rainer Waser**, Institute of Electronic Materials II, RWTH Aachen University, Germany; Peter Grünberg Institut (PGI-7), Forschungszentrum Jülich, Germany

H.-S. Philip Wong, Department of Electrical Engineering, Stanford University, USA

Victor V. Zhirnov, Semiconductor Research Corporation, USA

## Acronyms

1D1R 1-Diode-1-resistor 1S1R 1-Selector-1-resistor

1T One transistor

1T1C 1-Transistor-1-capacitor 1T1R 1-Transistor-1-resistor

2DEG Two-dimensional electron gas

3D Three dimensional AD Analog digital AF Anti-ferromagnetic

AIST Silver (Ag) Indium (In) Antimony (Sb) Tellurium (Te)

ALD Atomic layer deposition AM Associative memory

ASIC Application specific integrated circuit

ASL All-spin logic

BARITT diode Barrier-injection transit-time diode

BBE Brain, body, environment based interactions

BBL Buried bit line BDA 1,4-Benzenediamine

BDC60 Bis(fullero[c]pyrolidin-1y1)benzene

BDT 1,4-Benzenedithiol

BE Bottom electrode

BEC Bottom electrode contact

BEOL Back end of line

BFO Bismuth ferrite (BiFeO3)

BiSFET Bilayer pseudo-spin field-effect transistor

BIST Built-in self-test

BJT Bipolar junction transistor

BL Bit line

BLG Bilayer graphene BN Beyond Neumann

CA Cellular automata

CAM Contend addressable memory

xxiv Acronyms

CBL Cantilever bit line

CBRAM Conductive-bridge random access memory

CDMA Code division multiple access

CMIS Current-induced magnetization switching

CMOS Complementary metal oxide semiconductor

CNT Carbon nanotube

CNTFET Carbon nanotube field-effect transistor

CO Carbon monoxide

CoFeB Cobalt iron boron

CoPt Cobalt platinum

CP-AFM Conducting probe—atomic force microscopy

CPP Current perpendicular to plane

CPU Central processing unit

CRS Complementary resistive switch

CTAFM Conductive-tip atomic force microscopy

D Density of states

DC Direct contact

DC8 to DC12 Eight to 12 carbon atoms in alkanedithiols

dCNT Carbon nanotube diameter

DFT Density functional theory

DIBL Drain induced barrier lowering

DMRG method Density matrix renormalization group method

DNA Deoxyribonucleic acid

DoM Degree of match

DOS Density of states

DRAM Dynamic random access memory

DVD Digital versatile disc

e Elementary charge of an electron EBIC Electron beam induced current EBJs Electromigrated break junctions

EEPROM Electrically erasable programmable read only memory

Eg Energy bandgap EM Electromechanical

EMB Electrochemical metallization bridge

EOT Equivalent oxide thickness ERD Emerging research devices

FD Fully depleted

FeFET Ferroelectric field effect transistor

Fe-NAND Ferroelectric NAND

FeRAM Ferroelectric random access memory

FERET Facial recognition technology

FET Field-effect transistor FIB Focused ion beam

FinFET Multi-gate MOSFET with fin-shaped active structure

Acronyms

FL Free layer

FM Ferromagnetic

FN Fowler–Nordheim

FOPE Fluorinated oligomer

FPGA Field programmable gate array

FRAM Ferroelectric random access memory

FTJ Ferroelectric tunnel junction FWHM Full width at half maximum

GAA Gate all around

GaAs Gallium arsenide

GMR Giant magnetoresistive

GNM Graphene nanomesh

GNR Graphene nanoribbon

GQ Quantum conductance

GSHE Giant spin Hall effect

GST Germanium (Ge), Antimony(Sb), Tellurium(Te)

h Planck's constant

HAO Hf-Al-O HDD Hard disk drive

HEMT High electron mobility transistor

HF Hydrofluoric acid HKMG High-k metal gate

HMAX Hierarchical memory and X HOMO Highest occupied molecular orbital

HP High performance HRS High resistance state

HTM Hierarchical temporal memory

IC Integrated circuit

ICT Information and communication technologies

IEDM International Electron Devices Meeting

IETS Inelastic electron tunneling spectroscopy

I-MOS Impact-ionization MOS InAlAs Indium aluminum arsenide

InAs Indium arsenide

InGaAs Indium gallium arsenide iNML In-plane nanomagnet logic

InP Indium phosphide

InSb Indium antimonide

$I_{\text{off}}$  Off current  $I_{\text{on}}$  On current

IOP Input-output processor

IPCM Interfacial phase change memory

ITRS International Technology Roadmap for Semiconductors

xxvi Acronyms

KJMA Kolmogorov, Johnson and Mehl, and Avrami

$L_{\rm ch}$  Channel length LEC Lyric error correction

$L_{\rm g}$  Gate length

LLG Landau-Lifshitz-Gilbert LRS Low resistance state  $L_{\rm spr}$  Spacer length LtN Less than Neumann

LUMO Lowest unoccupied molecular orbital

m Carrier effective mass MC Magneto current ratio

MCBJs Mechanically controllable break junctions

MEMS Micro-electro-mechanical systems

MFIS Metal ferroelectric insulator semiconductor

MFTJ Multiferroic tunnel junctions

MG Multigate

mHEMT Metamorphic HEMT

MIEC Mixed ionic electronic conduction

MIM Metal-insulator-metal

MIT Metal-insulator transition

MLC Multi level cell

MO-BF Metal oxide-bipolar filamentary

MOS Metal oxide semiconductor

MoS<sub>2</sub> Molybdenum disulfide

MoSe<sub>2</sub> Molybdenum diselenide

MOSFET Metal oxide semiconductor field-effect transistor

MO-UF Metal oxide-unipolar filamentary

MOCA: Magnetic quantum-dot cellular automata

MRAM Magnetic random access memory

M-SCM Memory class storage class memory

MTJ Magnetic tunnel junction

MtN More than Neumann

Nc Nanocrystal

NCC Nano-current channel

ND Notre Dame

NEMory Memory cell based on a NEMS switch NEMS Nano-electro-mechanical systems

NIST: National Institute of Standards and Technology

NML Nanomagnet logic nMOSFET n-Channel MOSFET N-T N-Terminal relay NV Nonvolatile

NVM Nonvolatile Memory

NWFET Nanowire field-effect transistor

Acronyms xxvii

ODT Au-octanedithol junction

ONO Oxide–nitride–oxide

OOMMF Object oriented micromagnetic framework

OPE Oligophenyleneethynynylene

OPI Oligophenyleneimine

OPV Oligophenylenevinylene

OS Operating system

OTP One-time programmable

OTS Ovonic threshold switch

PABA Persistent asynchronous background activity

PC Phase change

PCB Phase change bridge

PCM Phase change memory

PCRAM Phase change random access memory

PDMS Polydimethylsiloxane

PE Piezoelectric

PE: Processing element

PET Piezoelectronic transistor

PF Poole Frenkel

PFM Piezoresponse force microscopy

pHEMT Pseudomorphic HEMT

PIDS Process integration, devices, and structures

PLA Programmable logic array

PLL Phase-locked loop PM Permanent magnet pMA Pars-mercaptoaniline

PMA Perpendicular magnetic anisotropy

PMN-PT Lead magnesium niobate – lead titanate

pMOSFET p-Channel MOSFET

pNML: Perpendicular nanomagnet logic

PR Piezoresistive

PS-MOSFET Pseudo-spin MOSFET

PZN-PT Lead zinc niobate-lead titanate

PZT Lead zirconate titanate

QCA Quantum-dot cellular automata

R Read

R6G Rhodamine

RA Resistance × area

RAM Random access memories

$R_{\rm c}$  Contact resistance

RC Time constant of a circuit composed of resistors and capacitors

RDF Random dopant fluctuation

ReRAM Redox resistive random access memory

RF Radio frequency

xxviii Acronyms

RIE Reactive ion etch

RL Reference layer

RQ Quantum resistance

RRAM Resistive random access memory

RTD Resonant tunneling diode

RWL Read word line

SAM Self-assembled monolayer

SB Schottky barrier

SBM Suspended beam memory

SBT SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>

SCE Short channel effect

SCLC Space-charge limited conduction

SCM Storage class memory

SEM Scanning electron microscopy

SERS Surface-enhanced Raman spectroscopy

SET Single electron transistor SEU Single event upset

SFD: Switching field distribution

SG Suspended gate

Si Silicon

SLL Super lattice like

SNDM Scanning nonlinear dielectric microscopy

SNM Static noise margin

SoC System on a chip

SOI Silicon on insulator

SPDT Single pole double-throw

SPT Structural phase transition

SR Structural relaxation

SR Stochastic resonance

SRAM Static random access memory

SS Subthreshold swing

S-SCM Storage class storage class memory

SSD Solid state disk STD Spin torque device

STDP Spike timing dependent plasticity

STM Scanning tunneling microscopy

STM-BJ Scanning tunnel microscope controlled break junction

STMG Spin torque majority logic gate

STNO Spin torque nano-oscillator

STS Scanning tunneling spectroscopy

STS Subthreshold slope STT Spin transfer torque

STT-MRAM Spin torque transfer magnetic random access memory

SWD Spin wave devices

SWNT Single walled carbon nanotube