# MICROPROCESSORS THEORY & Applications

Gene A. Streitmatter Vito Fiore

## MICROPROCESSORS Theory and Applications

Gene A. Streitmatter Vito Fiore

Associate Professors Electronics Technology Rock Valley College Rockford, Illinois

#### Library of Congress Cataloging in Publication Data

Streitmatter, Gene A

Microprocessors.

Bibliography: p. 443

Includes index.

1. Microprocessors. I. Fiore, Vito, joint author. II. Title.

QA76.5.S783 001.6'4'04 78-31466

ISBN 0-8359-4371-2

© 1979 by Reston Publishing Company, Inc. A Prentice-Hall Company Reston, Virginia 22090

All rights reserved. No part of this book may be reproduced in any way, or by any means, without permission in writing from the publisher.

10 9 8 7 6 5 4 3 2

Printed in the United States of America

#### **PREFACE**

Advances in the area of large-scale integration have brought about the development of a solid state device called a microprocessor. Because microprocessors represent a considerable advance in the area of integrated circuit technology and promise to be the nucleus of electronics of the future, this book provides the required reorientation from traditional techniques used in controls and data processing to a versatile programmable controller. An introductory middle-ground approach between hardware and software is taken, which combines software and hardware applications without concentrating exclusively on one or the other.

Universal concepts applicable to all models of microprocessors are presented in Chapters 1 through 9. The book is organized in a linear progression from fundamental principles to complete systems covering both the Motorola MC6800 and Intel 8080 microprocessors in Chapters 10 through 14. The Intel 8080 and Motorola MC6800 have been used throughout the text since their software and hardware serve as typical examples of today's microprocessors.

Starting in Chapter 1 with a general overview of microprocessors which establishes a working language and basic understanding of some of the fundamental concepts, each chapter builds on the previous ones. For example, Chapter 5, "Introduction to Software," presents the basic skills and procedures of programming. In Chapter 9, "Advanced Software," these basic concepts can be discussed in more detail since the intervening chapters on bus control, input/output and memory have provided the necessary background for mastering more specific information.

The final chapters, 10 through 14, contain specific details and applications of the Intel 8080 and Motorola MC6800 which bring together all the fundamental concepts learned in the earlier chapters.

xviii Preface

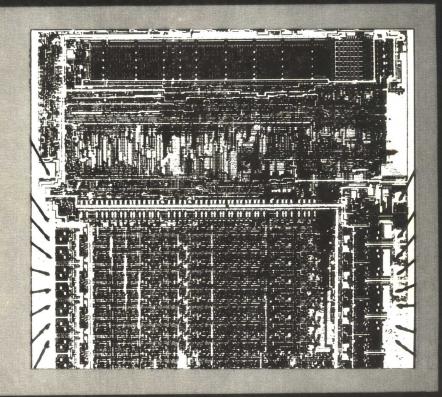

This text contains over one hundred illustrations of circuits, programs, charts, subsystems and systems and photographs of micro dies, which directly reinforce the textual information.

A glossary of new terms is provided at the beginning of each chapter. A general glossary containing all these terms as well as additional ones is located at the back of the book.

The appendixes contain extensive reference information including instruction sets for the Motorola MC6800 and the Intel 8080 and supplemental technical data such as numbering systems, conversion tables, integrated circuit listings, standard logic symbols and a coding system.

Upon completing this book, the reader should have gained the fundamental insights necessary to understanding and learning microprocessors which will serve as the framework for continued study in this exciting, state-of-the-art technology.

#### **ACKNOWLEDGMENTS**

The authors acknowledge with appreciation the permission granted by Motorola Inc. and Intel Corporation to reprint their copyrighted instruction set material, which appears in Appendix 5. Furthermore, various diagrams, photos, tables and figures that are noted as courtesy of Hewlett-Packard, Intel Corporation and Motorola Inc. have been reprinted from copyrighted material with the manufacturers' permission from the following manuals:

Hewlett-Packard 59309A HP-IB Digital Clock Operating and Service Manual, 1976. (Fig. 13-3, 13-4, 13-5)

Intel 8080 Microcomputer Systems User's Manual, 1975. (Fig. 7-7, 7-9; 10-1, 10-2, 10-3, 10-4, 10-5, 10-6, 10-7, 10-8; 11-4, 11-5, 11-6; Table 7-1)

Intel Memory Design Handbook, 1977. (Fig. 8-5, 8-6, 8-7, 8-8, 8-9, 8-10, 8-11, 8-12)

Intel MCS85 Training Course, 1977. [Some diagrams have been modified] (Fig. 10-9, 10-10, 10-11, 10-12)

Intel SDK-85 User's Manual, 1977. (Table 9-2)

Motorola TTL Integrated Circuits Data Book, 1971. (Fig. 3-13)

Motorola M6800 Programming Reference Manual, first ed., 1976. (Fig. 4-4)

Motorola M6800 Microcomputer System Design Data, 1976. (Fig. 7-11; 12-1, 12-2, 12-3, 12-4, 12-5, 12-6; Tables 12-1, 12-2, 12-3, 12-4, 12-5, 12-6, 12-7, 12-8)

Motorola M6800 Microprocessor Course, 1977. (Fig. 8-1, 8-2, 8-3, 8-4)

Motorola MEK6800D2 Manual, second ed., 1977. (Fig. 14-12, 14-14; Table 4-2, 9-1)

xx Acknowledgments Motorola M68ADS1A Development System User's Manual, 1978. (Fig. 14-16, 14-17)

The following people have played an important role of assistance in providing technical information and leads to sources of material: Ron Bishop, Don Jackson, Lothar Stern, Fuad Musa and Fred Elkin of Motorola Inc.; Tom Lehmann and Rob Walker of Intel Corporation; Ravinder Bhatnager and Ed Morgado of American Microsystems, Inc. A special thanks to Dave Kugler of Hewlett-Packard Company.

A very special thanks is due Fritz Wilson of Motorola Inc., Phoenix, Arizona, for his continuous support and personal encouragement throughout the entire preparation of this text.

The authors appreciate the guidance and encouragement given to them and the professional polish added to the text by the staff of Reston Publishing Company, Inc., especially Lawrence J. Benincasa, Editor, and Linda Weigle, Production Editor. Thanks also to Frances Myles, Prentice-Hall representative, for her enthusiasm and encouragement regarding this book.

Of special assistance to the authors during the writing of this book were Helen Dolezal, who spent many long hours proofreading the original manuscript, and Vicki Fiore, our "manuscript consultant," who put in hours and hours of work into the wee hours of the morning at her typewriter. No undertaking of this type can be successful without the dedication and effort of people like them.

Also, Roger Leid, Chairman of the Division of Technology at Rock Valley College, Rockford, Illinois, who has been very supportive with his constant encouragement and, most of all, his endless amount of patience with both of us during this writing time.

Last, but certainly not least, our deepest gratitude to William F. Ridgway for the hundreds of hours spent in designing and manufacturing the microprocessor training equipment that provided us with the applications needed to develop our understanding of the hardware side of this fascinating field of electronics.

#### **CONTENTS**

LIST OF ILLUSTRATIONS xi LIST OF TABLES xv PREFACE xvii ACKNOWLEDGMENTS xix

- 1 INTRODUCTION TO THE MICROPROCESSOR 1

The Microprocessor, 3

Major Concepts of Microprocessors, 6

Software Concepts, 12

Questions, 13

- 2 BINARY INTRODUCTION 15 Numbering Systems, 16 Arithmetic, 19 Complement Methods, 24 Fractions, 30 Summary, 32 Questions, 32

- 3 DIGITAL CONCEPTS FOR MICROPROCESSORS 35 Active Gates, 36 Flip-Flop Applications, 45 Decoders, 48 Code Converters, 53 Summary, 56 Questions, 56

- 4 THE INSTRUCTION SETS 59 CPU Programming Model, 60 Programs in Memory, 62 Instruction Set Terminology, 64

viii Contents

The Instructions, 67

Summary, 72

Questions, 75

- 5 INTRODUCTION TO SOFTWARE 77

Fundamental Programming Concepts, 78

Constructing the Program, 80

Example Problem, 84

Commonly Used Concepts, 89

Questions, 93

- 6 BUS CONTROL 95

System Review, 96

Timing and Control, 97

Address Bus, 103

Data Bus, 107

Control Bus—Line Definitions, 107

Questions, 108

- 7 INPUT/OUTPUT 109

Ports and Porting, 110

Nonprogrammable Ports, 112

Programmable Ports, 121

Manufactured Devices, 123

Summary, 131

Questions, 131

- 8 MEMORY 133

Relationship CPU and Memory, 134

RAM, 135

ROM, 137

EPROM, 139

PROM, 142

Summary, 144

Questions, 146

- 9 ADVANCED SOFTWARE 147 Introduction and Review, 148 Assembly Level Programming, 148 Some Common Techniques, 156 Debugging, 163 Summary, 166 Questions, 166

- 10 THE INTEL 8080: ARCHITECTURE AND SUPPORT CHIPS 169

Architecture of a CPU, 170

Architecture of the 8080 CPU, 174

Support Chips, 176

Interrupting Ports, 183

Support Chips for Interrupt, 187

DMA, 194

Questions, 197

11 INTEL 8080 APPLICATIONS 201 Circuit Discussion, 201 Program Discussion, 210 Output Port, 216 Summary, 218

THE MOTOROLA 6800: ARCHITECTURE AND SUPPORT CHIPS 219

System Component Descriptions, 220

Microprocessor Interface Lines, 225

Peripheral and Memory Interface Lines, 226

Static and Dynamic Characteristics, 228

A Minimum System, 233

MPU Address Modes, 238

Processor Controls, 244

Summary, 253

13 MOTOROLA 6800 APPLICATIONS 255

The IEEE 488-1975 General Purpose Interface Bus, 256

Video Display Generator (VDG), 268

Summary, 275

Questions, 275

14 LOOKING AHEAD ... 277

Further Study Suggestions, 278

A Look at Intel, 278

A Look at Motorola, 282

Appendix 1 NUMBERING SYSTEMS 309

Appendix 2 ASCII CODE CONVERSION TABLE 313

Appendix 3 INTEGRATED CIRCUITS 314

Appendix 4 STANDARD LOGIC SYMBOLS 322

Appendix 5 INSTRUCTION SETS 323

GLOSSARY 427

BIBLIOGRAPHY 443

INDEX 447

#### **ILLUSTRATIONS**

| Figure |                                                |      |

|--------|------------------------------------------------|------|

| Numbe  | er                                             | Page |

| 1-1    | Where microcomputers fit (applications)        | 4    |

| 1-2    | Intercommunication method                      | 8    |

| 1-3    | Common intercommunication configuration        | 8    |

| 1-4    | Common bus diagram                             | 9    |

| 2-1    | Evaluation of a binary statement               | 31   |

| 3-1    | Active gate signal diagrams                    | 37   |

| 3-2    | Debouncing circuits                            | 39   |

| 3-3    | Cross coupled inverter circuit for debouncing  |      |

|        | SPST switches                                  | 39   |

| 3-4    | RS flip-flops                                  | 41   |

| 3-5    | Gated RS flip-flop (RST) active high clock;    |      |

|        | Gated RS flip-flop (RST) active low clock      | 42   |

| 3-6    | Master-slave (2-phase clocking, negative edge) | 44   |

| 3-7    | (a) D-type flip-flop; (b) logic symbol         | 45   |

| 3-8    | Multiple-bit latch                             | 46   |

| 3-9    | Frequency divider (divide-by-2)                | 47   |

| 3-10   | Binary counter                                 | 47   |

| 3-11   | Serial input-parallel output shift register    | 48   |

| 3-12   | (a) Single line decoder; (b) two line decoder  | 49   |

| 3-13   | Logic diagram 7442                             | 50   |

| 3-14   | 4-to-16 cascade decoder                        | 51   |

| 3-15   | Data distribution (demultiplex)                | 52   |

| 3-16   | Data selection                                 | 53   |

| 3-17   | 16-bit data selector                           | 55   |

| 4-1    | Internal structure (general)                   | 61   |

|        |                                                |      |

| <b>kii</b><br>Illustrations | Figure<br>Numbe |                                                            | Page |

|-----------------------------|-----------------|------------------------------------------------------------|------|

|                             | 4-2             | Instruction/data memory arrangement                        | 63   |

|                             | 4-3             | Intel programming model                                    | 73   |

|                             | 4-4             | Motorola MC6800 programming model                          | 74   |

|                             | 5-1             | Common flow chart symbols                                  | 83   |

|                             | 5-2             | Algorithm for Add $x$ and $y$                              | 85   |

|                             | 5-3             | Algorithm for statement 1, $x + y = z$                     | 87   |

|                             | 5-4             | Algorithm for statement 3, add next two sequential entries | 87   |

|                             | 5-5             | Program development from conceptual to machine level       | 88   |

|                             | 5-6             | Jump if negative conceptual level                          | 90   |

|                             | 5-7             | Program for multiplication subroutine                      | 91   |

|                             | 6-1             | Device selection timing and control                        | 98   |

|                             | 6-2             | Bidirectional control                                      | 102  |

|                             | 6-3             | Address assignments                                        | 104  |

|                             | 6-4             | Typical on board decoding                                  | 105  |

|                             | 6-5             | Input/output memory mapping                                | 106  |

|                             | 7-1             | Simplified data port                                       | 111  |

|                             | 7-2             | Output port with timing                                    | 113  |

|                             | 7-3             | Handshake analogy                                          | 114  |

|                             | 7-4             | Handshake circuit                                          | 115  |

|                             | 7-5             | Flow diagram for handshake operation                       | 116  |

|                             | 7-6             | Input 3-state buffering                                    | 118  |

|                             | 7-7             | 8212 logic diagram and pin out                             | 119  |

|                             | 7-8             | Discrete hardware programmable port using 8212 devices     | 122  |

|                             | 7-9             | 8255 block diagram and pin out                             | 124  |

|                             | 7-10            | 8255 address assignments                                   | 126  |

|                             | 7-11            | PIA expanded block diagram                                 | 129  |

|                             | 8-1             | Random access memory (RAM)                                 | 136  |

|                             | 8-2             | MCM6810 RAM functional block diagram                       | 137  |

|                             | 8-3             | Read only memory (ROM)                                     | 138  |

|                             | 8-4             | MCM6830 ROM functional block diagram                       | 139  |

|                             | 8-5             | 2708 pin configuration                                     | 140  |

|                             | 8-6             | 2708 block diagram                                         | 140  |

|                             | 8-7             | Charge decay versus time                                   | 141  |

|                             | 8-8             | 2708 output buffer                                         | 142  |

|                             | 8-9             | Typical fuse cell                                          | 143  |

|                             | 8-10            | Blown and unblown fuses                                    | 144  |

| Number |                                                                                | Page |  |

|--------|--------------------------------------------------------------------------------|------|--|

| 8-11   | Polysilicon fuse cross section                                                 | 144  |  |

| 8-12   | PROM/ROM technology family tree                                                | 145  |  |

| 9-1    | 3-try keyboard entry loop                                                      | 158  |  |

| 9-2    | Use of breakpoints                                                             | 164  |  |

| 10-1   | 8080 CPU functional block diagram                                              | 171  |  |

| 10-2   | 8228 pin configuration, block diagram, appli-                                  |      |  |

|        | cation connection                                                              | 177  |  |

| 10-3   | 8080A CPU standard interface for 8228                                          | 170  |  |

| 10.4   | controller                                                                     | 178  |  |

| 10-4   | 8255 pin configuration, block diagram basic mode definitions and bus interface | 181  |  |

| 10-5   | Control word format bit definitions 8255                                       | 101  |  |

| 10-3   | basic operation                                                                | 182  |  |

| 10-6   | 8214 pin configuration, logic diagram                                          | 188  |  |

| 10-7   |                                                                                | 189  |  |

| 10-8   |                                                                                | 191  |  |

| 10-9   |                                                                                | 193  |  |

|        | Summary of transfer rate comparison                                            | 195  |  |

|        | Direct memory access input/output                                              | 197  |  |

| 10-12  | 8080A/8085 peripheral family                                                   | 198  |  |

| 11-1   | General circuit arrangement                                                    | 202  |  |

| 11-2   | I/O port system                                                                | 203  |  |

| 11-3   | Port control block diagram                                                     | 205  |  |

| 11-4   | Input timing                                                                   | 206  |  |

| 11-5   | Output timing                                                                  | 207  |  |

| 11-6   | Status word chart                                                              | 208  |  |

| 11-7   | 7-segment designations                                                         | 212  |  |

| 11-8   | Program flow diagram                                                           | 214  |  |

| 12-1   | MC6800 microprocessor and input/output lines                                   | 221  |  |

| 12-2   | MCM6810A RAM bus interface                                                     | 222  |  |

| 12-3   | MCM6830A ROM bus interface                                                     | 223  |  |

| 12-4   | MC6820 PIA bus interface                                                       | 224  |  |

| 12-5   | MC6850 ACIA bus interface                                                      | 224  |  |

| 12-6   | Bus interface timing                                                           | 231  |  |

| 12-7   | Microprocessor $\phi 1$ and $\phi 2$ clocks                                    | 232  |  |

| 12-8   | Test loads                                                                     | 233  |  |

| 12-9   | Typical system interconnections                                                | 234  |  |

| 12-10  | Typical bus delay times versus capacitive loading                              | 236  |  |

| 12-11  | Address modes                                                                  | 241  |  |

| xiv           | Figure |                                                                |      |

|---------------|--------|----------------------------------------------------------------|------|

| Illustrations | Number |                                                                | Page |

|               | 12-12  | Reset timing                                                   | 246  |

|               | 12-13  | Interrupt timing                                               | 248  |

|               |        | Wait instruction timing                                        | 249  |

|               | 12-15  | Halt and single instruction execution for                      | 251  |

|               |        | system debug                                                   | 251  |

|               |        | 3-state control timing                                         | 252  |

|               |        | Possible bus structure                                         | 258  |

|               |        | Expanded GPIA/MPU system                                       | 260  |

|               |        | Photo of HP59309A                                              | 261  |

|               |        | HP59309A block diagram                                         | 262  |

|               | 13-5   | Digital bus pin summary and digital bus con-                   | 265  |

|               |        | nector pin designs                                             | 266  |

|               | 13-6   | ,                                                              | 270  |

|               |        | Block diagram of use of the VDG in a TV game                   |      |

|               |        | Microphoto of S68047 VDG                                       | 272  |

|               |        | VDG block diagram                                              | 273  |

|               |        | Typical system                                                 | 274  |

|               |        | Microphoto of MC6802 chip                                      | 282  |

|               |        | Typical 2-component microcomputer                              | 283  |

|               |        | Expanded block diagram of MC6802                               | 284  |

|               |        | MC6803 block diagram                                           | 287  |

|               |        | MC6803 system configuration                                    | 288  |

|               | 14-6   | MC6801 single chip microcomputer block                         | 289  |

|               | 14 7   | diagram  Description configuration                             | 290  |

|               |        | Data communication configuration                               | 290  |

|               |        | Example of expanded parallel I/O capacity Multiple MC6801 MCUs | 291  |

|               |        | MC6809 internal structure                                      | 292  |

|               |        | MC6800 microcomputer family block diagram                      | 294  |

|               |        | MEK6800D2 evaluation kit                                       | 298  |

|               |        |                                                                | 299  |

|               |        | MEK6800D2 block diagram Memory map for MEK6800D2               | 301  |

|               |        | · ·                                                            | 302  |

|               |        | Photo of M68ADS1A development system M68ADS1A block diagram    | 303  |

|               |        | M68ADS1A memory map                                            | 304  |

|               |        | "Inside look" at the EXORciser                                 | 304  |

|               | 14-10  | mond for at the macketser                                      | 200  |

#### **TABLES**

| r                                              | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Where Microcomputers Fit (Cost)                | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Equivalent Values                              | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Binary and Decimal Fractional Numbers          | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Truth Table                                    | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Intel Instruction Set                          | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Motorola Instruction Set                       | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Intel and Motorola Algorithms                  | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 8255 Basic Operation                           | 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Control Word Format                            | 127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Motorola Partial Assembly Listing              | 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Intel Partial Assembly Listing                 | 151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Manual Assembly Example                        | 153                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Typical Nest of Two Loops                      | 157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Intel-Motorola Single Precision Equivalents    | 159                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Intel 8080 Basic Arithmetic Operations Example | 160                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Multiple Precision                             | 161                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 8080 Restart Vector Locations                  | 192                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Timetable Memory Map (Octal/Hexadecimal)       | 211                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Port 6 Code (Fourth Digit and AM/PM). Ports    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3, 4 and 5 Codes (Digits 1, 2, and 3)          | 212                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Prestored Memory Table (Octal/Hexadecimal)     | 213                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Timetable Addressing Record                    | 215                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Memory Table of Prestored Times and Time on    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Clock (Octal/Hexadecimal)                      | 216                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                | Where Microcomputers Fit (Cost) Equivalent Values Binary and Decimal Fractional Numbers Truth Table Intel Instruction Set Motorola Instruction Set Intel and Motorola Algorithms 8255 Basic Operation Control Word Format Motorola Partial Assembly Listing Intel Partial Assembly Listing Manual Assembly Example Typical Nest of Two Loops Intel-Motorola Single Precision Equivalents Intel 8080 Basic Arithmetic Operations Example Multiple Precision 8080 Restart Vector Locations Timetable Memory Map (Octal/Hexadecimal) Port 6 Code (Fourth Digit and AM/PM). Ports 3, 4 and 5 Codes (Digits 1, 2, and 3) Prestored Memory Table (Octal/Hexadecimal) Timetable Addressing Record |

| xvi    | Table |                                                             |     |

|--------|-------|-------------------------------------------------------------|-----|

| Tables | Numbe | Number                                                      |     |

|        | 11-6  | Chart Construction                                          | 216 |

|        | 11-7  | Complete Program                                            | 217 |

|        | 12-1  | PIA Internal Addressing                                     | 227 |

|        | 12-2  | ACIA Internal Addressing                                    | 227 |

|        | 12-3  | Static Characteristics                                      | 229 |

|        | 12-4  | Dynamic Characteristics                                     | 230 |

|        | 12-5  | Maximum Ratings                                             | 233 |

|        | 12-6  | Address Lines for System of Fig. 12-9                       | 237 |

|        | 12-7  | Microprocessor Instruction Set—Alphabetic<br>Sequence       | 239 |

|        | 12-8  | Instruction Addressing Modes and Associated Execution Times | 240 |

|        | 14-1  | MC6803 New Instructions                                     | 286 |

### INTRODUCTION TO THE MICROPROCESSOR

Address A character or group of characters that identifies a register, a particular part of storage or some other data source or destination.

Glossary

- Arithmetic logic unit (ALU) The central processing unit chip logic which actually executes the operations requested by an input command

- Assembly language In microprocessor programs, a series of source statements using mnemonic symbols that assist in the definition of the instruction and are then translated into machine understandable object code such as binary 0s and 1s.

- Boolean algebra A mathematical system of logic which deals with classes, proposition, on-off circuit elements; associated by operators as AND, OR, NOT, EXCEPT, IF. . . . THEN—which permits computations and demonstrations in any other mathematical system.

- **Bus** One or more conductors used as a path over which information is transmitted.

- Central processing unit (CPU) Performs control, input/output, arithmetic and logical operations by executing instructions obtained from memory sources.

- Chip A single device composed of transistors, diodes and other components interconnected by various chemical processes and usually cut from a silicon wafer.

- Control unit That section which directs the sequence of operations, interrupts coded instructions and sends the proper signals to other circuits to carry out instructions.

- **Development system** A system provided by most manufacturers which allows the designer to accomplish prototype operations utilizing both hardware and software techniques.

1