# ULSI DEVICES

Edited by C. Y. Chang S. M. Sze

# **ULSI DEVICES**

Edited by

C. Y. Chang National Chiao Tung University

S. M. Sze National Chiao Tung University and National Nano Device Laboratories

A WILEY-INTERSCIENCE PUBLICATION

JOHN WILEY & SONS, INC.

New York • Chichester • Weinheim • Brisbane • Singapore • Toronto

This book is printed on acid-free paper. <sup>™</sup>

Copyright © 2000 by John Wiley & Sons. All rights reserved.

Published simultaneously in Canada.

No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning or otherwise, except as permitted under Sections 107 or 108 of the 1976 United States Copyright Act, without either the prior written permission of the Publisher, or authorization through payment of the appropriate per-copy fee to the Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923, (508) 750-8400, fax (508) 750-4744. Requests to the Publisher for permission should be addressed to the Permissions Department, John Wiley & Sons, Inc., 605 Third Avenue, New York, NY 10158-0012, (212) 850-6011, fax (212) 850-6008, E-Mail: PERMREQ @ WILEY.COM.

For ordering and customer service, call 1-800-CALL-WILEY.

## Library of Congress Cataloging-in-Publication Data:

ULSI devices / edited by C. Y. Chang, S. M. Sze.

p.

"A Wiley-Interscience publication."

ISBN 0-471-24067-2 (alk. paper)

1. Integrated circuits—Ultra large scale integration.

2. Semiconductors. I. Chang, C. Y. II. Sze, S. M., 1936-TK7874.76.U47 2000

621.39'5-dc21

99-29979

Printed in the United States of America.

10 9 8 7 6 5 4 3 2 1

### CONTRIBUTORS

- Sanjay K. Banerjee, The University of Texas at Austin, Austin, Texas, USA

- John Caywood, SubMicron Circuits, Inc., San Jose, California, USA

- C. Y. Chang, National Chiao Tung University, Hsinchu, Taiwan, ROC

- Mau-Chung Frank Chang, University of California at Los Angeles, Los Angeles, California, USA

- I. C. Chen, Worldwide Semiconductor Manufacturing Corp., Hsinchu, Taiwan, ROC

- Jean-Pierre Colinge, Department of Electrical and Computer Engineering, University of California, Davis, California, USA

- Gary Derbenwich, Celis Semiconductor Corp., Colorado Springs, Colorado, USA

- Brian Doyle, Intel Corporation, Santa Clara, California, USA

- Erich Kasper, Institute of Semiconductor Engineering, University of Stuttgart, Stuttgart, Germany

- W. Liu, Texas Instruments, Inc., Dallas, Texas, USA

- David R. Pehlke, Rockwell Science Center, Thousand Oaks, California, USA; now at Ericsson, Research Triangle Park, North Carolina, USA

- Marcel J. M. Pelgrom, Philips Research Laboratories, Eindhoven, The Netherlands

- Hisashi (Sam) Shichijo, Texas Instruments, Inc., Dallas, Texas, USA

- Ben G. Streetman, The University of Texas at Austin, Austin, Texas, USA

- Simon M. Sze, National Chiao Tung University and National Nano Device Laboratories, Hsinchu, Taiwan, ROC

- **Hon-Sum Philip Wong**, IBM Thomas J. Watson Research Center, Yorktown Heights, New York, USA

Beginning in 1990, the semiconductor industry has entered the ultra-large-scale integration (ULSI) era with 10 million or more devices per integrated circuit (IC) chip. We expect that this trend toward higher integration levels will continue at least to year 2020. By then, the most advanced IC chips will contain over 1 trillion (10<sup>12</sup>) devices.

The most important ULSI device is, of course, the metal-oxide-semiconductor field-effect transistor (MOSFET), because of its advantages in device miniaturization, low power dissipation, and high yield compared to all other semiconductor devices. The MOSFET also serves as a basic component for many key device building blocks, including the complementary metal oxide semiconductor (CMOS), the dynamic random access memory (DRAM), and the static random access memory (SRAM). Another important ULSI device is the nonvolatile semiconductor memory (NVSM), which has the most desirable attributes for information storage compared to all other semiconductor memories. The third important ULSI device is the bipolar transistor. Although it is nearly completely replaced by the MOSFET in digital circuits, the bipolar transistor is often the preferred device for analog and mixed analog and digital circuits.

ULSI Devices gives a comprehensive and in-depth coverage of the physics and operational principles of the aforementioned devices and their building blocks. In addition, the book covers device simulation, reliability, digital and analog circuit building blocks, low-power and low-voltage operations, as well as system-on-chip for ULSI applications.

Each chapter starts with an introduction that provides a general discussion of a specific device, a device building block or a circuit building block. Subsequent sections present the physics and operational characteristics of these components, the evolution of device structures, and the ultimate limitation on device or circuit performances. The problem set at the ends of each chapter are an integral part of the development of the topic.

The book is intended as a textbook for senior undergraduate or first-year graduate students in applied physics and electrical and electronics engineering; it assumes that the reader has already acquired an introductory understanding of the physics of semiconductor devices. The book can also serve as a reference for those actively involved in IC design and process development.

In the course of writing this text, many people have assisted us and offered their support. First, we express our appreciation to the management of our academic and industrial institutions, without whose help this book could not have been written. We

have benefited from suggestions made by our reviewers: Dr. S. Cristoloveanu of ENSERG-LPCS, Prof. S. Datta of Purdue University, Prof. L. Der of the University of California, Los Angeles, Prof. K. Hess of the University of Illinois, Prof. C. M. Hu of the University of California, Berkeley, Dr. R. Koch of Mixed Signal Competence Center, Dr. C. C. Lu of Etron Technology, Dr. K. Mistry of Digital Equipment Corporation, Dr. K. K. Ng of Bell Laboratories, Lucent Technologies, Prof. Y. Omura of Kansai University, Dr. B. Prince of Memory Strategies International, Dr. F. J. Shone of Macronix International Company, Dr. J. Slotboom of Philips Research Laboratories, Prof. Y. Tsividis of Columbia University, and Dr. H. J. Wann of IBM T. J. Watson Research Center.

We are further indebted to Mr. N. Erdos for technical editing of the entire manuscript. We also thank Ms. Y. C. Wang, Ms. M. H. Tai and Ms. W. L. Chen for handling the correspondence with our contributors and reviewers, and Mrs. T. W. Sze for preparing the Appendixes.

We wish to thank the Ministry of Education, ROC (Republic of China), the National Science Council, ROC, and the Spring Foundation of the National Chiao Tung University for their financial support. One of the editors (S. M. Sze) especially thanks the United Microelectronics Corporation (UMC), Taiwan, ROC, for the UMC Chair Professorship grant that provided the environment to work on this book.

Hsinchu, Taiwan January 2000 C. Y. CHANG S. M. SZE

# CONTENTS

| CO | ONTRIBUTORS                                                                                                                                                                             | ix                      |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| PR | REFACE                                                                                                                                                                                  | xi                      |

| 1. | . Introduction C. Y. Chang and S. M. Sze                                                                                                                                                | 1                       |

|    | <ul> <li>1.1 Semiconductor Industry</li> <li>1.2 Milestones in ULSI-Related Devices</li> <li>1.3 Technology Trends</li> <li>1.4 Organization of the Book</li> <li>References</li> </ul> | 1<br>3<br>9<br>13<br>15 |

| PA | ART I DEVICE FUNDAMENTALS                                                                                                                                                               |                         |

| 2. | . Bipolar Transistor Fundamentals E. Kasper                                                                                                                                             | 19                      |

|    | 2.1 Introduction                                                                                                                                                                        | 19                      |

|    | 2.2 Structure and Operating Regimes                                                                                                                                                     | 20                      |

|    | 2.3 The Inner-Box-Shaped Transistor                                                                                                                                                     | 25                      |

|    | 2.4 Self-Adjusted Transistor Structures                                                                                                                                                 | 51                      |

|    | 2.5 Heterojunction Bipolar Transistor                                                                                                                                                   | 60                      |

|    | 2.6 Summary and Future Trends                                                                                                                                                           | 66                      |

|    | References                                                                                                                                                                              | 67                      |

|    | Problems                                                                                                                                                                                | 71                      |

| 3. | . MOSFET Fundamentals P. Wong                                                                                                                                                           | 73                      |

|    | 3.1 Introduction                                                                                                                                                                        | 73                      |

|    | 3.2 MOSFET Device Physics: First-Order Mo                                                                                                                                               | odels 74                |

|    | 3.3 Device Scaling                                                                                                                                                                      | 84                      |

|    | 3.4 Short-Channel Effects                                                                                                                                                               | 88                      |

|    | 3.5 Transport Properties                                                                                                                                                                | 102                     |

|    | 3.6 Parasitic Effects                                                                                                                                                                   | 110                     |

|    | 3.7 Evolution of MOSFET Device Structures                                                                                                                                               | 130                     |

| vi | CONTENTS |

|----|----------|

|----|----------|

| 3.8 | Summary and Future Trends                                      | 135 |

|-----|----------------------------------------------------------------|-----|

| Re  | ferences                                                       | 139 |

| Pro | bblems                                                         | 147 |

|     | evice Miniaturization and Simulation Banerjee and B. Streetman | 149 |

| 4.1 | Introduction                                                   | 149 |

| 4.2 | Band Structure                                                 | 150 |

| 4.3 | Semiclassical Electron Dynamics                                | 160 |

| 4.4 | Equilibrium Statistics                                         | 163 |

| 4.5 | e ,                                                            | 170 |

| 4.6 |                                                                | 182 |

| 4.7 |                                                                | 185 |

| 4.8 | ,                                                              | 211 |

|     | ferences                                                       | 216 |

| Pro | bblems                                                         | 218 |

|     | CE STRUCTURES                                                  |     |

|     | OI and Three-Dimensional Structures P. Colinge                 | 221 |

| 5.1 | Introduction                                                   | 221 |

|     | SOI Substrates                                                 | 222 |

|     | The SOI MOSFET                                                 | 230 |

|     | 3D and Novel SOI Devices                                       | 239 |

|     | SOI Circuits                                                   | 254 |

| 5.6 | ,                                                              | 263 |

|     | ferences                                                       | 263 |

| Pro | blems                                                          | 272 |

|     | e Hot-Carrier Effect<br>Doyle                                  | 275 |

| 6.1 | Introduction                                                   | 275 |

| 6.2 | <i>D</i>                                                       | 278 |

| 6.3 | Gate Voltage Dependence of Stress                              | 281 |

| 6.4 | Hot-Carrier Lifetime Estimation: AC and DC                     | 294 |

| 6.5 | Hot-Carrier Measurements                                       | 302 |

| 6.6 | Structure Dependence                                           | 310 |

| 6.7 | Process Dependence                                             | 314 |

| 6.8 | Summary and Future Trends                                      | 322 |

|     | erences                                                        | 324 |

| Pro | blems                                                          | 332 |

|    |                                                         | CONTENTS | vii |

|----|---------------------------------------------------------|----------|-----|

| 7. | DRAM and SRAM S. Shichijo                               |          | 333 |

|    | 7.1 Introduction                                        |          | 333 |

|    | 7.2 DRAM Cell Structures                                |          | 333 |

|    | 7.3 DRAM Operation Principle                            |          | 340 |

|    | 7.4 DRAM Circuits                                       |          | 346 |

|    | 7.5 SRAM Memory Cell Structure                          |          | 358 |

|    | 7.6 SRAM Operation Principle                            |          | 362 |

|    | 7.7 SRAM Circuits                                       |          | 367 |

|    | 7.8 Summary and Future Trends                           |          | 371 |

|    | References                                              |          | 372 |

|    | Problems                                                |          | 374 |

| 8. | Nonvolatile Memory                                      |          | 377 |

|    | J. Caywood and G. Derbenwich                            |          |     |

|    | 8.1 Introduction                                        |          | 377 |

|    | 8.2 Floating-Gate Memory                                |          | 378 |

|    | 8.3 Floating-Gate Memory Arrays                         |          | 393 |

|    | 8.4 Reliability of Floating-Gate Memories               |          | 421 |

|    | 8.5 Future Trends and Summary of Floating-Gate Memory   |          | 426 |

|    | 8.6 Silicon Nitride Memory                              |          | 430 |

|    | 8.7 Ferroelectric Memory                                |          | 448 |

|    | References                                              |          | 463 |

|    | Problems                                                |          | 470 |

| SY | RT III CIRCUIT BUILDING BLOCKS AND STEM-IN-CHIP CONCEPT |          |     |

| 9. | CMOS Digital and Analog Building Block Circuits for     |          |     |

|    | Mixed-Signal Applications                               |          | 477 |

|    | D. Pehlke and MC. F. Chang                              |          |     |

|    | 9.1 Introduction                                        |          | 477 |

|    | 9.2 CMOS for Digital Applications                       |          | 479 |

|    | 9.3 CMOS Technology for Analog and RF Applications      |          | 492 |

|    | 9.4 CMOS Low-Noise Amplifiers                           |          | 493 |

|    | 9.5 Mixers and Frequency Translation                    |          | 508 |

|    | 9.6 CMOS Voltage-Controlled Oscillators                 |          | 520 |

|    | 9.7 CMOS Power Amplifiers                               |          | 535 |

|    | 9.8 Summary and Future Trends                           |          | 540 |

|    | References                                              |          | 541 |

|    | Problems                                                |          | 543 |

# viii CONTENTS

| 10. |              | Speed or Low-Voltage, Low-Power Operations                    | 547 |

|-----|--------------|---------------------------------------------------------------|-----|

|     | <i>I. C.</i> | Chen and W. Liu                                               |     |

|     | 10.1         | Introduction                                                  | 547 |

|     | 10.2         | High-Speed Considerations for Digital Applications            | 548 |

|     | 10.3         | Low Voltage/Low Power Considerations for Digital Applications | 581 |

|     | 10.4         | Cutoff and Maximum Oscillation Frequencies                    | 585 |

|     | 10.5         | Large-Signal Power and Efficiency                             | 597 |

|     | 10.6         | Noise Figure                                                  | 607 |

|     | 10.7         | Summary and Future Trends                                     | 616 |

|     | Refer        | ences                                                         | 618 |

|     | Proble       | ems                                                           | 627 |

| 11. | Syste        | m-on-Chip Concepts                                            | 631 |

|     |              | lgrom                                                         |     |

|     | 11.1         | Introduction                                                  | 631 |

|     |              | Embedded Modules on an IC                                     | 633 |

|     |              | Technology for Mixed-Signal Circuits                          | 639 |

|     | 11.4         | Technology Limits                                             | 645 |

|     | 11.5         | Analog Interfaces                                             | 651 |

|     | 11.6         | Integration of Blocks                                         | 664 |

|     | 11.7         | System-on-Chip Concept                                        | 676 |

|     | 11.8         | Summary and Future Trends                                     | 679 |

|     | Refer        |                                                               | 681 |

|     | Proble       | ems                                                           | 683 |

| Ap  | pendix       | A. List of Symbols                                            | 685 |

| Ap  | pendix       | B. International System of Units (SI Units)                   | 687 |

| Apj | pendix       | C. Unit Prefixes                                              | 689 |

| Ap  | pendix       | D. Greek Alphabet                                             | 691 |

| Apj | pendix       | E. Physical Constants                                         | 693 |

| App | pendix       | F. Properties of Si at 300 K                                  | 695 |

| INI | DEX          |                                                               | 697 |

# Introduction

C. Y. CHANG

National Chiao Tung University Hsinchu, Taiwan, ROC

S. M. SZE

National Chiao Tung University National Nano Device Laboratories Hsinchu, Taiwan, ROC

### 1.1 SEMICONDUCTOR INDUSTRY

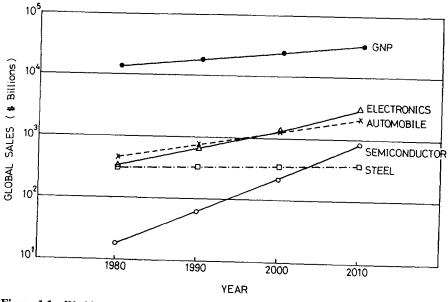

The electronic industry is the largest industry in the world with global sales over 1 trillion dollars. <sup>1-3</sup> The foundation of the electronic industry is the semiconductor industry. Figure 1.1 shows the sales volumes of these two industries from 1980 to 1998 and projects the sales to year 2010. Also shown are the world gross national product (GNP), and the sales volumes of automobile and steel industries.<sup>2</sup>

We note that the electronic industry has surpassed the automobile industry in 1998. If the current trends continue, in year 2010 the sales volume of the electronic industry will reach \$2.7 trillion and will constitute about 10% of the world GNP. The semiconductor industry will grow at an even higher rate to surpass the steel industry in the early twenty-first century and to constitute 30% of the electronic industry in 2010 (i.e., about \$750 billion).

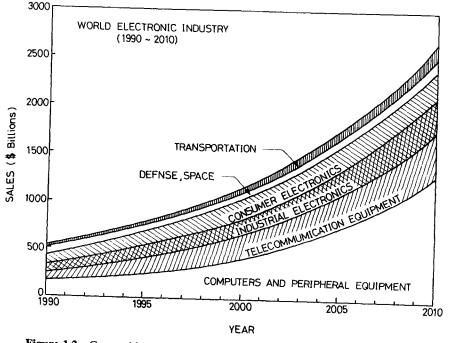

Figure 1.2 shows the composition of the world electronic industry. The largest segment is the computers and peripheral equipment (about 35% in 1998), followed by the telecommunication equipment ( $\sim$ 25%), industrial electronics ( $\sim$ 15%), consumer electronics ( $\sim$ 15%), defense and space electronics ( $\sim$ 5%), and transportation ( $\sim$ 5%). By the year 2010, the composition will remain essentially the same; however, the computers and peripheral equipment segment will expand more rapidly to capture about 45% of the total market.

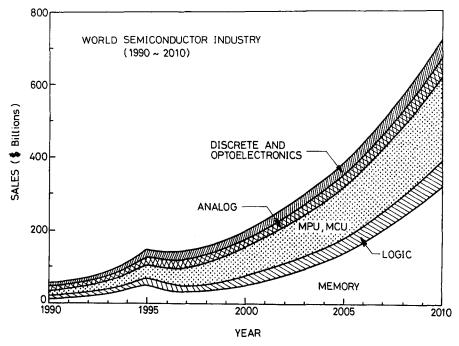

The market for the world semiconductor industry<sup>2,3</sup> is shown in Figure 1.3. The largest segment is the microprocessor and microcontroller units (about

ULSI Devices, Edited by C. Y. Chang and S. M. Sze ISBN 0-471-24067-2 Copyright © 2000 by John Wiley & Sons, Inc.

Figure 1.1 World gross national product and sales volumes of the electronics, automobile, semiconductor, and steel industries from 1980 to 1998 and projected to 2010. (After Refs. 1-3.)

Figure 1.2 Composition of the world electronic industry. (After Refs. 2 and 3.)

Figure 1.3 Composition of the world semiconductor industry. (After Refs. 2 and 3.)

35% in 1998), followed by memory ( $\sim$ 25%), analog ( $\sim$ 15%), discrete and optoelectronic ( $\sim$ 15%), and logic ( $\sim$ 10%). By the year 2010, memory may become the dominant segment and most of the memories will be integrated with microprocessors (and other logic circuits) to form systems-on-a-chip.

# 1.2 MILESTONES IN ULSI-RELATED DEVICES

The ULSI device is almost synonymous with the silicon MOSFET. This is mainly due to the MOSFET's intrinsic characteristics, which are uniquely suitable for highly complex ICs. In addition, many important device building blocks for ULSI such as CMOS, DRAM, and SRAM are also derived from MOSFET.

However, there are other important devices that can either enhance the MOSFET performance (e.g., bipolar transistor for BiCOMS) or have special features not obtainable from MOSFET (e.g., nonvolatile semiconductor memory for long-term information storage).

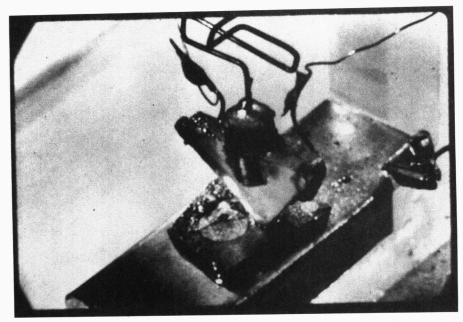

Table 1.1 lists some major ULSI related devices and device building blocks in chronological order. In 1947, the point-contact transistor was invented by Bardeen and Brattain.<sup>4</sup> This was followed by Shockley's classic paper on bipolar transistor.<sup>5</sup> Figure 1.4 shows the first transistor. The two point contacts at the bottom of the triangular quartz crystal were made from two stripes of gold foil

Figure 1.4 The first transistor. (After Bardeen and Brattain, Ref. 4.)

separated by about 50 µm and pressed onto the germanium surface. With one gold contact forward-biased and the other reverse-biased, the transistor action was observed. The invention of the bipolar transistor had an unprecedented impact on the electronics industry, and 1947 marked the beginning of the modern electronics era. In 1957, Kroemer proposed the heterojunction bipolar transistor (HBT) to improve the emitter efficiency; this device is potentially one of the fastest semiconductor devices. At present, the bipolar transistor has been replaced by MOSFET in a digital circuit. However, the bipolar transistor and

TABLE 1.1 Milestones of ULSI-Related Devices

| Device or Device Building Block  | Inventor(s) / Author(s)                                                                                                                                                                | Institution                                                                                                                                                                                                                                                                                                                        |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bipolar transistor               | Bardeen, Brattain, Shockley                                                                                                                                                            | Bell Labs                                                                                                                                                                                                                                                                                                                          |

|                                  | Kroemer                                                                                                                                                                                | RCA Labs                                                                                                                                                                                                                                                                                                                           |

| -                                | Kilby                                                                                                                                                                                  | TI                                                                                                                                                                                                                                                                                                                                 |

| Monoliohic IC                    | Noyce                                                                                                                                                                                  | Fairchild                                                                                                                                                                                                                                                                                                                          |

| Enhancement-mode MOSFET          | Kahng, Atalla                                                                                                                                                                          | Bell Labs                                                                                                                                                                                                                                                                                                                          |

| CMOS                             | Wanlass, Sah                                                                                                                                                                           | Fairchild                                                                                                                                                                                                                                                                                                                          |

|                                  | Kahng, Sze                                                                                                                                                                             | Bell Labs                                                                                                                                                                                                                                                                                                                          |

|                                  | Dennard                                                                                                                                                                                | IBM                                                                                                                                                                                                                                                                                                                                |

|                                  | Hoff et al.                                                                                                                                                                            | Intel                                                                                                                                                                                                                                                                                                                              |

| Room-temperature single-electron | Yano et al.                                                                                                                                                                            | Hitachi                                                                                                                                                                                                                                                                                                                            |

|                                  | Bipolar transistor Heterojunction bipolar transistor Integrated circuit Monoliohic IC Enhancement-mode MOSFET CMOS Nonvolatile semiconductor memory One-transistor DRAM Microprocessor | Bipolar transistor Heterojunction bipolar transistor Integrated circuit Monoliohic IC Enhancement-mode MOSFET CMOS Nonvolatile semiconductor memory One-transistor DRAM Microprocessor Room-temperature single-electron  Bardeen, Brattain, Shockley Kroemer Kilby Noyce Kahng, Atalla Wanlass, Sah Kahng, Sze Dennard Hoff et al. |

Figure 1.5 The first integrated circuit (After Kilby, Ref. 7.)

HBT are useful for analog and mixed analog and digital circuits. They can be combined with CMOS to form BiCMOS (bipolar CMOS) for high-speed/low-power applications.

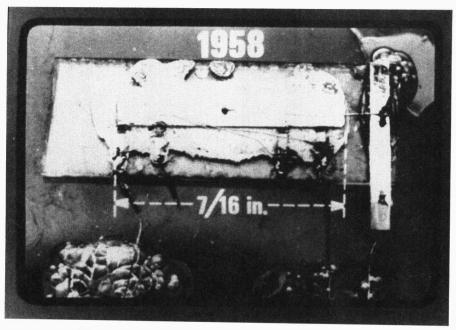

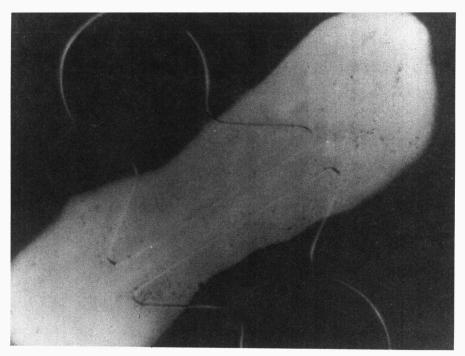

In 1958, the first rudimentary integrated circuit (IC) was made by Kilby. It contained one bipolar transistor, three resistors, and one capacitor, all made in germanium and connected by wire bonding (see Fig. 1.5). In 1959, Noyce proposed the first monolithic IC by fabricating all devices in a single semiconductor substrate using oxide isolation and aluminum metallization (see Fig. 1.6). These inventions paved the way for the ever-expanding microelectronic industry.

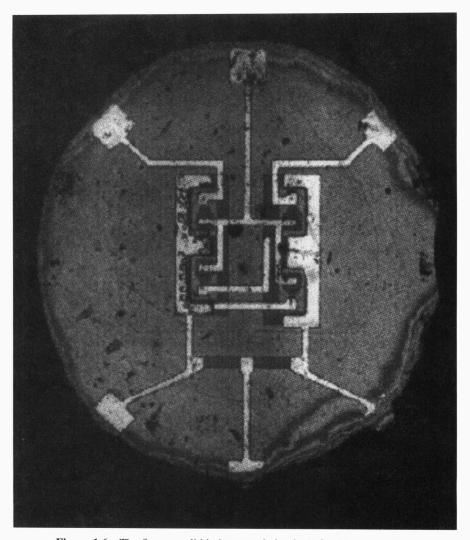

In 1960, Kahng and Atalla proposed and fabricated the first enhancement-mode MOSFET using a thermally oxidized silicon structure. Figure 1.7 shows the device, which has a channel length of 25 µm and a gate oxide thickness of about 1000 Å. The two keyholes are the source and drain contacts, and the top elongated area is the aluminum gate evaporated through a metal mask. Although present-day MOSFETs have been scaled down to deep submicrometer regime, the choice of silicon and thermally grown silicon dioxide used in the first enhancement-made MOSFET remains the most important combination. The MOSFET and its related ICs now constitute over 90% of the semiconductor device market, and it is the most important device for ULSI applications.

As the complexity of the IC increases, we have moved from NMOS to the CMOS (complementary MOSFET) technology, which employs both NMOS and

Figure 1.6 The first monolithic integrated circuit. (After Noyce, Ref. 8.)

PMOS to form the logic elements. The CMOS concept<sup>10</sup> was proposed by Wanlass and Sah in 1963. The advantage of CMOS technology is that the logic elements draw significant current only during the transition from one state to another and draw very little current between transitions, allowing power consumption to be minimized. The CMOS technology is the dominant technology for ULSI.

In 1967, an important memory device was invented by Kahng and Sze. <sup>11</sup> This is the nonvolatile semiconductor memory (NVSM), which can retain its stored

Figure 1.7 The first enhancement-mode MOSFET. (After Kahng and Atalla, Ref. 9.)

information when the power supply is switched off. A schematic diagram of the first NVSM is shown in Figure 1.8a. Although it looks like a conventional MOSFET, the major difference is the addition of the floating gate, in which semipermanent charge storage is possible. Because of its attributes of non-volatility, high density, low power consumption, and electrical rewritability, NVSM has become the dominant memory for portable electronic systems such as the cellular phone and the notebook computer.

A limiting case of the floating-gate memory is the single-electron memory cell (SEMC) shown in Figure 1.8b. By reducing the length of the floating gate to ultra small dimensions (e.g., 10 nm), we obtain the SEMC. Because of its small size the capacitance is also very small ( $\sim 10^{-18}$  F, which is about a million times smaller than that of the device in Fig. 1.8a). At this dimension, when an electron tunnels into the floating gate, the tunneling of another electron is blocked due to quantum effect. The SEMC is an ultimate floating-gate memory cell, since we need at least one electron for information storage. The operation of a SEMC at room temperature was first demonstrated by Yano<sup>12</sup> et al. in 1994 (last item in Table 1.1). The SEMC can serve as a building block for multiterabit NVSM.

The one-transistor DRAM, which is a combination of a MOSFET and a charge-storage MOS capacitor, was proposed in 1967 by Dennard. A circuit representation and a cross-sectional view of the memory cell are shown in Figure