## INTRODUCTION TO COMPUTER ARCHITECTURE AND ORGANIZATION

HAROLD LORIN

# INTRODUCTION TO COMPUTER ARCHITECTURE AND ORGANIZATION

HAROLD LORIN

IBM Systems Research Institute, New York

A Wiley-Interscience Publication

JOHN WILEY & SONS

New York · Chichester · Brisbane · Toronto · Singapore

Copyright © 1982 by John Wiley & Sons Inc

All rights reserved. Published simultaneously in Canada

Reproduction or translation of any part of the work beyond that permitted by Section 197 or 108 of the 1976 United States Copyright Act without the permission of the copyright owner is unlawful. Requests for permission or further information should be addressed to the Permissions Department. John Wiley & Sons. Inc.

### Library of Congress Cataloging in Publication Data.

Lorin, Harold.

Introduction to computer architecture and organization.

"A Wiley-Interscience publication." Includes bibliographies and index.

1. Computer architecture. 1. Title.

QA76.9.A731.67 1982 621.3819'52 82-8640 ISBN 0-471-86679-2 AACR2

Printed in the United States of America

10 9 8 7 6 5 4 3 2 1

## **PREFACE**

This book is an introduction to computers for people who know something about computing. It is aimed at the population of computer professionals and paraprofessionals, casual users, and all others who have some view of computing but know nothing about the logical and organizational nature of a computing device.

As the computer field has matured, it, like all advancing areas of knowledge, has fragmented into a number of specialties. There are a number of very competent computer professionals who know many aspects of software specification, data base design, large application development technique, and so on, but do not know much about the instrument on which their miracles are performed. There is also a large population of computing professionals who know about the technology of computer manufacture or packaging digital technology but have never formed a complete image of the nature of the device they manufacture or whose subassemblies they design. Finally, there is the growing population of casual users whose curiosity has been piqued by their contact with computers and who would like to know more about them.

This book is for all these people. It assumes that the reader has some knowledge of languages like BASIC, FORTRAN, and COBOL, and, starting with known concepts, guides the reader through various stages of computer hardware architecture and organization. It is my opinion, however, that the slightest familiarity with the general ideas of higher-level languages is a sufficient starting point.

This book was developed over a period of years as a result of my interaction with both graduate and professional students. A number of these students reviewed the manuscript, and the extent of coverage and many specific details are the result of their comments and class interaction.

What I try to do here is discuss ideas of architecture and organization generally to provide an overview of several immortal concepts. While specific architectures and machine organizations are mentioned in the book, for example, the IBM S/370, IBM Series/1, IBM 8100, Sperry Rand UNIVAC 1100, Cray Research CRAY-1, Digital Equipment Corporation VAX-11, Data General NOVA, INTEL 8080, and INTEL 8086, the book is not intended to describe specific machines but to use them as examples of architectural and organizational concepts. The danger in using specific examples is that the concepts they embody seem to age with the machines though the concepts are in fact ageless.

There are two great challenges in undertaking a book of this type. One, of course, is content. Naturally I hope that the content is well chosen, the omissions not disqualifying, and the simplifications appropriate. Aside from content, the greatest challenge is sequence. Topics are so interrelated that it is difficult to discuss many points without anticipating later ones. Where necessary, brief characterizing introductions are offered in one area to support discussion in another. This leads to some repetition, but the idea is to give more and more detail each time a topic is discussed. The sequence of chapters was discovered dynamically in class; it has been changed many times, and I am now confident that the conceptual flow of the book minimizes the temptation for readers to look ahead.

HAROLD LORIN

New York September 1982

## **CONTENTS**

|    | PAI                                                | RT ONE ARCHITECTURE                                                                                                                                                                                                                                                                                                    |    |  |

|----|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| 1. | Arc                                                | Architecture, Organization, and Implementation                                                                                                                                                                                                                                                                         |    |  |

|    | 1.<br>2.                                           | Architecture, 3 Elements of an Architecture, 5                                                                                                                                                                                                                                                                         |    |  |

|    |                                                    | <ul> <li>2.1. Mode of Data Representation, 5</li> <li>2.2. Size of the Basic Data Structure, 5</li> <li>2.3. Addressing Conventions, 6</li> <li>2.4. Register Model, 6</li> <li>2.5. Instruction Set, 7</li> <li>2.6. Interrupt Mechanism, 9</li> <li>2.7. Control States, 9</li> <li>2.8. Input/Output, 10</li> </ul> |    |  |

|    | 3.<br>4.<br>5.<br>6.<br>7.                         | Implementation, 11 Architecture versus Organization, 11                                                                                                                                                                                                                                                                |    |  |

| 2. | Con                                                | npilation                                                                                                                                                                                                                                                                                                              | 17 |  |

|    | 1.<br>2.<br>3.<br>4.<br>5.<br>6.<br>7.<br>8.<br>9. |                                                                                                                                                                                                                                                                                                                        |    |  |

| 3. | Dat                                                       | a Coding and Reference                                                                                                                                                                                                                                                                             | 27 |

|----|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | 1.<br>2.                                                  | Data Declaration, 27 Data Modes and Representation, 27                                                                                                                                                                                                                                             |    |

|    |                                                           | <ul><li>2.1. Pure Binary Characteristics, 29</li><li>2.2. Binary-Coding Schemes, 30</li><li>2.3. Floating Point, 30</li></ul>                                                                                                                                                                      |    |

|    | 3.                                                        | Addressable Units, 31                                                                                                                                                                                                                                                                              |    |

|    |                                                           | <ul><li>3.1. Basic Word Size, 32</li><li>3.2. Address Definition, 33</li><li>3.3. Word Sizes and Processor Type, 34</li></ul>                                                                                                                                                                      |    |

|    | 4.<br>5.                                                  | Nonscalar Representation, 34<br>Self-Describing Data, 35                                                                                                                                                                                                                                           |    |

| 4. | Reg                                                       | ister Organization                                                                                                                                                                                                                                                                                 | 37 |

|    | 1.<br>2.<br>3.<br>4.<br>5.<br>6.<br>7.                    | Registers, 37 Register and Register Model Characteristics, 38 Register Operand Referencing, 39 Operations on Registers, 41 Multiple Register Sets, 42 Operand Stacks, 43 Stacks and Compilation, 49 Some Example Operand Register Models, 52                                                       |    |

|    |                                                           | 8.1. CRAY-1, 52<br>8.2. UNIVAC 1100, 53<br>8.3. VAX-11, 54                                                                                                                                                                                                                                         |    |

|    | 9.<br>10.<br>11.                                          | Software Register Conventions, 54 Basic Control Registers, 54 Placement of Control Information, 55                                                                                                                                                                                                 |    |

| 5. | Mei                                                       | mory Addressing Conventions                                                                                                                                                                                                                                                                        | 57 |

|    | 1.<br>2.<br>3.<br>4.<br>5.<br>6.<br>7.<br>8.<br>9.<br>10. | Addressing Conventions in Instructions, 57 Fundamental Issue, 57 Address Size Compression, 58 Fewer Addresses, 60 Mixed Addressing Forms, 61 Registers in Address Formation, 62 Indexing, 63 Page. Base, and Segment Addressing, 66 Segmentation, 68 Indirect Addressing, 69 Memory Protection, 70 |    |

|    |                                                           |                                                                                                                                                                                                                                                                                                    |    |

Contents ix

|    |                                        | <ul><li>11.1. Protection Keys, 71</li><li>11.2. Protection Rings, 71</li></ul>                                                                                                                                                             |     |  |

|----|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

| 6. | Inst                                   | ruction Sets                                                                                                                                                                                                                               | 74  |  |

|    | 1.<br>2.<br>3.<br>4.<br>5.             | Instruction Set Organization, 74 Informal Groupings of Instructions, 74 Other Instruction Groupings, 79 Symmetric Instruction Sets, 79 Example Instruction Forms, 81                                                                       |     |  |

|    |                                        | <ul><li>5.1. UNIVAC 1100, 81</li><li>5.2. Data General NOVA, 82</li><li>5.3. Other Formats, 83</li></ul>                                                                                                                                   |     |  |

| 7. | Cha                                    | nges in Program Sequencing                                                                                                                                                                                                                 | 86  |  |

|    | 1.<br>2.<br>3.<br>4.                   | Sequence Alteration, 86 Branching, 86 Condition Code Logic, 89 Skip Logic, 92                                                                                                                                                              |     |  |

| 8. | Subroutine Linkage                     |                                                                                                                                                                                                                                            |     |  |

|    | 1.<br>2.<br>3.<br>4.<br>5.<br>6.<br>7. | Concept of a Subroutine, 95 Subroutine Linkage, 96 Basic Linkage Instruction, 96 Basic Stack Linkage Control, 99 Parameter Passing, 101 Activation Record, 102 Stacks, Parameters, and Activation Records, 103 Addressing and Linkage, 105 |     |  |

| 9. | Inte                                   | rrupt Mechanisms and Control States                                                                                                                                                                                                        | 107 |  |

|    | 1.                                     | Interrupt Mechanisms, 107                                                                                                                                                                                                                  |     |  |

|    |                                        | <ul><li>1.1. Introduction to Interrupt Response, 107</li><li>1.2. Interrupt Inhibition, 109</li></ul>                                                                                                                                      |     |  |

|    | 2.<br>3.                               | Variations in Interrupt Architecture, 109<br>General Description of S/370 Interrupt Architecture, 110                                                                                                                                      |     |  |

|    |                                        | <ul> <li>3.1. Interrupt Classes, 110</li> <li>3.2. The S/370 Program Status Word, 111</li> <li>3.3. Organization of Lower Memory, 113</li> <li>3.4. Interrupt Response, 114</li> </ul>                                                     |     |  |

|    | 4.<br>5.                               | Other Interrupt Schemes, 115<br>Control States, 116                                                                                                                                                                                        |     |  |

| 10. | Virtual Memory                                 |                                                                                                                                                                                                                                                                                                                                                 |     |

|-----|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | 1.<br>2.                                       | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                           |     |

|     |                                                | <ul> <li>2.1. Basic Mechanisms, 122</li> <li>2.2. Memory Space Management, 123</li> <li>2.3. Address Formation in Paging Systems, 124</li> <li>2.4. Page Faults, 125</li> <li>2.5. Linear Virtual Memory and Protection, 127</li> <li>2.6. Segmentation in Linear Virtual Memories, 127</li> <li>2.7. Associative Memory Assist, 127</li> </ul> |     |

|     | 3.                                             | Alternative Architectural Concepts, 129                                                                                                                                                                                                                                                                                                         |     |

| 11. | Inpo<br>1.<br>2.<br>3.<br>4.<br>5.<br>6.<br>7. | Input/Output, 132 Disk Characteristics, 134 Input/Output Architecture Features, 136 Basic Processor I/O Architecture, 137 Operating Systems Services, 140 Input/Output Supervisor Flow, 142 Control Languages, 143 Higher Levels of Input/Output Support, 145                                                                                   | 132 |

|     | _                                              | iography, 146                                                                                                                                                                                                                                                                                                                                   |     |

| 12. | The                                            | Power of an Architecture                                                                                                                                                                                                                                                                                                                        | 147 |

|     | 1.<br>2.                                       | Concept of Architectural Power, 147 The Army-Navy Study, 148                                                                                                                                                                                                                                                                                    |     |

|     |                                                | <ul><li>2.1. Absolute Criteria, 149</li><li>2.2. Quantitative Criteria, 151</li></ul>                                                                                                                                                                                                                                                           |     |

|     | 3.<br>4.<br>5.<br>6.                           | Measures of an Architecture, 154 Functional Instructions, 155 Architectural Comparisons, 156 Ideal Architecture, 158                                                                                                                                                                                                                            |     |

|     |                                                | <ul><li>6.1. Addressing and Memory Referencing, 159</li><li>6.2. Characteristics of Ideal Architecture, 159</li></ul>                                                                                                                                                                                                                           |     |

|     | 7.<br>8.<br>9.                                 | Architecture, Compilability, and Design Complexity, 161 The Great Debate, 163 Level of an Architecture, 163                                                                                                                                                                                                                                     |     |

|     | Bibli                                          | 9.1. Support of an Operating System, 165 9.2. Extension Toward Higher-Level Languages, 166 iography, 168                                                                                                                                                                                                                                        |     |

Contents xi

|     | PA.              | RI TWO ORGANIZATION AND IMPLEMENTATION                                                                                                                                                                                                                                                                                                                            | )N  |

|-----|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 13. | Co               | ncepts in Organization and Implementation                                                                                                                                                                                                                                                                                                                         | 173 |

|     | 1.<br>2.         | Introduction, 173 Organization and Implementation Decisions, 174                                                                                                                                                                                                                                                                                                  |     |

|     |                  | <ul> <li>2.1. Width of Data Paths, 174</li> <li>2.2. Degree of Circuit Sharing, 174</li> <li>2.3. Definition of Specialized Units, 175</li> <li>2.4. Parallelism of Functional Units, 175</li> <li>2.5. Buffering and Queuing, 175</li> <li>2.6. Prediction, 175</li> <li>2.7. Underlying Technology, 176</li> <li>2.8. Functional Implementation, 176</li> </ul> |     |

|     | 3.               | Price/Performance Goals, 176                                                                                                                                                                                                                                                                                                                                      |     |

|     | 4.               | Architecture, Organization, and Price/Performance, 177                                                                                                                                                                                                                                                                                                            |     |

| 14. | Bas              | sic Concepts of Instruction Execution                                                                                                                                                                                                                                                                                                                             | 180 |

|     | 1.               | Basic Cycles, 180                                                                                                                                                                                                                                                                                                                                                 |     |

|     | 2.<br>3.         | Execution of an Instruction—Instruction Stages, 182 Instruction Stages and Machine Cycles, 186                                                                                                                                                                                                                                                                    |     |

| 15. | Org              | ganization for Increased Performance                                                                                                                                                                                                                                                                                                                              | 189 |

|     | 1.               | Organizational Approaches to Faster Machines, 189                                                                                                                                                                                                                                                                                                                 | 203 |

|     | 2.               | Instruction Times, 190                                                                                                                                                                                                                                                                                                                                            |     |

|     | 3.               | Cycles Reduction by Stage Speedup, 190                                                                                                                                                                                                                                                                                                                            |     |

|     | 4.<br>5.         | Stage Redefinition, 191 Resequencing Decode and Address Formation, 192                                                                                                                                                                                                                                                                                            |     |

|     | 6.               | Concluding Remarks, 195                                                                                                                                                                                                                                                                                                                                           |     |

| 16. | Ext              | ended Lookahead                                                                                                                                                                                                                                                                                                                                                   | 197 |

|     | 1.               | Inter-Instruction Overlap, 197                                                                                                                                                                                                                                                                                                                                    |     |

|     | 2.<br>3.         | Storing Values into Memory, 202 Memory Read and Write Contention, 204                                                                                                                                                                                                                                                                                             |     |

|     | 3.<br><b>4</b> . | Memory Reference Delays, 204                                                                                                                                                                                                                                                                                                                                      |     |

|     | 5.               | Increasing Lookahead, 206                                                                                                                                                                                                                                                                                                                                         |     |

|     | 6.               | Details of I/E Function and Relationship, 207                                                                                                                                                                                                                                                                                                                     |     |

|     | 7.               | Buffering and Extended Lookahead, 210                                                                                                                                                                                                                                                                                                                             |     |

| 17. | Para             | allel Instruction Execution                                                                                                                                                                                                                                                                                                                                       | 214 |

|     | 1.               | Multiple Instruction Execution, 214                                                                                                                                                                                                                                                                                                                               |     |

|     | 2.<br>3.         | Considerations in Multiple E-Box Design, 215 Populations of E-Boxes, 216                                                                                                                                                                                                                                                                                          |     |

|     |                  | - p                                                                                                                                                                                                                                                                                                                                                               |     |

|     | 4.<br>5.<br>6.<br>7.             | Delivery of Instructions to E-Boxes, 217 Delivery of Operands to E-Boxes, 218 Relationship between E-Boxes and Registers, 219 Instruction Sequencing, 220                                                                              |     |

|-----|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     |                                  | <ul><li>7.1. Sequencing Techniques, 221</li><li>7.2. Intersecting Memory References, 226</li></ul>                                                                                                                                     |     |

|     | 8.<br>9.                         | Code Equivalence and Rearrangement, 227 Characteristics of E-Unit Designs, 228                                                                                                                                                         |     |

|     | 10.                              | 9.1. Single-Level Units, 228 9.2. Multilevel Pipeline Units, 229 Vector Manipulation, 231                                                                                                                                              |     |

|     | 11.                              | Multiple I-Stream Machines, 233                                                                                                                                                                                                        |     |

| 18. | Mei                              | mory Organization                                                                                                                                                                                                                      | 238 |

|     | 1.<br>2.<br>3.                   | Basic Goals of Memory Design, 238 Enough Memory, 238 Memory Organization, 239                                                                                                                                                          |     |

|     |                                  | 3.1. Banking, 240 3.2. Interleaving to Speed Memory Response, 241                                                                                                                                                                      |     |

|     | 4.<br>5.<br>6.<br>7.<br>8.<br>9. | Memory Lookahead, 242 Memory Partitioning Techniques and Processor Lookahead, 243 Limits on Memory Partitioning, 243 Memory Times, 244 A Memory/Processor Interconnect Organization, 245 Alternative Interconnection Organization, 248 |     |

| 19. | Mei                              | nory Hierarchies                                                                                                                                                                                                                       | 251 |

| ÷   | 1.<br>2.                         | Notion of Hierarchy, 251<br>Instruction Buffers, 253                                                                                                                                                                                   |     |

|     |                                  | <ul> <li>2.1. Basic Buffer Fill Technique, 256</li> <li>2.2. Flexible Priority Driven Buffer Fill, 257</li> <li>2.3. Short Loop Mode, 257</li> </ul>                                                                                   |     |

|     | 3.<br>4.<br>5.                   | Branch Instructions and Instruction Buffering, 257<br>Operand Buffers, 259<br>Cache, 260                                                                                                                                               |     |

|     |                                  | <ul> <li>5.1. Cache Mapping and Loading, 262</li> <li>5.2. Cache Contents Management, 265</li> <li>5.3. Stores and Changes to Cache, 266</li> <li>5.4. Some Concluding Comments, 266</li> </ul>                                        |     |

|     |                                  |                                                                                                                                                                                                                                        |     |

Contents xiii

|     | 6.         | Other Hierarchical Notions. 267                                                                                                                                  |     |

|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | <b>7</b> . | Instruction and Control Memories, 268                                                                                                                            |     |

|     | 8.         | Final Comments on Memory, 269                                                                                                                                    |     |

| 20. | Inp        | ut/Output Design                                                                                                                                                 | 271 |

|     | 1.         |                                                                                                                                                                  |     |

|     | 2.         | ,                                                                                                                                                                |     |

|     | 3.         | Processor Overlap, 276                                                                                                                                           |     |

|     | 4.<br>5.   | More Elaborate Input/Output Design, 278                                                                                                                          |     |

|     | 5.<br>6.   | Buffered Input/Output, 281 Direct Memory Access Organizations, 281                                                                                               |     |

|     | 7.         | Multiple Units, 282                                                                                                                                              |     |

|     | 8.         | General-Purpose Channels, 284                                                                                                                                    |     |

|     | 9.         | Input/Output Processor Concepts, 286                                                                                                                             |     |

|     | 10.        | Processor Support of Input/Output Functions, 288                                                                                                                 |     |

| 21. | Ove        | erview of Implementation                                                                                                                                         | 290 |

|     | 1.         | Introductory Observations on Technology, 290                                                                                                                     |     |

|     |            | <ul> <li>1.1. Physical Change, 290</li> <li>1.2. Performance and Price/Performance, 292</li> <li>1.3. Storage, 292</li> <li>1.4. Summary Remarks, 294</li> </ul> |     |

|     | 2.         | Computer Building Blocks, 294                                                                                                                                    |     |

|     | 3.         | Architecture, Design, and Implementation, 296                                                                                                                    |     |

|     | 4.         | Microprocessors and Microcomputers, 297                                                                                                                          |     |

|     | 5.         | Basics of Implementing One Architecture with Another, 299                                                                                                        |     |

|     | 6.         | Considerations in Implementing One Architecture with Another, 301                                                                                                |     |

|     | 7.         | Microcode Types, 303                                                                                                                                             |     |

|     | 8.         | Extending an Architecture, 304                                                                                                                                   |     |

|     | Bibl       | iography, 305                                                                                                                                                    |     |

|     | INE        | DEX                                                                                                                                                              | 307 |

## **PART ONE**

## **ARCHITECTURE**

## Architecture, Organization, and Implementation

#### 1. ARCHITECTURE

The exact meaning of the word architecture in the context of computers is a little uncertain. In general, architecture refers to the visible characteristics of a system as seen by a person or a program creating code capable of running on the machine. It is common, however, to use the word to mean the view of a machine shown by its assembly language. An assembly language is a low-level programming language in which the basic characteristics of a computer system are more directly represented than in a language like COBOL or FORTRAN. The assembly language programmer is aware of memory locations used in the machine, the actual instructions of a machine, and possibly the general speed of instructions. He\* is not necessarily aware of the underlying organization of the machine in terms of operational logical units or of the hardware technology used in the construction of the machine.

The word architecture is frequently used to mean the visible characteristics of only the element actually performing instructions, that is, the processor of a computer system. Since a programmer may view other elements of a computer system through the processor, architecture also more generally means the characteristics of all the component elements of a system that might concern a programmer working at machine level. These components include processor(s), memory. and input/output subsystems.

A processor is a unit that interprets instructions and changes data in conformity with the instructions of a program. A computer may have one or more processors either dedicated to the execution of specialized instructions or capable of performing all instructions. Memory is a device that holds instructions to be executed and data to be operated on. Input/output subsystems are collections of units that connect processors and memories with the devices (1) that interface with the outside world (printers, terminals, sensors, etc.) cr (2) on

<sup>\*</sup> Throughout this book "he" is used to mean "he" or "she." This avoids the cumbersome "le/she."

which large amounts of additional data or instructions are stored and from or to which data is moved to or from memory.

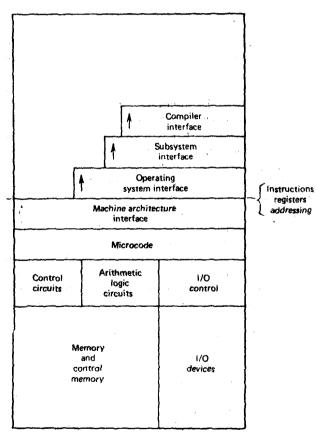

The word architecture is also used to suggest the relationships among various building block elements of hardware and software systems. A system may be thought of as having several architectural levels. Figure 1 shows a representation of architectural levels. Each rectangle represents a set of functions and the horizontal lines are the interfaces between the functions. The first part of this book discusses the architectural level represented by the line labeled machine-architecture interface. The second part of the book addresses the levels that support this interface;

Figure 1. Architectural levels.

#### 2. ELEMENTS OF AN ARCHITECTURE

From the point of view of a programmer looking at a computer system from an architectural level, a system has a set of characteristics that define how data will be represented and referenced, the operations that can be performed on data, and other features that determine how sequences of operations must be executed to achieve a computational result

#### 2.1. Mode of Data Representation

This refers to the representation of values in the processor and memory and the manner in which strings of binary digits should be interpreted at different points in the architecture. The representation of information may be in either pure base 2 (binary) or encoded form generically called the binary-coded decimal. There is also a form of scientific notation, called floating point, where values and exponents may be represented separately in either pure binary or coded form.

When a value is to be manipulated by a processor, the circuits of the processor will be designed to treat the bits of that value as either pure binary, binary-coded decimal, or floating point. For example, a unit designed to add binary numbers will produce an erroneous result for the logic of a program if the data presented to it is in binary-coded decimal form. As another example, a program must know the mode of representation for various values printed on a system printer. Devices like printers always require data to be in some coded decimal form, which may not be the form in which the data is arithmetically manipulated in the processor. The program must issue instructions to put the data in proper form for printing.

#### 2.2. Size of the Basic Data Structure

This refers to the organization of values in the memory of the system and in the processor. The basic architectural data structures are bits, bytes, characters, and words.

A computer system's memory is organized into locations, which may be visualized as elements in a one-dimensional array. Each element has a name, or an address. Thus we speak of a memory having 4096 locations; each location can be directly referenced according to its position on the list. For example, there are memory locations 0000, 0001, 0002..., 4094, 4095. When one of these numbers appears in control circuits connected to memory either the contents (the value that exists in the location) will be brought from memory to the circuits of the processing unit or information in the processing unit will be stored in the memory, depending on the work associated with the address.

Each location in a memory has a fixed size that represents the number of bits (binary digits) held in that location. Thus we speak of machines with 8, 16, 24, and 32-bit memories. This describes the number of bits that will be transferred