The essential companion to the bestselling CMOS: Circuit Design, Layout, and Simulation

# CIVIOS

MIXED-SIGNAL CIRCUIT DESIGN

R. Jacob Baker

IEEE Press Series on Microelectronic Systems Stuart K. Tewksbury and Joe E. Brewer, *Series Editors*

## CMOS Mixed-Signal Circuit Design

#### R. Jacob Baker

Volume II of CMOS: Circuit Design, Layout, and Simulation

IEEE Press Series on Microelectronic Systems

Stuart K. Tewksbury, Series Editor

IEEE Solid-State Circuits Society Sponsor

This book is printed on acid-free paper. @

Copyright © 2002 by The Institute of Electrical and Electronics Engineers, Inc.

No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning or otherwise, except as permitted under Section 107 or 108 of the 1976 United States Copyright Act, without either the prior written permission of the Publisher, or authorization through payment of the appropriate per-copy fee to the Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923, (978) 750-8400, fax (978) 750-4744. Requests to the Publisher for permission should be addressed to the Permissions Department, John Wiley & Sons, Inc., 605 Third Avenue, New York, NY 10158-0012, (212) 850-6011, fax (212) 850-6008, E-Mail: PERMREQ @ WILEY.COM.

For ordering and customer service, call 1-800-CALL WILEY.

#### Library of Congress Cataloging-in-Publication Data is available.

Baker, R. Jacob,

CMOS: Mixed-Signal Circuit Design, volume II/

R. Jacob Baker

p. cm.

Includes bibliographical references and index.

ISBN 0-471-22754-4 (cloth: alk, paper)

Printed in the United States of America

10 9 8 7 6 5 4 3 2 1

## To Julie, Kyri, and Josh

### **Preface to Volume II**

Why a second volume? Why not write a separate, unassociated, book covering mixed-signal circuit design? The answer to these questions comes from my desire to keep from duplicating material available in *CMOS Circuit Design, Layout, and Simulation* (the, sometimes affectionately called, "purple" book containing the first 29 chapters). My goal, when writing this second volume, was to provide a quality textbook and reference that contains material that isn't covered in other textbooks and to couple this material with online learning aids. The supporting companion website, <a href="http://cmosedu.com">http://cmosedu.com</a>, provides worked solutions to the problems, SPICE simulation netlist examples, and discussions concerning mixed-signal circuit design.

#### **Book Organization**

The power of a mixed-signal circuit design, and perhaps the reason they are replacing analog-only designs in the implementation of analog interfaces, comes from the marriage of analog circuits with digital signal processing. Chapter 30 uses the topic of data converter modeling as a vehicle to illustrate some fundamental signal processing topics. In addition, models are developed to aid in the understanding of quantization noise. Chapter 31 discusses signal-to-noise ratio (SNR) and ways of improving SNR using filtering (averaging). The chapter provides a practical discussion of some of the basic tools the mixed-signal designer uses to improve SNR. Decimation, interpolation, and feedback (and the concept of pushing quantization noise to higher-frequencies, i.e., noise-shaping, so that it can be filtered out using a digital filter) are also discussed. Because of the importance of noise-shaping to the design of analog interfaces Ch. 32 is devoted entirely to noise-shaping data converters (often called delta-sigma or sigma-delta data converters). The presentation mixes theory with practical implementations and examples to illustrate the operation of these data converters.

Chapter 33 covers circuit design using submicron CMOS devices. This chapter was born, in part, after I was asked, "Why didn't you use a more modern CMOS process in the purple book?" Submicron devices don't follow the square-law MOSFET model and so hand calculations based on equations derived from the square-law models are somewhat meaningless. I quickly realized, however, that many designers don't do hand calculations and so the significant deviations between long- and short-channel behavior aren't readily apparent. Similarly, students are often asked to compare their hand calculations to SPICE simulation results using the level 1 model. Of course, the simulations and hand calculations match but have little, if anything, to do with the performance of the submicron CMOS circuits in actual silicon.

At the risk of stating the obvious, accurate models for submicron CMOS devices are extremely important. In Ch. 33 the EKV model is used. The EKV model does a good job of modeling the device's transition from weak to strong inversion. This is important when simulating modern data converter or mixed-signal circuits where the threshold voltage doesn't scale with the power supply voltage (i.e., the circuitry is operating a larger percentage of the time in the subthreshold region). As seen in Ch. 33, hand calculations can be performed with transconductance or output resistance values read off of plots generated experimentally or from simulations using the accurate EKV model.

Chapter 34 covers the implementation of data converters. Its purpose is to provide ideas and discussions for implementing the data converter topologies discussed in Ch. 29. Matching, offsets, gains, bandwidths, and topologies are discussed to provide insight into the design of Nyquist rate data converters.

Chapter 35 covers the design of integrated filters. This topic is a book in itself so I've picked the most relevant subjects and attempted to provide practical insight useful when implementing the filters in CMOS technology. The material is complete and useful enough so that, once the material in the chapter is understood, the reader should have little difficulty understanding the merits or trade-offs of any filtering topology. A special twist on the material is the way the topic of digital filtering is presented (hopefully, it is very practical).

Significant effort, in these first six chapters, has been put into integrating theory and examples with simulation results (using actual numbers, i.e., not just symbolic representations). The reader serious about learning the material will find the ability to modify a simulation netlist (downloaded from http://cmosedu.com) and look at the resulting output a very useful learning tool. However, while hand calculations and simulations are very important when learning and designing CMOS circuits, equally, if not more, important is the actual building and testing of the mixed-signal circuits. Chapter 36 provides some examples of actual circuits built "at the bench" to provoke thought and interest. The hope is that instead of just simulating a design, the engineer/student may also want to build and test a representation of the circuit using discrete components. While these discrete circuits won't provide an exact representation of the actual integrated circuits, they can provide insight into the limitations of a particular design. They can also be used to get aquainted with the test equipment and the possible loading that might be introduced into the circuit when probing.

Preface xvii

#### Acknowledgments

Finally, and perhaps most importantly, I would like to thank the reviewers, contributors, colleagues, and (especially!) students who helped make this book possible: Jake Anderson, Brian Bergeson, Tom Bernhard, Kurt Beigel, Jan Bissey, Bill Black, Ken Boorom (special thanks for the very detailed reviews), Dave Boyce, Liz Brauer, Joe Brewer, Curtis Cahoon, Mansun Chan, John Chen, Cathy Faduska, Chris Fayomi, Ed Fong, Dan Foty, Rich Friel, Paul Furth, Randy Geiger, David Goldman, Neil Goldsman, Tyler Gomm, Mike Green, John Griffin, Joe Hartman, Francis Heck, Rick Hilton, Gexin Huang, Glen Hush, Pandurang Irkar, Alok Jain, Brent Keeth, Christy Kuhnen, Harry Li, Yantao Ma, Paul Mason, Mary Miller, Bob Moehrke, Ken Moore, Sugato Mukherjee, Fred Perner, Adrian Ong, Zuxu Qin, Jeremy Rice, Ben Rivera, Brandon Roth, Savang Sengkhamyong, Mir Seyyedy, Brian Shirley, Joseph P. Skudlarek, Jim Slupe, Ken Smith, Mike Smith (special thanks for WinSPICE), Liu Song, Stuart Tewksbury, Lisa Van Horn, Tony VenGraitis, and Tom Voshell.

Boise, ID, January 2002

R. Jacob (Jake) Baker

## **Contents**

| Preface to Volume II                                                    | χv |

|-------------------------------------------------------------------------|----|

| Chapter 30 Data Converter Modeling                                      | 1  |

| 30.1 Sampling and Aliasing: A Modeling Approach                         | 2  |

| 30.1.1 Impulse Sampling                                                 | 2  |

| A Note Concerning the AAF and RCF                                       | 4  |

| Time-Domain Description of Reconstruction                               | 9  |

| Using SPICE for Spectral Analysis (Looking at the Spectrum of a Signal) | 13 |

| Representing the Impulse Sampler's Output in the Z-Domain               | 16 |

| An Important Note                                                       | 18 |

| 30.1.2 The Sample and Hold                                              | 19 |

| SPICE Modeling the Sample and Hold                                      | 19 |

| S/H Spectral Response                                                   | 20 |

| Circuit Concerns for Implementing the S/H                               | 25 |

| 30.2 SPICE Models for DACs and ADCs                                     | 26 |

| 30.2.1 The Ideal DAC                                                    | 26 |

| SPICE Modeling Approach                                                 | 28 |

| 30.2.2 The Ideal ADC                                                    | 32 |

| Summary                                                                 | 35 |

| 30.3 Quantization Noise                                                 | 35 |

viii Contents

| 30.3.1 Viewing the Quantization Noise Spectrum Using Simulations             | 37         |

|------------------------------------------------------------------------------|------------|

| An Important Note                                                            | 39         |

| RMS Quantization Noise Voltage                                               | 40         |

| Treating Quantization Noise as a Random Variable                             | 42         |

| Calculating RMS Quantization Noise Voltage from a Spectrum                   | 43         |

| The DFT's Relationship to the Continuous Time Fourier<br>Transform           | 5 <b>1</b> |

| 30.3.2 Quantization Noise Voltage Spectral Density                           | 52         |

| Reducing Quantization Noise Using Averaging                                  | 54         |

| The Noise Spectral Density View of Averaging                                 | 55         |

| An Important Note                                                            | 56         |

| Practical Implementation of Averaging in ADCs                                | 57         |

| Chapter 31 Data Converter SNR                                                | 63         |

| 31.1 Data Converter SNR: An Overview                                         | . 64       |

| 31.1.1 Effective Number of Bits                                              | 64         |

| Signal-to-Noise Plus Distortion Ratio                                        | 66         |

| Spurious-Free Dynamic Range                                                  | 68         |

| Dynamic Range                                                                | 68         |

| Specifying SNR and SNDR                                                      | 69         |

| 31.1.2 Clock Jitter                                                          | 70         |

| Using Oversampling to Reduce Sampling Clock Jitter Stability<br>Requirements | 72         |

| A Practical Note                                                             | 74         |

| Modeling Clock Jitter with SPICE                                             | 74         |

| Using Our SPICE Jitter Model                                                 | 78         |

| 31.1.3 A Tool: The Spectral Density                                          | 79         |

| The Spectral Density of Deterministic Signals: An Overview                   | 79         |

| The Spectral Density of Random Signals: An Overview                          | 82         |

| Specifying Phase Noise from Measured Data                                    | 86         |

| 31.2 Improving SNR Using Averaging                                           | . 87       |

| 31.2.1 Using Averaging to Improve SNR                                        | 87         |

| Spectral Density View of Averaging Revisited                                 | 88         |

| An Important Observation                                                     | 92         |

| Jitter and Averaging                                                         | 93         |

| Relaxed Requirements Placed on the Antialiasing Filter                       | 94         |

| Data Converter Linearity Requirements                                        | 95         |

| Adding a Noise Dither to the ADC Input                                       | 97         |

| The Z-Plane                                                                  | 99         |

Contents

| 31.2.2 Decimating Filters for ADCs                                          | 106        |

|-----------------------------------------------------------------------------|------------|

| The Accumulate and Dump                                                     | 106        |

| Averaging without Decimation                                                | 111        |

| Relaxed Requirements Placed on the Antialiasing Filter<br>Revisited         | 113        |

| Implementing Averaging Fifters                                              | 114        |

| Aliasing Concerns When Using Decimation                                     | 120        |

| A Note Concerning Stability                                                 | 122        |

| Decimating Down to 2B                                                       | 124        |

| 31.2.3 Interpolating Filters for DACs                                       | 126        |

| The Dump and Interpolate                                                    | 127        |

| Practical Implementation of Interpolators                                   | 128        |

| 31.2.4 Bandpass and Highpass Sinc Filters                                   | 132        |

| Canceling Zeroes to Create Highpass and Bandpass Filters                    | 132        |

| Frequency Sampling Filters                                                  | 135        |

| 31.3 Using Feedback to Improve SNR                                          | 136        |

| 31.3.1 The Discrete Analog Integrator                                       | 136        |

| A Note Concerning Block Diagrams                                            | 138        |

| 31.3.2 Modulators                                                           | 140        |

| Chapter 32 Noise-Shaping Data Converters                                    | 149        |

| 32.1 Noise-Shaping Fundamentals                                             | 149        |

| 32.1.1 SPICE Models                                                         | 149        |

| Nonoverlapping Clock Generation and Switches                                | 150        |

| Op-Amp Modeling                                                             | 151        |

| SPICE Modeling a 1-Bit ADC                                                  | 153        |

| 32.1.2 First-Order Noise-Shaping                                            | 154        |

| A Digital First-Order NS Demodulator                                        | 157        |

| Modulation Noise in First-Order NS Modulators                               | 158        |

| RMS Quantization Noise in a First-Order Modulator                           | 162        |

| Decimating and Filtering the Output of a NS Modulator                       | 164        |

| Implementing the Sinc Averaging Filter Revisited                            | 167        |

| Analog Sinc Averaging Filters using SPICE                                   | 169        |

| Using our SPICE Sinc Filter Model                                           | 171        |

| Analog Implementation of the First-Order NS Modulator                       | 172        |

| The Feedback DAC                                                            |            |

|                                                                             | 174        |

| Understanding Averaging and the Use of Digital Filtering with the Modulator | 174<br>174 |

X Contents

| Integrator and Forward Modulator Gain                                     | 182 |

|---------------------------------------------------------------------------|-----|

| Comparator Gain, Offset, Noise, and Hysteresis                            | 186 |

| Op-Amp Gain (Integrator Leakage)                                          | 186 |

| Op-Amp Settling Time                                                      | 188 |

| Op-Amp Offset                                                             | 189 |

| Op-Amp Input Referred Noise                                               | 190 |

| Practical Implementation of the First-Order NS Modulator                  | 191 |

| Fully-Differential Modulator with a Single-Ended Input                    | 193 |

| 32.1.3 Second-Order Noise-Shaping                                         | 194 |

| Second-Order Modulator Topology                                           | 195 |

| Integrator Gain                                                           | 198 |

| Implementing Feedback Gains in the DAI                                    | 202 |

| Using Two Delaying Integrators to Implement the Second-Order<br>Modulator | 205 |

| Selecting Modulator (Integrator) Gains                                    | 207 |

| Understanding Modulator SNR                                               | 208 |

| 32.2 Noise-Shaping Topologies                                             | 210 |

| 32.2.1 Higher-Order Modulators                                            | 210 |

| M <sup>th</sup> -Order Modulator Topology                                 | 211 |

| Decimating the Output of an Mth-Order NS Modulator                        | 212 |

| Implementing Higher-Order, Single-Stage, Modulators                       | 213 |

| 32.2.2 Multibit Modulators                                                | 215 |

| Simulating a Multibit NS Modulator Using SPICE                            | 215 |

| Multibit Demodulator (Used in a NS DAC) Implementation (Error Feedback)   | 217 |

| Implementation Concerns                                                   | 220 |

| 32.2.3 Cascaded Modulators                                                | 221 |

| Second-Order (1-1) Modulators                                             | 221 |

| Third-Order (1-1-1) Modulators                                            | 223 |

| Third-Order (2-1) Modulators                                              | 223 |

| Implementing the Additional Summing Input                                 | 226 |

| 32.2.4 Bandpass Modulators                                                | 228 |

| Implementing a Bandpass Modulator                                         | 229 |

| Chapter 33 Submicron CMOS Circuit Design                                  | 235 |

| 33.1 Submicron CMOS: Overview and Models                                  | 236 |

| 33.1.1 CMOS Process Flow                                                  | 236 |

| 33.1.2 Capacitors and Resistors                                           | 239 |

| Using a MOSFET as a Capacitor                                             | 239 |

| Using a Native or Natural MOSFET Capacitor                                | 239 |

Contents

| The Floating MOS Capacitor                    | 239 |

|-----------------------------------------------|-----|

| Metal Capacitors                              | 241 |

| An Important Note                             | 244 |

| Resistors                                     | 245 |

| 33.1.3 SPICE MOSFET Modeling                  | 248 |

| Model Selection                               | 248 |

| Model Parameters                              | 252 |

| An Important Note                             | 254 |

| A Note Concerning "Long L MOSFETs"            | 255 |

| 33.2 Digital Circuit Design                   | 255 |

| 33.2.1 The MOSFET Switch                      | 256 |

| Bidirectional Switches                        | 258 |

| A Clocked Comparator                          | 261 |

| Common-Mode Noise Elimination                 | 264 |

| 33.2.2 Delay Elements                         | 271 |

| 33.2.3 An Adder                               | 274 |

| 33.3 Analog Circuit Design                    | 276 |

| 33.3.1 Biasing                                | 276 |

| Selecting the Excess Gate Voltage             | 276 |

| Selecting the Channel Length                  | 277 |

| Small-Signal Transconductance, $g_m$          | 279 |

| MOSFET Transition Frequency, $f_{\tau}$       | 279 |

| The Beta Multiplier Self-Biased Reference     | 280 |

| 33.3.2 Op-Amp Design                          | 284 |

| Output Swing                                  | 284 |

| Slew-rate Concerns                            | 287 |

| Differential Output Op-Amp                    | 295 |

| 33.3.3 Circuit Noise                          | 298 |

| Thermal Noise                                 | 298 |

| The Spectral Characteristics of Thermal Noise | 299 |

| Noise Equivalent Bandwidth                    | 301 |

| MOSFET Noise                                  | 303 |

| Noise Performance of the Source-Follower      | 304 |

| Noise Performance of a Cascade of Amplifiers  | 305 |

| DAI Noise Performance                         | 306 |

| Chapter 34 Implementing Data Converters       | 311 |

| 34.1 R-2R Topologies for DACs                 | 312 |

| 34.1.1 The Current-Mode R-2R DAC              | 312 |

xii Contents

| 34.1.2 The Voltage-Mode R-2R DAC                           | 314 |

|------------------------------------------------------------|-----|

| 34.1.3 A Wide-Swing Current-Mode R-2R DAC                  | 316 |

| DNL Analysis                                               | 317 |

| INL Analysis                                               | 318 |

| Switches                                                   | 319 |

| Experimental Results                                       | 319 |

| Improving DNL (Segmentation)                               | 321 |

| Trimming DAC Offset                                        | 323 |

| Trimming DAC Gain                                          | 325 |

| Improving INL by Calibration                               | 326 |

| 34.1.4 Topologies Without an Op-Amp                        | 328 |

| The Voltage-Mode DAC                                       | 328 |

| Two Important Notes Concerning Glitches                    | 331 |

| The Current-Mode (Current Steering) DAC                    | 332 |

| 34.2 Op-Amps in Data Converters                            | 334 |

| Gain Bandwidth Product of the Noninverting Op-Amp Topology | 335 |

| Gain Bandwidth Product of the Inverting Op-Amp Topology    | 336 |

| 34.2.1 Op-Amp Gain                                         | 337 |

| 34.2.2 Op-Amp Unity Gain Frequency                         | 339 |

| 34.2.3 Op-Amp Offset                                       | 339 |

| Adding an Auxiliary Input Port                             | 339 |

| 34.3 Implementing ADCs                                     | 343 |

| 34.3.1 Implementing the S/H                                | 343 |

| A Single-Ended to Differential Output S/H                  | 345 |

| 34.3.2 The Cyclic ADC                                      | 351 |

| Comparator Placement                                       | 352 |

| Implementing Subtraction in the S/H                        | 354 |

| Understanding Output Swing                                 | 357 |

| 34.3.3 The Pipeline ADC                                    | 359 |

| Using 1.5 Bits/Stage                                       | 361 |

| Capacitor Error Averaging                                  | 368 |

| Comparator Placement                                       | 374 |

| Clock Generation                                           | 377 |

| Offsets and Alternative Design Topologies                  | 378 |

| Dynamic CMFB                                               | 382 |

| Layout of Pipelined ADCs                                   | 385 |

| Chapter 35 Integrator-Based CMOS Filters                                                 | 393 |

|------------------------------------------------------------------------------------------|-----|

| 35.1 Integrator Building Blocks                                                          | 393 |

| 35.1.1 Lowpass Filters                                                                   | 393 |

| 35.1.2 Active-RC Integrators                                                             | 395 |

| Effects of Finite Op-Amp Gain Bandwidth Product                                          | 398 |

| Active-RC SNR                                                                            | 403 |

| 35.1.3 MOSFET-C Integrators                                                              | 404 |

| Why use an Active Circuit (an Op-Amp)                                                    | 406 |

| 35.1.4 g <sub>m</sub> -C (Transconductor-C) Integrators                                  | 407 |

| Common-Mode Feedback Considerations                                                      | 410 |

| A High-Frequency Transconductor                                                          | 411 |

| 35.1.5 Discrete-Time Integrators                                                         | 411 |

| An Important Note                                                                        | 415 |

| Exact Frequency Response of a First-Order Discrete- Time<br>Digital (or Ideal SC) Filter | 416 |

| 35.2 Filtering Topologies                                                                | 418 |

| 35.2.1 The Bilinear Transfer Function                                                    | 418 |

| Active-RC Implementation                                                                 | 419 |

| Transconductor-C Implementation                                                          | 419 |

| Switched-Capacitor Implementation                                                        | 420 |

| Digital Filter Implementation                                                            | 421 |

| The Canonic Form (or Standard Form) of a Digital Filter                                  | 425 |

| 35.2.2 The Biquadratic Transfer Function                                                 | 429 |

| Active-RC Implementation                                                                 | 431 |

| Switched-Capacitor Implementation                                                        | 437 |

| High Q                                                                                   | 438 |

| Q Peaking and Instability                                                                | 443 |

| Transconductor-C Implementation                                                          | 445 |

| The Digital Biquad                                                                       | 446 |

| 35.3 Filters using Noise-Shaping                                                         | 448 |

| Removing Modulation Noise                                                                | 448 |

| Implementing the Multipliers                                                             | 451 |

| Chapter 36 At the Bench                                                                  | 459 |

| 36.1 A Push-Pull Amplifier                                                               | 459 |

| Deadbug Prototyping                                                                      | 460 |

| Probing                                                                                  | 462 |

| Testing the Circuit                                                                      | 463 |

XiV Contents

| 36.2 A First-Order Noise-Shaping Modulator | 467 |

|--------------------------------------------|-----|

| Prototyping the Modulator                  | 469 |

| 36.3 Measuring 1/f Noise                   | 472 |

| MOSFET Noise                               | 474 |

| Input-Referred Noise Voltage               | 475 |

| Chopper Stabilization                      | 476 |

| 36.4 A Discrete Analog Integrator          | 479 |

| Clock Generation                           | 480 |

| Prototyping the Filter                     | 482 |

| 35.5 Quantization Noise                    | 485 |

| Prototyping the ADC Circuit                | 488 |

| Index                                      | 493 |

| About the Author                           | 502 |

## Chapter 30

## **Data Converter Modeling**

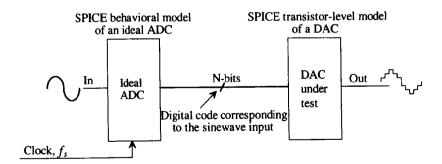

In this chapter we continue our discussion of data converters by discussing methods to model ideal data converters and their components using SPICE. The main goal of this chapter is to provide tools for evaluating mixed-signal designs with large complexity, which can be used in design evaluation and later in the book. In particular, we will generate SPICE models, using behavioral elements, for ideal analog-to-digital converters (ADCs) and digital-to-analog converters (DACs) blocks. This allows us to analyze the performance of a mixed-signal circuit block in a SPICE simulation within a reasonable amount of time. For example, if we have designed a DAC at the transistor level and want to use SPICE to simulate its operation, under various temperatures and matching conditions, we may apply a digital input code generated from our ideal ADC with a sinewave input as seen in Fig. 30.1. Similarly, given a digital signal processing (DSP) system, we can drop our ideal DAC into the simulation at any point where there is a digital word and get an analog waveform output.

Figure 30.1 Generating the sinewave digital code for DAC simulation with an ideal ADC.

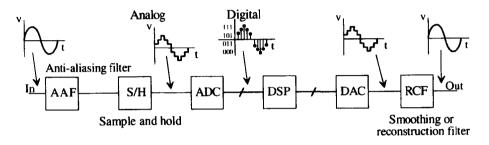

Also, in this chapter we look at how the analog-to-digital and digital-to-analog conversion process affects the signals in the system. Figure 30.2 shows the basic conversion process. We will make extensive use of the spectral analysis capability (discrete fourier transform or DFT) available in SPICE to look at the digital data (and analog signals) in the frequency domain.

Figure 30.2 Signals resulting from A/D and D/A conversion in a mixed-signal system.

#### 30.1 Sampling and Aliasing: A Modeling Approach

In this section we discuss how sampling a signal changes the signal's spectrum. We also discuss how to model the sampling process in SPICE.

#### 30.1.1 Impulse Sampling

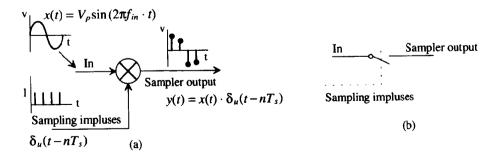

Consider the simple sampling gate shown in Fig. 30.3a. Let's assume we apply a sinewave input, x(t), to this sampling gate of the form,  $V_p \sin(2\pi f_{in} \cdot t)$  (for the moment, a single frequency input). The output of the sampling gate (a.k.a. sampler), y(t), is the product of the input and a sampling unit impulse signal or

$$y(t) = \sum_{n=-\infty}^{\infty} V_p \sin(2\pi f_{in} \cdot nT_s) \cdot \delta_u(t - nT_s)$$

(30.1)

Figure 30.3 (a) Simple sampling gate and (b) SPICE implementation of a sampling gate.