### **IEEE Press Series on Microelectronic Systems**

R. Jacob Baker, Series Editor

# From Frequency to Time-Average Frequency

A Paradigm Shift in the Design of Electronic Systems

**Liming Xiu**

# FROM FREQUENCY TO TIME-AVERAGE-FREQUENCY

# A Paradigm Shift in the Design of Electronic Systems

LIMING XIU

IEEE Press Series on Microelectronic Systems

Copyright © 2015 by The Institute of Electrical and Electronics Engineers, Inc.

Published by John Wiley & Sons, Inc., Hoboken, New Jersey. All rights reserved. Published simultaneously in Canada.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning, or otherwise, except as permitted under Section 107 or 108 of the 1976 United States Copyright Act, without either the prior written permission of the Publisher, or authorization through payment of the appropriate per-copy fee to the Copyright Clearance Center, Inc., 222 Rosewood Drive, Danvers, MA 01923, (978) 750-8400, fax (978) 750-4470, or on the web at www.copyright.com. Requests to the Publisher for permission should be addressed to the Permissions Department, John Wiley & Sons, Inc., 111 River Street, Hoboken, NJ 07030, (201) 748-6011, fax (201) 748-6008, or online at http://www.wiley.com/go/permission.

Limit of Liability/Disclaimer of Warranty: While the publisher and author have used their best efforts in preparing this book, they make no representations or warranties with respect to the accuracy or completeness of the contents of this book and specifically disclaim any implied warranties of merchantability or fitness for a particular purpose. No warranty may be created or extended by sales representatives or written sales materials. The advice and strategies contained herein may not be suitable for your situation. You should consult with a professional where appropriate. Neither the publisher nor author shall be liable for any loss of profit or any other commercial damages, including but not limited to special, incidental, consequential, or other damages.

For general information on our other products and services or for technical support, please contact our Customer Care Department within the United States at (800) 762-2974, outside the United States at (317) 572-3993 or fax (317) 572-4002.

Wiley also publishes its books in a variety of electronic formats. Some content that appears in print may not be available in electronic formats. For more information about Wiley products, visit our web site at www.wiley.com.

Library of Congress Cataloging-in-Publication Data is available.

ISBN: 978-1-110-02732-4

Printed in Singapore by Markono Print Media Pte Ltd

10 9 8 7 6 5 4 3 2 1

#### **FOREWORD**

Dr. Ahmad Bahai

Chief Technology Officer Texas Instruments Inc. Stanford University

Unprecedented innovations in semiconductor technology and manufacturing over last several decades have prompted an impressive growth in high-tech industry, which has immensely influenced our world. Today, electronics has permeated many aspects of our daily lives such as communication, transportation, health, and even our social interactions. A unique combination of efficiency, intelligence, form factor, and affordability of integrated circuits promises to address some of most daunting social and environmental challenges of modern world such as energy, health, and pollution. As more people and things are increasingly connected to each other and to the cloud of massive data and information, we will undoubtedly witness an ever-increasing rate of innovative ideas and applications enabled by semiconductor technology in years to come.

Almost every modern electronic circuit and system requires a timing reference. Reliable generation, transmission, reception, and conditioning and processing of data need timing references as well as some level of synchronization even in asynchronous systems! As the data rate is exponentially growing, the need for accurate timing reference exacerbates. Many advance high-speed data acquisition, interface, and processor-integrated circuits require a clock accuracy of a few femtoseconds (10<sup>-15</sup>)! In addition to a high-accuracy clock reference, generation of different frequencies and distribution of high-speed timing signal in a compact noisy path across the chip or the board are critical and challenging in high-speed analog and digital signal processing. Since the RMS jitter is inversely proportional to Quality Factor of the circuit, a combination of high-performance clock reference, low-noise circuit architecture, high-performance device, and careful layout is critical for a timing solution. The complexity and cost of clock generation and distribution amount to almost one-third of total board cost in many high-performance electronic boards and modules.

#### x FOREWORD

The infrastructure of modern world depends on high-performance clock and timing. High-speed wireless and wired communication networks which are the backbone of Internet and connectivity, power distribution systems, security systems, industrial metrology, scientific research systems, and many other applications increasingly rely on highly accurate and stable timing references.

We have come a long way from using celestial bodies' rotation and revolution as timing references. Modern timing references can provide accuracy, precision, and stability needed for high-performance circuits. Crystal oscillators and its high-stability variations such as VCXO, TCXOs and OCXO, MEMS-based clock references, GPS timing reference, and recently developed chip-scale atomic clocks (CSAC) can provide low jitter and phase noise integrated timing references. Also, advances in phase lock loop, injection-locked oscillators, and frequency synthesizer's theory and techniques such as hybrid and cascade architectures facilitate generation of accurate and stable timing reference at various frequencies as well as recovery and jitter cleaning of timing signal.

As the complexity of electronic systems grows the need for higher performance, robust timing references are becoming more pivotal and challenging. Liming Xiu offers a timely and comprehensive analysis of fundamentals and new approaches in timing and frequency synchronization techniques. The author's theoretical and practical experience through many years of advance R&D in Texas Instruments have been instrumental to providing a useful reference for one of the most challenging topics of today's technology.

I commend Liming for his insightful and articulate text which goes beyond conventional approaches by exposing the readers to many novel ideas and inspiring them to think out of the box.

It's about time.

#### **PREFACE**

#### A PARADIGM SHIFT

The word *paradigm* is defined in the dictionary as "a framework containing the basic assumptions, ways of thinking, and methodology that are commonly accepted by members of a scientific community." In his influential book *The Structure of Scientific Revolutions*, published in 1962, Thomas Kuhn used the term *paradigm shift* to indicate a change in the basic assumptions (the *paradigms*) within the ruling *theory* of *science*. Today, the term paradigm shift is used widely, both in scientific and nonscientific communities, to describe a profound change in a fundamental model or perception of events.

Ever since the clock concept was introduced into microelectronic system design many decades ago, it was assumed that all the cycles in a clock pulse train have to be equal in their lengths (a rigorous clock signal). One reason that this form of clock signal has dominated microelectronic system design for a long time is that, in the past, the requirement for IC clocking was mostly straightforward. A clock signal with a fixed rate was sufficient for most systems. However, the complexity of future systems changes the game. Low-power operation, low electromagnetic radiation, synchronization among networked devices (e.g., Internet of Things), complex data communication schemes, etc., all require a clock signal that is flexible.

Another reason behind the dominance of this style of rigorous clock is that time, which shows its existence and its flow indirectly through the use of a clock pulse train, is not a physical entity that can be controlled and observed directly. Thus, creating a flexible clock is an inherently difficult task. It demands effort beyond simply playing with various techniques at the circuit level. Philosophically it requires an adjustment, at a fundamental level, in our thinking about the way of clocking microelectronic

systems. The "anomaly" in this case is a new perspective on the concept of clock frequency. In this line of argument, the materials presented in this book induce a paradigm shift in the field of microelectronic system design.

## IN ELECTRICAL WORLD WE ONLY DEAL WITH TWO THINGS: LEVEL AND TIME

Although there are numerous different types of microelectronic devices and systems supporting the daily operation of our society, we only deal with two things when designing such devices and systems: level and time. Microelectronic devices and systems perform their magic by creating a variety of events that occur inside the silicon chip in a predetermined order. The purpose of such events is to essentially specify "what happens at when." In the process of creating those events, we need "level" to represent "what" and "time" to describe "when."

In describing "what," there are two approaches to implementation: (1) the analog way and (2) the digital way. The analog method uses proportional relationships to describe the physical world. (*Physical world*: It is the sum of all the stuff around us; you can see it, touch it, taste it, hear it, or smell it. And these five senses are based on the *proportional* relationship.) By contrast, the digital approach employs a binary system (i.e., on/off) to represent information. It is the natural language for performing computation using microelectronic devices. In the past several decades of silicon chip design, the task of describing "what" has been studied in great depth. Perhaps, it is fair to say that it is a mature art now.

However, we have not been as creative in dealing with "when." Historically, we were fixed in the belief that any clock cycle has to be exactly the same as any other cycle. Hence, we restrained our hand at making the clockwork for the electrical world. Since "time" is half of the story in "what happens at when," it can impact the microelectronic system's overall information processing efficiency in great deal. A small step change in the fundamental level (the anomaly) can produce a profound influence on upper level structures. This flow of thought is reflected in the development from the ideas of Chapters 1–4 to their applications in Chapters 5–7.

#### INTERNET OF THINGS AND THE CLOCK

The Internet of Things (IoT) is a growing network of everyday objects, from industrial machines to consumer goods, which can share information and complete tasks without human interference. It comprises three key components: (1) the things themselves, (2) the communication networks connecting them, and (3) the computing systems that make use of the data flowing among the things. IoT is the catalyst for new business growths across multiple industries, including industrial, medical, consumer, and automotive. The semiconductor industry, which provides chips designed for various IoT applications, is the enabler of this IoT trend. Designers of microelectronic products for IoT applications, however, face several unique challenges. The three most

noticeable ones are the ultralow-power challenge, the ultralow-cost challenge, and the miniaturization challenge.

As said, IoT is a network of many things. It implies that the key in IoT is the "connection." For things in IoT to connect, it requires the establishment of a "common view of time" among the things. In other words, time synchronization of the network plays a major role in IoT. There are two essential pieces for establishing this synchronization: Each thing must have its own time (frequency) source to control its internal operation and there must exist a communication protocol agreed by all the things to establish and maintain the "common view of time." The design of this communication protocol depends heavily on the quality of the time (frequency) source. In IoT's harsh design environment of ultralow power, extreme small size, and ultralow cost, building a good time (frequency) source for each thing is an extremely challenging task. It requires innovations on clocking. Chapter 5 of this book provides some innovative options to meet this challenge.

#### CLOCK IS ENABLER FOR SYSTEM-LEVEL INNOVATION

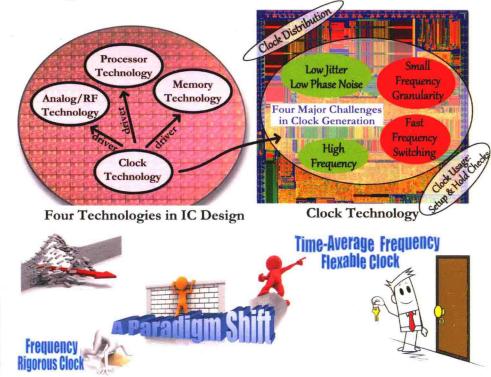

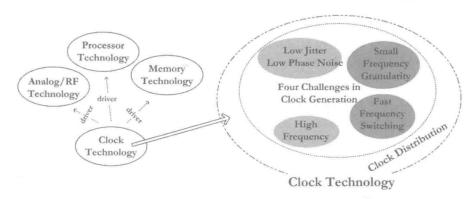

Viewing from a high level, there are four fundamental technologies supporting the entire IC design business: processor technology, memory technology, analog/RF technology, and clock technology. In the past several decades, a tremendous amount of effort has been spent on the development of the first three technologies. Clock technology falls behind in this race. One of the key reasons for this is that, as mentioned before, clock technology deals with a special entity: time. It is neither directly observable nor directly controllable. The circuit designer can only play with it indirectly, through voltage and/or current. This lag, however, provides us an opportunity to make significant progress. It is a battleground for new ideas. It is a potential birthplace for great inventions. It is one of the enablers for system-level innovation. Chapters 5–7 are the first round of effort in this direction.

# WHAT IS NEW ON CLOCK? FLEXIBILITY VERSUS SPECTRUM PURITY

When the term *flexible clock* is used, it refers to a clock signal whose frequency can be (1) arbitrarily set (within a small frequency granularity, similar to the way that voltage level can be arbitrarily reached within a quantization resolution) and (2) changed quickly (similar to the way that voltage level can make transition quickly). Preferably, these two features shall be achieved simultaneously and be available to the clock user at a reasonable cost.

A rigorous clock has the characteristic of high spectrum purity, which is beneficial to certain applications such as functioning as a carrier in wireless communication and as the driving clock for analog-to-digital converter. There are, however, many more applications wherein spectrum purity is not of high concern. Instead, a clock signal possessing the capability of small frequency granularity and fast frequency

switching is more useful. Therefore, there is a crucial trade-off to be made when an IC design problem is investigated. In the past, a clock of high spectrum purity was the undeniable winner. However, for future microelectronic system design, this is not necessarily always the case. Chapters 5 and 6 of this book demonstrate that a flexible clock is more cost-effective in solving many emerging problems in modern applications.

#### CLOCK IS NOT PLL; IT IS MUCH BIGGER

Within the community of IC design professionals, a popular view is that IC clocking is just the PLL (phase-locked loop) design. This is far from the truth. PLL design is just one piece of a big puzzle. The PLL specializes in generating the clock pulse train. There are, however, many other aspects to the clock, including the task of delivering a clock signal, logically and physically, to all the areas that need it. Another important task is the correct use of the clock signal once it actually reaches the destinations (i.e., to drive the cells). This work is important because it can cause system failure if certain conditions are not satisfied (i.e., the setup and hold checks). Moreover, as a signal bearing highly concentrated energy at a particular frequency, the clock is a danger aggressor capable of doing serious damage to other signals around it. Thus, care must be given to avoid this from happening. Furthermore, the clock network consumes the largest percentage of overall chip power consumption. The reduction of power usage is heavily dependent on how the clock is used. Chapter 2 of this book helps the reader establish an appropriate appreciation of the clock: clock is not simply the PLL; it is a much bigger topic.

#### "JITTERY" CLOCK IS NOT NECESSARILY A BAD THING

Among clock circuit designers and clock signal users, jitter is always a bad thing. The essence of a clock pulse train is to create a series of "moments in the flow of time" by utilizing the mechanism of the "voltage-level-crossing-a-threshold." The resulting moments are used as the reference points for other events happening inside the microelectronic system. Therefore, the requirement on those moments is that their locations-in-time must be predictable and precise. Jitter is a parameter measuring this quality. Thus, a jittery clock is undesirable since it reduces the effectiveness of the clock in coordinating other events. However, jitter is not without any use. An obvious example of its applicability is that jitter in a clock signal can help reduce its electromagnetic radiation since it spreads the clock energy.

The not-so-obvious, and more valuable, use of a "jittery" clock is to trade the irregularity in the moment with the flexibility. As mentioned, the flexibility associated with a clock signal refers to its capability of fine frequency resolution and fast frequency switching. When used with care of this irregularity in the moment, a clock signal can be made flexible by intentionally introducing "controlled jitter" into it. This capability is important for certain applications, such as in adaptive clock

generation and in clock data recovery. Indeed, it outweighs the requirement on the clock's spectrum purity in such applications. Hence, a jittery clock is not necessarily a bad thing. An example is provided in Chapter 5 to support this unconventional view. It also serves as an example of "thinking out of the box."

#### THE POWER OF IDEA

Many times in our history, the power of an idea has changed the landscape of our civilization. Such ideas include liberty, democracy, Romanticism, Confucianism, Marxism, Zionism, among others. Each of those great ideas led to a profound movement that changed the way we live. In science and technology, the latest example of such an idea would be Einstein's theory of relativity. It links the space and time together, resulting in a thing called space-time. This breakthrough idea, which was regarded as a ridiculous one by most people when it made its debut, is proven to be one of the greatest in human history. This idea is an "anomaly" that later leads to a great paradigm shift in science.

In my previous book *Nanometer Frequency Synthesis beyond Phase Locked Loop* (Wiley-IEEE Press, 2012, IEEE Press Series on Microelectronic Systems), a new perspective on clock frequency was introduced and its associated implementation technology was presented. This angle of using a clock pulse train is not aligned with the prevailing view. However, evidences show that it works. In many cases, it can do a better job with lower cost. After that book was published, I have often encountered the question of "what is it useful for?" from people of old fashion. While the material presented in that book focused on building the circuit at component level, this book will answer the question of how to use it in an upper level to create better systems. This book is the continuation in this route of new microelectronic system design methodology; it can be treated as Volume II of this series. Volume I (the 2012 book) teaches the technique of making a field programmable frequency generator (FPFG). With this FPFG available to chip designers, Volume II (this book) shows the ways of using it. The spirit of this series of books is innovation. The goal is to create cheaper, better, and faster products.

#### **ACKNOWLEDGMENT**

Ireceived my bachelor's and first master's degrees from Tsinghua University (Beijing, China). Tsinghua's training prepared me to be a scientist with an innate curiosity on the structure of the world, with a strong intention to pursue the beauty of the universe. I earned my second master's degree from Texas A&M University (College Station, TX, USA). A&M's education turned me into an engineer with a desire to build and invent. I got my "PhD degree" from "University of TI" (Texas Instruments Inc., a.k.a. Training Institute). My "PhD adviser" is the collection of numerous TI engineers, including my wife (a long-time TIer).

The TI engineers fighting in the semiconductor front line taught me how to deal with real-world problems and, more importantly, equipped me with the capability to spot emerging problems. My "PhD dissertation" is the invention of Flying-Adder frequency synthesis architecture plus the book of *VLSI Circuit Design Methodology Demystified: A Conceptual Taxonomy* (quality controlled by the forewords written by TI CEO Rich Templeton and then TI CTO Hans Stork). I truly believe that my "PhD degree" acquired in this environment is competitive with the PhD degree issued from any top engineering school in the world. Novatek Microelectronics (Taiwan) is a place that provides me with room for doing some serious thinking, to sharpen my vision. The Novatek experience enabled me to compose my second book *Nanometer Frequency Synthesis Beyond the Phase-Locked Loop*. The warmth of Novatek people will be remembered for life. My 2-year tenure as vice president of IEEE Circuit and System Society is unique. It is beneficial to me in many ways. It has broadened my view from another direction.

This book would be impossible if any part of the aforementioned experience was missed. It is the result of knowledge-and-experience accumulation over three decades. This long process is enjoyable most of the time, but painful occasionally.

#### xviii ACKNOWLEDGMENT

Thanks to all those who helped me in this journey. I also want to thank my editors in Wiley & IEEE, Mary Hatcher and Brady Chin, for their great help. Their efficiency is greatly admired by me. Their patience on me is deeply appreciated. Finally, I want to give special thanks to my dear wife Zhihong You (my Tsinghua, Texas A&M, and TI alumnus). She allowed me to spend time on this book in countless evenings and weekends while she virtually acted alone on raising our two daughters, and successfully sent the elder one to Yale University in 2014.

Liming Xiu Dallas, TX 2015

# **CONTENTS**

| Foreword       |                                                              |                                                                                         |  |  |

|----------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|

| Preface        |                                                              |                                                                                         |  |  |

| Acknowledgment |                                                              |                                                                                         |  |  |

| 1              | Importance of Clock Signal in Modern Microelectronic Systems |                                                                                         |  |  |

|                | 1.1                                                          | Clock Technology: One of the Four Fundamental Technologies in IC Design, 1              |  |  |

|                | 1.2                                                          | Clock Signal Generator: The Knowledge-and-Skill Gap between Its Creator and Its User, 3 |  |  |

|                |                                                              | How Is Sense-of-Time Created in Electrical World?, 5                                    |  |  |

|                |                                                              | All Microelectronic Systems Are Frequency Driven, 9                                     |  |  |

|                |                                                              | A New Kid in Town: The Clock Architect, 14                                              |  |  |

|                | Refe                                                         | rences, 15                                                                              |  |  |

| 2              | Everything about the Clock                                   |                                                                                         |  |  |

|                | 2.1                                                          | Clock Generation, 17                                                                    |  |  |

|                | 2.2                                                          | Clock Distribution: Functional, 18                                                      |  |  |

|                |                                                              | Clock Distribution: Physical, 19                                                        |  |  |

|                |                                                              | Clock Usage: System Perspective, 20                                                     |  |  |

|                |                                                              | Clock Usage: Electrical Perspective, 20                                                 |  |  |

|                |                                                              | Clock Signal Quality, 22                                                                |  |  |

|                | 2.7                                                          | Clock Network Power Consumption, 23                                                     |  |  |

|                | References, 23                                               |                                                                                         |  |  |

| 3                                                                                           | fferent Way of Constructing a Clock Signal:<br>e-Average-Frequency | 27                                                                                                                                                              |    |  |

|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

|                                                                                             | 3.1<br>3.2                                                         | Motivation, 27<br>Clock Is Trigger and Gatekeeper: Essence of Stage-by-Stage                                                                                    |    |  |

|                                                                                             | 3.3<br>3.4                                                         | Operation, 30 Time-Average-Frequency: Brief Review, 32 Circuit Architecture of Time-Average-Frequency Direct Period                                             |    |  |

|                                                                                             | 3.5                                                                | Synthesis, 34 The Two Long-Lasting Problems: Small Frequency Granularity and Fast Frequency Switching, 37                                                       |    |  |

|                                                                                             | 3.6<br>3.7                                                         | Time-Average-Frequency and "Jittery" Clock, 40 Frequency Switching and Waveform Establishment in TAF-DPS Clock Generator, 43                                    |    |  |

|                                                                                             |                                                                    |                                                                                                                                                                 |    |  |

|                                                                                             |                                                                    | Impact of Implementation Imperfection, 52 grences, 54                                                                                                           |    |  |

| 4                                                                                           |                                                                    | e-Average-Frequency and Special Clocking Techniques: Gapped ek, Stretchable Clock, and Pausible Clock                                                           | 55 |  |

|                                                                                             | 4.1<br>4.2<br>4.3                                                  | Stretchable Clock, Pausible Clock, and Asynchronous FIFO, 59                                                                                                    |    |  |

|                                                                                             | Refe                                                               | erences, 65                                                                                                                                                     |    |  |

| 5 Microelectronic System Design in the Field of<br>Time-Average-Frequency: A Paradigm Shift |                                                                    |                                                                                                                                                                 |    |  |

|                                                                                             | 5.1<br>5.2                                                         | Digital Data Communication in the Field of Frequency, 69 Data Transfer in Time-Average-Frequency Field: Transmitting Clock Available, 72                        |    |  |

|                                                                                             | 5.3                                                                | Data Transfer in Time-Average-Frequency Field: Clockless<br>Transmission, 74                                                                                    |    |  |

|                                                                                             |                                                                    | Clock Data Recovery in Time-Average-Frequency Field, 76                                                                                                         |    |  |

|                                                                                             |                                                                    | Network-on-Chip GALS Strategy in Time-Average-Frequency Field,                                                                                                  | 82 |  |

|                                                                                             | 5.6                                                                | Network Time Synchronization in Time-Average-Frequency Field:                                                                                                   |    |  |

|                                                                                             | 5.7                                                                | Improved Time Granularity and Frequency Granularity, 89 Crystalless Reference and Time-Average-Frequency Driven VLSI System: Source for Frequency Reference, 93 |    |  |

|                                                                                             | 5.8                                                                | Crystalless Reference and Time-Average-Frequency Driven VLSI<br>System: Harmony in System-Level Design, 96                                                      |    |  |

|    | <ul> <li>5.9 Efficient Implementation of MCXO System in Time-Average-Frequency Field, 97</li> <li>5.10 CPU Throttling in Time-Average-Frequency Field, 105</li> <li>5.11 Spreading Clock Energy in Time-Average-Frequency Field, 108</li> <li>5.12 TAF-DPS as Circuit Technique in Building Special Function Blocks, 5.12.1 TAF-DPS as DCO for PLL and DLL, 114</li> <li>5.12.2 TAF-DPS as Open-Loop Fractional Divider, 117</li> <li>5.12.3 TAF-DPS in Pulse Width Modulation, 120</li> <li>5.12.4 TAF-DPS for Message Transmission Using Spectrum, 122</li> <li>5.12.5 TAF-DPS for Message Transmission Using Duty Cycle, 122</li> <li>References, 127</li> </ul> |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 6  | TAF-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TAF-DPS Clock Generator and On-Chip Clock Distribution                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|    | 6.1<br>6.2<br>6.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Resonar<br>by TAF-<br>TAF-DF<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.3.5 | Clock Distribution at Low Frequency, 131 at Clock Distribution Network Assisted DPS, 136 PS Clock Source and FPGA, 143 FPGA Operation and Flexibility, 144 Prefabricated FPGA Structure and Clock/Frequency Distribution Requirement, 144 Heterogeneous FPGA Computing and Frequency Requirement, 145 Parallelism in FPGA and Frequency Requirement, 145 TAF-DPS Clock Source and FPGA, 145 Creating Clock Source of Sub-ppm Frequency Granularity and Two-Cycle Frequency Switching Speed with FPGA Custom Logic, 146 |  |  |  |  |

| 7  | Digital-to-Frequency Converter: A Component Enabling New<br>Application Fields                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 8  | Conclusion: Evolution of Timekeeper in Electrical World                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| In | Index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

### IMPORTANCE OF CLOCK SIGNAL IN MODERN MICROELECTRONIC SYSTEMS

# 1.1 CLOCK TECHNOLOGY: ONE OF THE FOUR FUNDAMENTAL TECHNOLOGIES IN IC DESIGN

Today's typical electronic systems contain millions of electrical signals. They make the system perform what it is designed to do. Among these, the most important one is the clock signal. From an operational perspective, the clock is the timekeeper of the electrical world in a chip/system. From a structural perspective, the clock generator is the heart of a chip; the clock pulse is the heart beat; the clock signal is the blood; and the clock distribution network is the vessel.

The timekeeper has played and is playing a critical role in human life. History shows that the progressive advancement of our civilization is only made possible by the steady refinement of the timekeeper: the clock [Fra11]. The same is true for electronic systems. The purpose of electronic systems is for processing information. The efficiency of performing this task is highly dependent on the time scale used. This time scale is controlled by the clock signal. It has two key aspects: its size (the absolute clock frequency) and its resolution (the capability of differentiating nearby frequencies; resolution can also be viewed as frequency granularity and/or time granularity). In addition, another characteristic is important in the electronic system: the speed at which the time scale can be switched from one to another (the clock frequency switching speed).

From the day of Robert Noyce [Noy61] and Jack Kirby's [Kil64] first integrated circuit in 1959 to today's systems of billions of transistors on a chip, the art of

From Frequency to Time-Average-Frequency: A Paradigm Shift in the Design of Electronic Systems, First Edition. Liming Xiu. © 2015 The Institute of Electrical and Electronics Engineers, Inc. Published 2015 by John Wiley & Sons, Inc.

integrated circuit (IC) design can be roughly individualized into three key areas: processor technology, memory technology, and analog technology. Processor technology focuses its attention on how to build efficient circuits to process information. Using transistors to do logic and arithmetic operations with high efficiency is its highest priority. Memory technology is the study of storing information in a circuit. Its aim is to store and retrieve information in large amounts and at high speed. Analog technology squares its effort at circuits that interface electrical systems with humans (or the world of physical phenomena). Inside electronic systems, information is processed in binary fashion. Once outside, information is used by us in proportional style since our five senses are built upon proportional relationships. The analog circuit is the bridge in between. During the past several decades, advancements in these three circuit technologies have made today's electronic systems very powerful. However, the driver of these three technologies, the clock, has not seen fundamental breakthroughs. The time scale is not flexible: The available clock frequencies are limited and the switching between frequencies is slow. To improve the electronic system's information processing efficiency further, the next opportunity is with the method of clocking: (1) We need a flexible on-chip clock source and (2) and it needs to be available to chip designers at a reasonable cost. Now is the time for clock to be recognized as a technology, as illustrated in Figure 1.1.

There are four key challenges in the generation of a clock signal: high clock frequency, low noise, small frequency granularity (also loosely referred to as arbitrary frequency generation), and fast frequency switching (also loosely referred to as instantaneous frequency switching). The first two have been studied intensively by researchers. The last two have not drawn much attention. Another challenge lies in distributing the generated clock signal to all the places that require a clock. Clock distribution is a difficult problem both functionally and physically. From a functional perspective, a cell requiring a driving clock might need the clock signal to come from different sources in different operating modes. The logical path from a source to any destination (clock sink) is controlled by the selector, frequency divider, and gater, as illustrated on the left in Figure 1.2. These elements ensure that a clock sink sees the appropriate clock signal at the appropriate time. From a physical point of view,

FIGURE 1.1 Clock as a technology.