# Gallium Nitride Power Devices

edited by Hongyu Yu Tianli Duan

# Published by

Pan Stanford Publishing Pte. Ltd. Penthouse Level, Suntec Tower 3 8 Temasek Boulevard Singapore 038988

Email: editorial@panstanford.com

Web: www.panstanford.com

# British Library Cataloguing-in-Publication Data

A catalogue record for this book is available from the British Library.

### **Gallium Nitride Power Devices**

Copyright © 2017 by Pan Stanford Publishing Pte. Ltd.

All rights reserved. This book, or parts thereof, may not be reproduced in any form or by any means, electronic or mechanical, including photocopying, recording or any information storage and retrieval system now known or to be invented, without written permission from the publisher.

For photocopying of material in this volume, please pay a copying fee through the Copyright Clearance Center, Inc., 222 Rosewood Drive, Danvers, MA 01923, USA. In this case permission to photocopy is not required from the publisher.

ISBN 978-981-4774-09-3 (Hardcover) ISBN 978-1-315-19662-6 (eBook)

Printed in Canada

# **Preface**

As a third-generation semiconductor, GaN has found broad technological applications in high-power devices by virtue of its high breakdown field and high electron mobility. Therefore, the development of GaN technology is regarded as important national strategic research for many countries. The industry has made phenomenal growth in GaN electronics. Moreover, many GaN-related papers have been published to report the progress in the fundamental concepts and performances of GaN devices.

To access both fundamental knowledge and advanced novel development, a book that could give information about comprehensive material physics and device structure as well as device operational principles was needed. To meet such a need, *Gallium Nitride Power Devices* was prepared. This book comprises nine chapters which discuss the growth technology of GaN wafers and the characteristics of polarization effects of GaN material and device process on device performance, reliability, and packaging. It is a textbook for undergraduate students, and it is also a reference book for graduate students as well as engineers and scientists in GaN research.

In the course of writing this book, I was fortunate to obtain the help of Wang Zhigang and Wang Bing from Southwest Jiaotong University, Cheng Kai from Enkris Semiconductor, Liu Zhihong from the Singapore-MIT Alliance for Research and Technology, and Jiang Lingli, Xia Pengkun, and Dongbin from the South University of Science and Technology of China.

Tianli Duan

# Contents

| Prefe | ice    |            |                                         | ix |

|-------|--------|------------|-----------------------------------------|----|

| 1.    | The G  | owth Te    | chnology of High-Voltage GaN on Silicon | 1  |

|       | Peng 2 | Kiang, Liy | ang Zhang, and Kai Cheng                |    |

|       | 1.1    | Introdu    | iction                                  | 1  |

|       | 1.2    | The Nu     | cleation Layer Growth                   | 6  |

|       | 1.3    |            | Engineering                             | 10 |

|       |        | 1.3.1      | The LT-Al(Ga)N Interlayer               | 10 |

|       |        | 1.3.2      | The AlGaN Buffer Layer                  | 15 |

|       |        | 1.3.3      | Al(Ga)N/GaN SLs                         | 18 |

|       | 1.4    | Leakag     | e Reduction and Breakdown Voltage       |    |

|       |        | Enhand     | cement                                  | 21 |

|       |        | 1.4.1      | Compensational Doping                   | 21 |

|       |        | 1.4.2      | Other Methods                           | 25 |

|       | 1.5    | Conclu     | sions                                   | 26 |

| 2.    | The Ch | aracteris  | stics of Polarization Effects in GaN    |    |

|       | Hetero | structur   | es                                      | 35 |

|       | Zhigai | ng Wang    |                                         |    |

|       | 2.1    | Introdu    | action                                  | 35 |

|       | 2.2    | The ab     | initio Theory in III-V Semiconductors   | 37 |

|       |        |            | Spontaneous Polarization                | 38 |

|       |        | 2.2.2      | Piezoelectric Polarization              | 39 |

|       |        | 2.2.3      | The Analytical Model of a 2DEG at the   |    |

|       |        |            | AlGaN/GaN Interface                     | 42 |

|       | 2.3    | Polariz    | ation Effects Discussion                | 43 |

| 3.    | GaN T  | ransistor  | Fabrication Process                     | 49 |

|       | Liu Zh | ihong      |                                         |    |

|       | 3.1    | Device     | Isolation                               | 51 |

|       |        | 3.1.1      | Wet Etch                                | 51 |

|       |        | 3.1.2      | Dry Etch                                | 56 |

|       |        |            | Implantation Isolation                  | 63 |

|       | 3.2    |            | Contacts                                | 67 |

|    |         | 3.2.1      | The Ti/Al/X/Au Metal Scheme           | 67  |

|----|---------|------------|---------------------------------------|-----|

|    |         | 3.2.2      | CMOS-Compatible Ohmic Contacts        | 76  |

|    | 3.3     | Gate F     | abrication                            | 77  |

|    |         | 3.3.1      | Schottky Gate                         | 78  |

|    |         | 3.3.2      | Metal-Insulator-Semiconductor Gate    | 79  |

|    | 3.4     | Surfac     | e Passivation                         | 80  |

|    | 3.5     | Field F    | Plates                                | 80  |

| 4. |         |            | AlGaN/GaN Heterojunction Field-Effect |     |

|    | Transi  | stors      |                                       | 93  |

|    | Jiang I | Lingli     |                                       |     |

|    | 4.1     | Introd     | uction                                | 93  |

|    | 4.2     | Polaria    | zation and Generation of a 2DEG       | 94  |

|    |         | 4.2.1      | Polarization                          | 94  |

|    |         | 4.2.2      | Generation of a 2DEG                  | 97  |

|    | 4.3     | GaN H      | EMT Operation Principle               | 98  |

|    | 4.4     | Break      | down for an AlGaN/GaN HEMT            | 101 |

|    |         | 4.4.1      | Gate Electric Field Plate             | 102 |

|    |         | 4.4.2      | Source Electric Field Plate           | 105 |

|    |         | 4.4.3      | Air Bridge Field Plate                | 106 |

| 5. | Origin  | al Demo    | nstration of Depletion-Mode and       |     |

|    | Enhan   | cement-    | Mode AlGaN/GaN Heterojunction         |     |

|    | Field-I | Effect Tra | ansistors                             | 111 |

|    | Zhigai  | ng Wang    | and Bing Wang                         |     |

|    | 5.1     | Introd     | uction                                | 112 |

|    | 5.2     | Develo     | opment of E-Mode AlGaN/GaN HFETs      | 113 |

|    |         | 5.2.1      | E-Mode HFET with a P-Type Cap Layer   | 114 |

|    |         | 5.2.2      | E-Mode HFET with a Recessed-Barrier   |     |

|    |         |            | Layer                                 | 114 |

|    |         | 5.2.3      | E-Mode HFET with a Double-Barrier     |     |

|    |         |            | Layer                                 | 116 |

|    |         | 5.2.4      | Metal-Insulator-Semiconductor HFET    | 119 |

|    |         | 5.2.5      | N-Polar GaN-Based E-Mode HFETs        | 121 |

|    |         | 5.2.6      | E-Mode HEMTs by Fluoride-Based        |     |

|    |         |            | Plasma Treatment                      | 122 |

|    |         | 5.2.7      | GaN-Based MOSFETs and AlGaN/GaN       |     |

|    |         |            | MOS-HFETs                             | 124 |

|    |         | 5.2.8      | Other Types of E-Mode HFETs           | 125 |

|    | 5.3     | Charge     | e Control Models                      | 126 |

|    |                      | 5.3.1     | CCM in a Heterojunction with a Single                     |     |

|----|----------------------|-----------|-----------------------------------------------------------|-----|

|    |                      |           | Barrier                                                   | 126 |

|    |                      | 5.3.2     | CCM in a Heterojunction with Double                       |     |

|    |                      |           | Barriers                                                  | 127 |

|    |                      | 5.3.3     | CCM in a Heterojunction with                              |     |

|    |                      |           | Multibarriers                                             | 129 |

|    | 5.4                  | Reliab    | ility of the Threshold Voltage                            | 132 |

|    |                      | 5.4.1     | Traps Exist in III-N Barrier Layers                       | 133 |

|    |                      | 5.4.2     | Fixed Charges Exist at the                                |     |

|    |                      |           | Dielectric/III-N Heterointerface or                       |     |

|    |                      |           | in the Dielectric                                         | 135 |

|    |                      | 5.4.3     | Dynamic Recovery of the Threshold                         |     |

|    |                      |           | Voltage Shift by Trapping Speed                           | 138 |

|    |                      | 5.4.4     | Lattice-Mismatch-Induced Reduction                        |     |

|    |                      |           | of Strain or Stress                                       | 139 |

| 6. | Surface              | e Passiv  | ation and GaN MIS-HEMTs                                   | 145 |

|    | Tianli .             | Duan ai   | nd Liu Zhihong                                            |     |

|    | 6.1                  | Introd    | uction                                                    | 145 |

|    | 6.2                  | Surfac    | e Passivation                                             | 147 |

|    | 6.3                  | Metal-    | Insulator-Semiconductor                                   |     |

|    |                      | High-E    | Electron-Mobility Transistors                             | 154 |

|    |                      | 6.3.1     | Characteristics of Various Gate                           |     |

|    |                      |           | Dielectrics                                               | 154 |

|    |                      | 6.3.2     | Atomic Layer Deposition of Al <sub>2</sub> O <sub>3</sub> | 155 |

|    |                      | 6.3.3     | Characterization of the Interface                         |     |

|    |                      |           | Traps by Traditional C-V Measurement                      | 163 |

|    |                      | 6.3.4     | Other Approaches to Measure the the                       |     |

|    |                      |           | Interface Trap Density                                    | 173 |

|    |                      |           | 6.3.4.1 Hysteresis method                                 | 173 |

|    |                      |           | 6.3.4.2 Subthreshold swing method                         | 173 |

|    |                      |           | 6.3.4.3 AC transconductance method                        | 174 |

|    |                      |           | 6.3.4.4 Photoassisted C-V                                 | 175 |

|    | 6.4                  | Summ      | ary                                                       | 176 |

| 7. | GaN Ve               | ertical P | ower Devices                                              | 193 |

|    | Liu Zhi              | ihong     |                                                           |     |

|    | 7.1                  | Introd    | uction                                                    | 193 |

|    | 7.2                  |           | ertical PN Diodes and Schottky Diodes                     | 195 |

|    | - 10 <del>-2</del> 0 | 721       | Davies Characterists                                      | 105 |

|       |                  | 7.2.2      | Design of the Vertical Diode Structures | 198 |  |

|-------|------------------|------------|-----------------------------------------|-----|--|

|       |                  | 7.2.3      | Edge Termination Technology             | 209 |  |

|       | 7.3              | Three-     | Terminal GaN Vertical Power Devices     | 217 |  |

|       |                  | 7.3.1      | Current Aperture Vertical Electronic    |     |  |

|       |                  |            | Transistors                             | 217 |  |

|       |                  | 7.3.2      | Junction Field-Effect Transistors       | 224 |  |

|       |                  | 7.3.3      | Trench Field-Effect Transistors         | 228 |  |

| 8.    | Reliab           | ility of G | GaN HEMT Devices                        | 241 |  |

|       | Pengk            | un Xia     |                                         |     |  |

|       | 8.1              | Tempe      | erature-Related Degradation             | 242 |  |

|       |                  | 8.1.1      | Degradation under Thermal Storage       | 242 |  |

|       |                  | 8.1.2      | Variation of Device Performance         |     |  |

|       |                  |            | under Different Temperatures            | 245 |  |

|       | 8.2              | Curren     | nt Collapse                             | 247 |  |

|       | 8.3 Prebreakdown |            |                                         |     |  |

|       |                  | 8.3.1      | Electric Field Peak                     | 250 |  |

|       |                  | 8.3.2      | Bulk Leakage                            | 252 |  |

|       |                  | 8.3.3      | Inverse Piezoelectric Effect            | 255 |  |

|       | 8.4              | Conclu     | usion                                   | 257 |  |

| 9.    | The Pa           | ackaging   | Technologies for GaN HEMTs              | 261 |  |

|       | Dong             | Bin        |                                         |     |  |

|       | 9.1              |            | uction                                  | 261 |  |

|       | 9.2              |            | nges and Advances in Packages for       |     |  |

| 9.    |                  | Gan HEMTs  |                                         |     |  |

|       |                  | 9.2.1      |                                         | 263 |  |

|       |                  |            | Parasitic Inductors                     | 264 |  |

|       |                  | 9.2.2      | Thermal Management                      | 265 |  |

|       |                  |            | ge Types for GaN Products               | 267 |  |

|       |                  | 9.3.1      | An Introduction to Commercialized       |     |  |

|       |                  |            | GaN Products                            | 269 |  |

|       |                  | 9.3.2      | Transistor Outline Packages             | 270 |  |

|       |                  | 9.3.3      |                                         | 274 |  |

| Index | Y                |            |                                         | 281 |  |

# Chapter 1

# The Growth Technology of High-Voltage GaN on Silicon

Peng Xiang, Liyang Zhang, and Kai Cheng

Enkris Semiconductor, Inc., Suzhou, China Peng.Xiang@enkris.com

# 1.1 Introduction

Due to the limited availability and relatively high cost of sufficiently large GaN substrates for homoepitaxial growth, GaN films are normally grown on foreign substrates, such as sapphire, SiC, and Si. Table 1.1 shows properties of III nitrides and these foreign substrates. SiC has the smallest lattice mismatch and thermal expansion coefficient (TEC) mismatch to GaN as compared to others, but the high price and limited diameter (normally  $\leq$ 6 inches) of a SiC substrate make it unaffordable for power applications. GaN-on-sapphire substrate technology is very mature and is the mainstream in the light-emitting diode (LED) market, but it is unsuitable for power applications due to the poor thermal conductivity of sapphire.

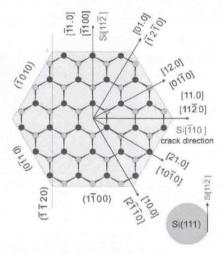

Si is the most widely used semiconductor nowadays, and using a Si substrate has many advantages over SiC and sapphire, such as a large diameter, low cost, and a ready-made process. The diameter of a Si substrate can be scaled to 12 inches, and the metal-organic chemical vapor deposition (MOCVD) reactor is available to grow 8-inch GaN epilayers on 8-inch Si substrates. In contrast, the SiC and sapphire substrate size is typically smaller than 6 inches. The cost of GaN power devices can be further reduced by using the ready-made 6- and 8-inch complementary metal-oxide-semiconductor (CMOS) process line. A Si substrate also shows high crystalline quality and minimized defect density, thanks to decades of development of the Si semiconductor industry. It has been well accepted that GaN on large-size silicon substrates is one cost-effective way to achieve high-volume production of GaN power devices. Figure 1.1 shows the epitaxial relationship of the GaN(0001) plane (c-plane) on the Si(111) plane. Usually, a Si(111) substrate is utilized for the epitaxial growth of c-plane GaN because of their same trigonal symmetry.

Table 1.1 Properties of III nitrides and substrates [1, 2]

| Ma           | iterial   | Lattice<br>param-<br>eters (Å) | Lattice<br>mismatch <sup>a</sup><br>to GaN | TEC <sup>b</sup> (10 <sup>-6</sup> K <sup>-1</sup> ) | Thermal conductivity (W/cmK) | Diameter |

|--------------|-----------|--------------------------------|--------------------------------------------|------------------------------------------------------|------------------------------|----------|

| Se           | AlN       | a = 3.112<br>c = 4.982         | 2.48%                                      | 4.2                                                  | 2.0                          | /        |

| III nitrides | InN       | a = 3.548<br>c = 5.7034        | -10.1%                                     | 5.7                                                  | 0.8                          | /        |

|              | GaN       | a = 3.1891<br>c = 5.1855       | 0                                          | 5.59                                                 | 1.3                          | /        |

| Substrates   | $Al_2O_3$ | a = 4.765<br>c = 12.982        | 13.9%<br>Rotated 30°                       | 7.5                                                  | 0.3                          | 2-6      |

|              | SiC       | a = 3.081<br>c = 15.117        | 3.51%                                      | 4.2                                                  | 4.9                          | 2-6      |

| 23           | Si        | a = 5.431                      | -17%                                       | 3.59                                                 | 1.3                          | 2-12     |

<sup>&</sup>lt;sup>a</sup>Lattice mismatch =  $(a_{GaN} - a_{eff.sub})/a_{sub}$

However, the growth of GaN on Si is challenging owing to issues such as melt-back etching and a large thermal and lattice mismatch [4]. A common problem in the growth of GaN on Si is melt-back

bTEC: Thermal expansion coefficient

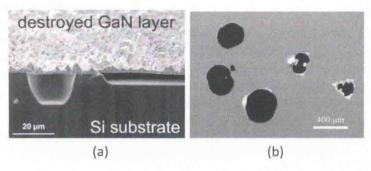

etching. The origin of melt-back etching is the alloying reaction between Ga and Si at high temperature (HT). Ga has high solubility in Si at high temperature. When Ga comes in contact with Si at high temperature, the alloy of Ga and Si forms and produces hollows and swellings on the substrate, which seriously destroys the epilayers (Fig. 1.2). Once the melt-back-etching process starts, it will expand during the following growth and cannot be stopped. Therefore it is extremely important to prevent melt-back for growing GaN on Si. Gafree layers, such as AlN, SiC [5], AlAs [6], and Al<sub>2</sub>O<sub>3</sub> [7], were employed to prevent Ga from contacting Si. Ascribed with the advantages of high thermal stability and convenience, AlN is normally used as a starting buffer layer for GaN on Si.

**Figure 1.1** Epitaxial relationship GaN(0001) on Si(111). Reprinted from Ref. [3], Copyright (2002), with permission from Elsevier.

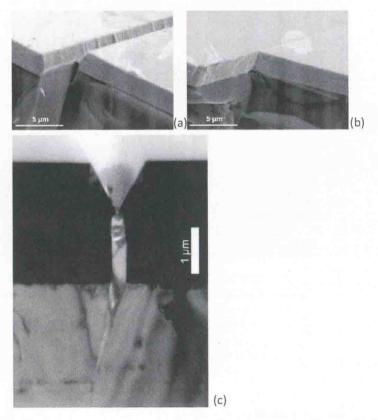

One of the biggest challenges is the large stress caused by the thermal mismatch between GaN epilayers and Si substrates. The TEC of GaN is  $5.59 \times 10^{-6} \; \text{K}^{-1}$ , which is much larger than that of Si,  $3.59 \times 10^{-6} \; \text{K}^{-1}$ . A GaN epilayer is usually grown at a high temperature of  $1000^{\circ}\text{C}$  using MOCVD. When GaN is cooling down from growth temperature to room temperature, a large tensile stress of about 1 Gpa is generated in the GaN film because the TEC of the Si substrate is significantly smaller than that of GaN. Consequently, there is a much greater risk that the GaN epilayers will crack if the thickness of GaN exceeds several hundred nanometers, as shown in Fig. 1.3. A GaN layer with a thickness of several hundred nanometers is insufficient for producing high-quality films and devices. GaN electronics on

Si can easily break down from the Si substrate because of the low critical electric field of Si. To achieve a high breakdown voltage, a film thickness of several micrometers is necessary for a GaN-on-Si power device.

**Figure 1.2** Destroyed GaN layer due to melt-back etching: (a) SEM image of a vertical view. Reprinted from Ref. [8], Copyright (2003), with permission from Elsevier. (b) Optical microscope image of a plan view.

Stress also introduces large wafer bow, which deteriorates the uniformity of the epilayer and causes failure during wafer handling and passing of the stepper in the lithography process, making the material unsuitable for device manufacturing. The wafer curvature  $\kappa$  can be obtained from the Stoney equation:

$$\kappa = \frac{6M_{\rm f}\varepsilon_{\rm m}h_{\rm f}}{M_{\rm s}h_{\rm s}^2} \tag{1.1}$$

where  $\varepsilon_{\rm m}$ ,  $M_{\rm f}$ ,  $M_{\rm S}$ ,  $h_{\rm f}$  and  $h_{\rm S}$  denote the biaxial mismatch strain, the biaxial moduli of the film, the biaxial moduli of the substrate, the thickness of the film, and the thickness of the substrate, respectively. Assuming the diameter of the substrate is D, the wafer bow can be obtained by

$$B = \frac{3M_{\rm f}D^2}{4M_{\rm s}h_{\rm s}^2}\varepsilon_{\rm m}h_{\rm f} \tag{1.2}$$

The wafer bow is proportional to the square of the substrate diameter, indicating a larger value when a large-diameter Si substrate is utilized.

To grow crack-free GaN on Si with low wafer bow, stress engineering has to be executed. Compressive stress is introduced during growth by inserting Al-rich layers such as AlN [9–13], AlGaN [14–24], and AlN/GaN superlattices (SLs) [25–29] to counterbalance

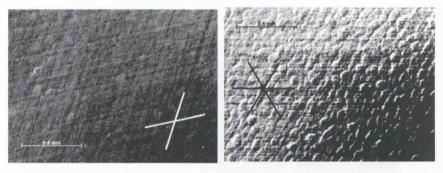

the tensile stress. Nevertheless, this compressive stress also should be carefully controlled. This compressive stress causes curvature of the wafer during growth, which will deteriorate the wafer temperature uniformity and cause plastic deformation (Fig. 1.4) if a too large curvature appears [30]. Thus stress engineering is of great importance and is challenging for the growth of a GaN-on-Si wafer.

**Figure 1.3** Two types of cracks for GaN on Si: (a) an open groove with facets occurs during growth and (b) a closed crack during cooling down; (c) cross section of an open crack. Reprinted from Ref. [3], Copyright (2002), with permission from Elsevier.

The large lattice mismatch between GaN and Si will introduce a high density of dislocations, which are usually larger than  $10^8/\text{cm}^2$ . High dislocation densities deteriorate the crystalline quality of GaN and the performance of power devices.

Apart from the large tensile stress and high dislocation density, GaN on Si has also suffered from high buffer leakage, which should be minimized for power applications. Compared to Si and GaAs,

GaN grown on a heterosubstrate is a very imperfect crystal system with a high density of defects. Usually, the density of the background donor in unintentionally doped GaN is 1016-1017/cm3 due to the existence of oxygen and silicon impurities and nitrogen vacancies, which introduces 10<sup>16</sup>-10<sup>17</sup>/cm<sup>3</sup> background electrons. Thus leakage current from the buffer layer will occur. Additionally, the Si substrate and the AlN/Si interface are conducting. A GaN buffer with a high background donor will also introduce leakage current from the Si substrate. Compositional doping [32-39] and removal of the Si substrate [40] are effective in reducing the buffer leakage and increasing the breakdown voltage of GaN on Si.

Nomarski microscope image of plastic substrate deformation for GaN-on-Si layers in two different appearances. The image on the left shows a weaker deformation, with slip lines in the Si(111) substrate only visible in two different directions (marked white), while the image on the right shows strong deformation, with slip lines propagating in all three preferred directions (marked black). Reproduced from Ref. [31] with permission from John Wiley and Sons.

# The Nucleation Layer Growth

Due to the melt-back etching phenomenon mentioned earlier, GaN cannot be directly grown on a Si substrate at high temperature. AlN [20, 41-49], SiC [5], AlAs [6], and Al<sub>2</sub>O<sub>3</sub> [7] were applied as the seeding layer for GaN grown on Si. AlN is the most universal nucleation layer that supports high-quality GaN on a Si substrate. With high thermal stability and good wettability on Si, the AlN buffer prevents the melt-back reaction and favors the subsequent growth of the GaN layer. In addition, compressive stress can be generated in GaN films grown on AlN because of the smaller lattice parameters of AlN, which can counterbalance the tensile stress when cooling down.