## Analog and Switching Circuit Design

using integrated and discrete devices

J Watson

### Analog and Switching Circuit Design

using integrated and discrete devices

J Watson University of Wales, Swansea

Adam Hilger Ltd, Bristol

### © J Watson 1984

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise without prior permission of the publisher.

British Library Cataloguing in Publication Data Watson, J.

Analog and switching circuit design using integrated and discrete devices

1. Switching circuits 2. Semiconductors

I. Title

621.3815'37

TK7868.S9

ISBN 0-85274-758-6 (hbk) ISBN 0-85274-764-0 (pbk)

Published by Adam Hilger Ltd, Techno House, Redcliffe Way, Bristol BS1 6NX

Phototypeset by Macmillan India Ltd, Bangalore and printed in Great Britain by J W Arrowsmith Ltd, Bristol

### **Preface**

Electronics is a subject of enormous diversity and depth, for which reason attempts have been made to compartmentalize the various fields of interest, whilst nevertheless recognizing the major overlaps which must occur. For example, three such divisions have been microelectronic fabrication, computer technology and communications, which have now overlapped to result in the modern major area of information technology(IT). Another form of division has been between analog and digital electronic circuit design, and these areas have now overlapped in integrated circuits which support both technologies, such as analog—digital and digital—analog converters, multiplexers, switched-capacitor filters and certain microprocessors.

At the same time, mathematical techniques have been developed<sup>(1)</sup> to describe and analyze the various functions which have been made possible by the application of modern electronic technology, particularly in the area of signals. Here, Fourier transform methods for signal analysis have been augmented by Z-transform techniques<sup>(2)</sup>, which are relevant to sampled-data systems; and the widespread availability of cheap computing power (in the form of microprocessors and random-access-memories, or RAM's) has made possible such departures as the use of the fast-Fourier-transform (FFT) for the implementation of signal processing<sup>(3)</sup>.

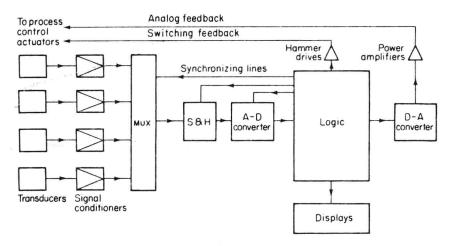

The interdependence of all these developments in both technology and analytical techniques can be observed when complete systems are considered. For example, figure P.1 shows a block diagram for an instrumentation system involving signal acquisition, processing and conversion, data manipulation and finally utilization. A case in point might be a chemical production line where a number of measurements must be made of such quantities as temperature, pressure, humidity and pH. Various forms of transducer (including semiconductor types) are used for this purpose and are represented by the blocks on the left of figure P.1. The variables are normally

Figure P. 1. A process-control instrumentation system block diagram.

continuous and the transducers respond to them in various known ways which result in output signals of diverse amplitude and impedance levels. So, it is usually necessary to employ analog techniques of signal conditioning, many of which have descended from the analog computer developments of earlier decades. The signal conditioning blocks are shown next in figure P.1.

It is now possible to sample sequentially the outputs of the bank of signal conditioners, and this is done with a multiplexer (MUX) which is essentially a solid-state switch which applies each signal to a single line in turn. In figure P.1, the MUX is shown feeding a sample-and-hold module which, as its name suggests, samples the signal appearing at the MUX output (after the inevitable switching transient is over) and holds it long enough for further processing.

In this system, analog-to-digital (A–D) conversion follows<sup>(4)</sup>, after which the digitized data can be processed in many ways. For example, though the analog signal may be filtered (if necessary) using analog techniques within the signal-conditioning module, such filtering may also be accomplished digitally after the A–D converter.

The information acquired by the transducers is now in the form of digital data which may be stored and combined according to the programming of the logic unit also shown in figure P.1. This logic may take several forms, from hard-wired combinatorial and sequential logic circuits<sup>(5)</sup> (often involving custom-interconnected uncommitted logic arrays, or ULA's in monolithic microcircuit form), to micro- or mainframe computers<sup>(6)</sup>.

Outputs to actuators may be in the form of on-off signals which can be interfaced by power transistors (hammer-drivers) to operate solenoids; or as sequences of pulses to drive stepper motors; or they may appear again in analog form via D-A converters<sup>(4)</sup>.

PREFACE XIII

Finally, a whole family of solid-state and other displays may be operated via appropriate microcircuit interfacers and drivers.

This system is but one example of the complexity and breadth of modern electronics, and serves to show that to gain an understanding of it implies that a number of texts must be studied in parallel, for no one book of reasonable size can treat more than a small part of the subject in other than a trivial manner. The aim of the present volume is to introduce a selection of contemporary semiconductor devices and integrated circuit structures and, through an understanding of their operation and characteristics, establish the basic tenets of analog and low-power switching design which will lead to the realization of useful and economical circuits.

Parallel reading should therefore include material on digital logic (5), in which there is already a plethora (perhaps even a surfeit) of excellent works, and also on highfrequency topics such as are necessary in transmitter-receiver design<sup>(7)</sup>. A natural follow-up would then be the immensely important field of computer-aided-design, or CAD. Computer techniques, programs (such as SPICE) and models(8) are invaluable for optimizing a design, determining sensitivity to parameter changes, taking account of tolerances and laying out interconnection schemes for complex networks from printed boards to very large scale integrated (VLSI)(9) circuits. But before such powerful tools can be used the basic circuit configuration must have been created by a designer, who must therefore know what devices and integrated structures are appropriate and how they may be combined to perform the tasks in hand. It is hoped that the present book will form an introduction to this latter body of knowledge insofar as analog and low-power switching circuits are concerned, and will be useful in the early years of university courses as a practical complement to analytical material<sup>†</sup>, and so that the necessarily heavy emphasis on digital methods does not lead to the obscuration of semiconductor devices and structures other than gates and memory cells. It is for these reasons that the mathematical level is limited to presuppose only a knowledge of elementary calculus; and given a basic prerequisite of circuit theory, the book will be found to be complete within itself.

Chapter 1 offers an introduction to some of the most common semiconductor devices from a circuit-oriented viewpoint and chapter 2 introduces the solid-state physics which explains their electrical characteristics. This has been done at a very elementary level, and largely qualitatively and other texts should be consulted when a deeper understanding of semiconductor physics and technology becomes necessary<sup>(10,11)</sup>. Chapter 2 concludes with further notes on transistor characterization and introduces the concept of the *equivalent circuit* and *modelling*.

Chapter 3 shows how incremental changes in transistor operating conditions can lead to parameters which describe the *small-signal performance* of amplifier stages and chapter 4 establishes methods of *biasing* which place and maintain a transistor into an operating condition which makes these small-signal parameters valid.

<sup>†</sup> As Horowitz and Hill point out in their preface to *The Art of Electronics*, 'there is a tendency among textbook writers to represent the theory, rather than the art, of electronics'.

XIV PREFACE

Chapter 5 extends the work on amplifier stages to include frequency response and feedback, and then goes on to introduce the *difference stage*, initially as a DC amplifier. The major advantages of monolithic integrated circuit realization of such stages are presented, and new basic circuit elements are introduced which depend upon the close matching made possible by IC techniques, such as the *current mirror*. The chapter concludes by combining the difference stage and current mirror to demonstrate how the monolithic transconductance multiplier becomes possible.

Chapter 6 (which may be omitted on a first reading) is concerned solely with the question of electrical noise, and presents concepts which are used in the design of low-noise amplifiers, and which are also met in later chapters.

Chapter 7 is entirely devoted to integrated circuits, mainly in their analog manifestations. It has been rightly pointed out† that, 'To make the most of a chip, you have to understand what goes on inside, particularly with circuits which are very flexible—they're not just black boxes', and this sentiment is followed throughout the chapter insofar as bipolar structures are concerned.

Chapter 8 introduces frequency-dependent circuits from a hardware-oriented viewpoint, and it is here where further parallel reading is necessary, for topics relating to filters, oscillators and waveform generators require not only specialized treatment, but an understanding of mathematical techniques outside the scope of this volume<sup>(1)</sup>.

The design of power amplifiers is treated in chapter 9 and switching topics (other than logic) are presented in chapter 10 for bipolar structures.

Discrete and ic field-effect devices are described in chapter 11, and comparisons between bipolar, Bifet and Bimos operational amplifiers are highlighted. The chapter concludes with introductions to modern insulated-gate developments including charge-coupled-devices (CCD's) and power-FET's.

The family of switching devices from unijunction transistors to triacs is introduced in chapter 12 and some of the increasingly important range of semiconductor transducers are described in chapter 13.

Finally, chapter 14 is devoted to the mains or battery power supplies which are necessary for the operation of all semiconductor circuits.

The book concludes with appendices which clarify certain points in the text and a series of minor problems is included which serve largely to illustrate elementary design procedures.

#### J Watson

January 1983

<sup>†</sup> By Paul Brokaw of Analog Devices Inc., quoted in EDN, May 20th 1979, p.52.

#### REFERENCES

- 1. Bird G J A 1980 Design of Continuous and Digital Electronic Systems (New York: McGraw-Hill)

- Lynn P A 1982 An Introduction to the Analysis and Processing of Signals (London: Macmillan)

- 3. Brigham E 1974 The Fast Fourier Transform (Englewood Cliffs, NJ: Prentice-Hall)

- 4. Seitzer D, Pretzl G and Hamdy N A 1983 Electronic Analog-to-Digital Converters (New York: John Wiley)

- 5. Lee S C 1976 Digital Circuits and Logic Design (Englewood Cliffs, NJ: Prentice-Hall)

- Sloan M 1980 Introduction to Minicomputers and Microcomputers (New York: Addison-Wesley)

- 7. Roddy D and Coolen J 1981 Electronic Communications (Reston, VA: Reston)

- 8. Getreu I 1976 Modelling the Bipolar Transistor (Tektronix)

- Mead C and Conway L 1980 An Introduction to VLSI Systems (New York: Addison-Wesley)

- Bar-Lev A 1979 Semiconductors and Electronic Devices (Englewood Cliffs, NJ: Prentice-Hall)

- Morgan D V and Board.K 1983 An Introduction to Semiconductor Microtechnology (New York: Wiley)

#### **ACKNOWLEDGEMENTS**

I am indebted to Miss S Morgan for part of the typing of the manuscript; to colleagues K Board and A Hooper for advice on solid state technology and power electronics; to W A Evans for numerous technical discussions on various topics including multipliers; and to my wife Margaret for more typing, more computing and more tea and sympathy!

### **Symbols**

| A                                | Voltage gain of a 'perfect' | $C_{ds}$                          | Drain-source capacitance   |

|----------------------------------|-----------------------------|-----------------------------------|----------------------------|

|                                  | amplifier                   | $C_{\rm gd}$ (or $C_{\rm rss}$ )  | Gate-drain capacitance     |

| $A_i$                            | Current gain                | $C_{gs}$                          | Gate-source capacitance    |

| $A_{i(FB)}$                      | Current gain with feedback  | $C_{iss}(or G_{gss})$             | Input capacitance of FET   |

| $A_{ov}$                         | Voltage gain measured       | 5001                              | with output short-         |

| (40.4)                           | from a Thévenin input       |                                   | circuited to AC (CS mode)  |

|                                  | generator                   | $C_{\rm oss}$ (or $C_{\rm dss}$ ) | Output capacitance of      |

| $A_{\text{ov(FB)}}$              | Voltage gain, with          | OSS ( dss /                       | FET with input short-      |

| ov(FB)                           | feedback, measured from     |                                   | circuited to AC (cs mode)  |

|                                  | a Thévenin input            | CMR                               | Common mode rejection      |

|                                  | generator                   | CMR                               | ratio                      |

| .4                               | Terminal voltage gain       |                                   | Tatio                      |

| $A_{\rm v}$                      | Common-mode voltage         | D*                                | Detectivity                |

| $A_{v(CM)}$                      | gain                        | _                                 | Detectivity                |

| $A_{v(FB)}$                      | Terminal voltage gain with  | $E_{\rm e}$                       | Irradiance                 |

| 1(1.2)                           | feedback                    | $E_{os}$                          | Direct component of offset |

| Ď                                | F 15 1 6 18                 |                                   | voltage                    |

| В                                | Feedback fraction           | $E_{\mathbf{v}}$                  | Illuminance                |

| В                                | Flux density                | e                                 | Voltage generated by a     |

| $B_{\rm sat}$                    | Saturation flux density     |                                   | 'perfect' voltage source   |

| b                                | Transport factor,           | eos                               | Total offset voltage       |

|                                  | device constant             | - 05                              | ,                          |

| $C_{c}$                          | Coupling capacitor          | F                                 | Goin bondwidth and         |

| C <sub>C</sub><br>C <sub>E</sub> | Emitter bypass capacitor    | $F_{T}$                           | Gain-bandwidth product     |

|                                  | Base-collector              | J<br>C                            | Frequency                  |

| Cbc                              | _                           | $f_{H}$                           | High-frequency cut-off     |

| C                                | capacitance hybrid $\pi$    | La.                               | point                      |

| $C_{\mathrm{be}}$                | Base-emitter parameters     | $f_{L}$                           | Low-frequency cut-off      |

|                                  | capacitance J               |                                   | point                      |

|                                  |                             |                                   |                            |

| $f_{m}$                                                | A frequency near the                                 | $I_Q$                 | Quiescent collector (or                                                |

|--------------------------------------------------------|------------------------------------------------------|-----------------------|------------------------------------------------------------------------|

| r                                                      | middle of a pass-band<br>Frequency at which the      | $I_{\mathbf{z}}$      | drain) current<br>Current through Zener                                |

| $f_1$                                                  | gain is unity                                        | 1 Z                   | diode                                                                  |

| $\Delta f$                                             | Equivalent noise bandwidth                           | Io                    | Reverse leakage current of a diode                                     |

|                                                        |                                                      | i <sub>b</sub>        | Incremental base current                                               |

| $g_{\mathrm{fs}}$ $g_{\mathrm{fso}}$                   | Transconductance of a FET $g_{fs}$ when $V_{GS} = 0$ | $i_{b^+}i_{b^+}$      | Bias currents at inverting<br>and non-inverting inputs<br>respectively |

| $g_{\mathrm{m}}$                                       | Transconductance of a bipolar transistor             | ic                    | Incremental collector current                                          |

| ***                                                    | Magneticine Coros                                    | i <sub>d</sub>        | Incremental drain current                                              |

| H<br>L                                                 | Magnetizing force                                    | i <sub>d</sub>        | Offset current $(i_{\bar{b}} - i_{\bar{b}})$                           |

| $h_{\mathrm{FB}}$                                      | Common-base direct current gain                      | i <sub>e</sub>        | Incremental emitter current                                            |

| $h_{FC}$                                               | Common-collector direct                              | $i_{\ell}$            | Incremental feedback<br>current                                        |

| 1.                                                     | current gain                                         | i <sub>in</sub>       | Incremental input current                                              |

| $h_{FE}$                                               | Common-emitter direct<br>current gain                | is                    | Incremental source current                                             |

| $h_{FE(O)}$                                            | CE current gain immediately available                | K                     | Bias stability factor                                                  |

| $h_{fb}$                                               | Common-base incremental current gain                 | k                     | $.\partial I_{\rm C}/\partial I_{\rm CEO}$<br>Boltzmann's constant     |

| $h_{\mathrm{fc}}$                                      | Common-collector incremental current gain            | $L_v$                 | Luminance                                                              |

| h <sub>fe</sub>                                        | Common-emitter incremental current gain              | $M_{_{\mathrm{v}}}$   | Luminous exitance                                                      |

| $\begin{pmatrix} h_{\rm f} \\ h_{\rm i} \end{pmatrix}$ |                                                      | NEP                   | Noise equivalent power                                                 |

| $\begin{pmatrix} h_o \end{pmatrix}$                    | h-parameters                                         | NF                    | Noise factor                                                           |

| $h_{\tau}$                                             |                                                      | n                     | B                                                                      |

| $I_{\mathrm{B}}$                                       | Direct base current                                  | $P_{\rm C}$           | Power dissipated at collector junction                                 |

| I <sub>C</sub>                                         | Direct collector current                             | $P_{L}$               | Full load power                                                        |

| $I_{\text{CBO}}$                                       | Collector-base leakage<br>current with emitter       | $P_{\rm S}^{\rm L}$   | Power extracted from supply at full load                               |

|                                                        | open-circuited                                       | Pdiss                 | Power dissipated within a                                              |

| $I_{\text{CEO}}$                                       | Collector-emitter leakage<br>current with base open- | $P_{\text{diss(FL)}}$ | transistor Power dissipated under                                      |

| $I_{D}$                                                | circuited Direct drain current                       | 3/3/1 E/              | conditions of maximum sinusoidal signal                                |

| I <sub>DSS</sub>                                       | Drain current when                                   | $P_{\rm diss(m)}$     | Maximum power                                                          |

| DSS                                                    | $V_{\rm GS}=0$                                       |                       | dissipation possible                                                   |

| $I_{\rm E}$                                            | Direct emitter current                               | $P_{\rm diss(Q)}$     | Power dissipation under                                                |

| $I_{\mathbf{G}}$                                       | Direct gate current                                  |                       | quiescent (no signal)                                                  |

| $I_{P}$                                                | Photo-current                                        |                       | conditions                                                             |

### SYMBOLS

| $P_{\text{tot}}$                 | Maximum allowed power dissipation within a transistor      | $r_{ds}$                       | Incremental channel resistance of a FET                      |

|----------------------------------|------------------------------------------------------------|--------------------------------|--------------------------------------------------------------|

|                                  | transistor                                                 | S                              | Bias stability factor                                        |

| Q                                | Selectivity                                                |                                | ∂I <sub>C</sub> /∂I <sub>CBO</sub>                           |

| q                                | Charge on an electron                                      | $S_{L}$ $S_{T}$                | Load stability factor Temperature stability factor           |

| $R_{\rm B}$                      | Base resistor                                              | $S_{\mathbf{v}}$               | Tennafor stabil                                              |

| $R_{BP}$                         | Parallel combination of R <sub>in</sub> and bias resistors | <b>V</b>                       | ization factor plies                                         |

| $R_{\rm C}$                      | Co lector resistor                                         | T                              | Temperature                                                  |

| $R_{\rm CS}$ (or $R_{\rm CES}$ ) | Collector saturation                                       | $T_{ m amb}$                   | Ambient temperature                                          |

|                                  | resistance                                                 | $T_{\rm j}$                    | Junction temperature                                         |

| $R_{E}$                          | Emitter resistor                                           | toff                           | OFF-time                                                     |

| $R_{\rm F}$                      | Feedback resistor                                          | ton                            | on-time                                                      |

| $R_{\rm G}$                      | Total resistance external to                               | t <sub>d</sub>                 | Delay time                                                   |

| _                                | an input point                                             | $t_{f}$                        | Fall time                                                    |

| $R_{\rm L}$                      | Load resistance                                            | $t_{\mathbf{r}}$ :             | Rise time                                                    |

| $R_{\rm D}$                      | Drain resistor for a FET                                   | $t_{s}$                        | Storage time                                                 |

| $R_{\rm S}$                      | Source resistor for a FET                                  | 4.5                            | No.                                                          |

| $R_{\rm X}$                      | Long-tail resistor                                         | $V_{\rm B}$                    | Bias voltage at base or gate                                 |

| $R_{g}$                          | Generator internal                                         |                                | w.r.t. common line                                           |

| $R_{\rm in}$                     | resistance Input resistance of active device               | $V_{BB}$                       | Voltage across the 'bases'<br>of a unijunction<br>transistor |

| $R_{in(CM)}^-$                   | Common-mode resistances                                    | $V_{ m BE}$                    | Direct base-emitter voltage                                  |

| • }                              | at inverting and non-<br>inverting inputs                  | $V_{\rm C}^{\rm BE}$           | Voltage at collector w.r.t.                                  |

| $R_{\text{in}(CM)}^+$            | respectively                                               | $V_{CB}$                       | Direct collector-base                                        |

| $R_{in(FB)}$                     | Input resistance with                                      | , Св                           | voltage                                                      |

| in(FB)                           | feedback                                                   | $V_{\rm CC}$ , $V_{\rm DD}$ or |                                                              |

| $R_{\rm ni}$                     | Noise current resistance                                   | $V_{\rm EE}$                   | Direct voltage supply                                        |

| R                                | Noise voltage resistance                                   | $V_{CE}$                       | Direct collector-emitter                                     |

| Rout                             | Output resistance of active                                | CL                             | voltage                                                      |

| R <sub>out(FB)</sub>             | device Output resistance with                              | $V_{CE(m)}$                    | Maximum designed collector-emitter voltage                   |

| out(FB)                          | feedback                                                   | $V_{CEM}$                      | Maximum allowed .                                            |

| $r_{\rm DS}$                     | DC or chord channel                                        | **                             | collector-emitter voltage                                    |

|                                  | resistance of a FET                                        | $V_{\rm CES}$                  | Collector-emitter                                            |

| r <sub>DS(ON)</sub>              | $r_{\rm DS}$ when $V_{\rm GS} = 0$                         | **                             | saturation voltage                                           |

| $r_{\rm Z}$                      | Incremental resistance of a                                | $V_{\rm DS}$                   | Direct drain-source voltage                                  |

|                                  | Zener diode                                                | $V_{E}$                        | Voltage at emitter w.r.t.                                    |

| r <sub>bb</sub>                  |                                                            | 17                             | common line                                                  |

| r <sub>brc</sub>                 | Hubrid # parameters                                        | $V_{\rm EB}$                   | Direct emitter-base voltage                                  |

| r <sub>b'e</sub>                 | Hybrid-π parameters                                        | $V_{\rm GD}$                   | Direct gate-drain voltage                                    |

| $r_{ce}$                         |                                                            | $V_{GS}$                       | Direct gate-source voltage                                   |

| $V_{ m GS(th)}$ $V_{ m GSQ}$ $V_{ m P}$ $V_{ m Q}$ | Threshold voltage of IGFET Quiescent gate-source voltage Pinch-off voltage Quiescent collector-emitter (or drain-source) voltage kT/q (taken as 26 mV at | $egin{array}{ll} Z_{\mathrm{F}} & & & \\ Z_{\mathrm{in}} & & & \\ Z_{\mathrm{in}(\mathrm{FB})} & & & \\ Z_{\mathrm{out}} & & & \\ Z_{\mathrm{out}(\mathrm{FB})} & & & \end{array}$ | Feedback impedance Input impedance with feedback Output impedance Output impedance with feedback |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| . 4                                                | 25 °C)                                                                                                                                                   |                                                                                                                                                                                    |                                                                                                  |

| $V_{\mathbf{Z}}$                                   | Zener voltage                                                                                                                                            | $\bar{e}_{\rm n}$                                                                                                                                                                  | Spot noise voltage referred                                                                      |

| $V_{\rm c}$                                        | Control voltage for                                                                                                                                      | 7                                                                                                                                                                                  | to input                                                                                         |

| $v_{ m be}$                                        | chopper or analog gate Incremental base-emitter                                                                                                          | $\overline{i}_{n}$                                                                                                                                                                 | Spot noise current referred to input                                                             |

| be                                                 | voltage                                                                                                                                                  | $\bar{\alpha}, \bar{\alpha}', \bar{\alpha}''$                                                                                                                                      | Direct current gain for                                                                          |

| $v_{cb}$                                           | Incremental collector-base                                                                                                                               |                                                                                                                                                                                    | CB, CE, and CC modes                                                                             |

|                                                    | voltage                                                                                                                                                  | α, α', α"                                                                                                                                                                          | Incremental current gain                                                                         |

| $v_{ce}$                                           | Incremental collector-<br>emitter voltage                                                                                                                |                                                                                                                                                                                    | for CB, CE and CC modes                                                                          |

| v <sub>ds</sub>                                    | Incremental drain-source voltage                                                                                                                         | β                                                                                                                                                                                  | Incremental current gain for CE mode                                                             |

| $v_{ m eb}$                                        | Incremental emitter-base voltage                                                                                                                         | $\overline{\beta}$                                                                                                                                                                 | Direct current gain for CE mode                                                                  |

| $v_{\rm gd}$                                       | Incremental gate-drain                                                                                                                                   |                                                                                                                                                                                    |                                                                                                  |

|                                                    | voltage                                                                                                                                                  | γ                                                                                                                                                                                  | Emitter efficiency                                                                               |

| $v_{\rm gs}$                                       | Incremental gate-source voltage                                                                                                                          | γ                                                                                                                                                                                  | Correlation coefficient                                                                          |

| $v_{\rm in}$                                       | Incremental input voltage                                                                                                                                | η                                                                                                                                                                                  | Intrinsic stand-off ratio for                                                                    |

| $v_{in(CM)}$                                       | Common-mode input voltage                                                                                                                                |                                                                                                                                                                                    | a unijunction transistor                                                                         |

| $v_{\rm in(ECM)}$                                  | Common-mode error                                                                                                                                        | $\theta$                                                                                                                                                                           | Thermal resistance                                                                               |

|                                                    | voltage                                                                                                                                                  | Φ                                                                                                                                                                                  | Total flux                                                                                       |

| $v_{\rm no}$                                       | Incremental noise output voltage                                                                                                                         | φ                                                                                                                                                                                  | Phase angle                                                                                      |

| $v_{\rm ni}$                                       | Incremental noise input voltage                                                                                                                          | $\tau_c$                                                                                                                                                                           | Collector time factor                                                                            |

| $v_{ m out}$                                       | Incremental output voltage                                                                                                                               | Tco                                                                                                                                                                                | Collector time factor measured at $V_{CB} = 0$ charge control para-                              |

| $W_{\rm c}$                                        | Work function                                                                                                                                            | $\tau_{\rm s}$                                                                                                                                                                     | Saturation time meters                                                                           |

| $W_{\rm g}$                                        | Energy gap                                                                                                                                               | 3                                                                                                                                                                                  | factor                                                                                           |

### Contents

|   | Symbols                                                              | vii |

|---|----------------------------------------------------------------------|-----|

|   | Preface                                                              | xi  |

| 1 | Semiconductor devices and integrated circuits                        | 1   |

| 2 | Physical principles and DC characteristics of diodes and transistors | 10  |

| 3 | Small-signal parameters and equivalent circuits                      | 32  |

| 4 | The transistor as an amplifier                                       | 49  |

| 5 | Circuit design and performance.                                      | 74  |

| 6 | Noise                                                                | 142 |

| 7 | Operational amplifiers and other microcircuits                       | 169 |

| 8 | Frequency dependent circuits                                         | 249 |

| 9 | Power amplifiers                                                     | 274 |

| 0 | The bipolar transistor as a switch                                   | 319 |

| 1 | The field-effect transistor—discrete and integrated                  | 376 |

| 2 | Triggers, thyristors and triacs.                                     | 448 |

| 3 | Semiconductor transducers                                            | 479 |

| 4 | Power supplies                                                       | 532 |

|   | Appendix I Decibels and roll-offs                                    | 564 |

|   | Appendix II Four-pole parameters                                     | 571 |

|   | Appendix III Noise bandwidth and noise factor minimization           | 574 |

|   | Appendix IV Problems                                                 | 578 |

|   | Solutions                                                            | 596 |

|   | Index                                                                | 598 |

|   |                                                                      |     |

# 1 Semiconductor devices and integrated circuits

In electronic design, components are divided into two classes, active and passive, and for both analysis and design purposes these are represented by equivalent circuits or models. If such an equivalent circuit contains one or more voltage and/or current generators, an active device is being modelled. Otherwise, a passive device is involved. This means that diodes and transistors count as active devices, whereas resistors, capacitors and inductors do not. The derivation and use of such models will be treated extensively in this volume.

Like individual resistors and capacitors, diodes and transistors are available as discrete (i.e. individually packaged) devices; or they may appear within microcircuits as multiple structures. The term 'microcircuit' is used to encompass both monolithic and hybrid integrated circuits (ic), and these terms will be further explained in later chapters. For the present, it will suffice to note that many thousands of active structures can be diffused into a single-crystal chip of silicon, and that this technology has made possible such developments as the microprocessor, the various forms of semiconductor memory and the uncommitted logic array (ULA). Further, when combined with the capability of depositing resistor and capacitor structures, self-contained ic such as compensated operational amplifiers become possible, and these are treated at length in chapter 7.

In order to understand how electronic circuits may be designed to fulfil specific functions it is necessary to have a grasp of the properties of the individual ic and other components. For purely digital design this implies an understanding of both the hardware and software of the relevant logic, and of the heirarchy of programming where microprocessors and their associated memories are involved. Conversely, in

real-world situations it is found that phenomena which it is desired to measure, and so convert to data, are almost invariably analog in nature; and very often the utilisation of such data for control purposes necessitates an analog approach, so that a thorough understanding of basic circuit design becomes necessary. This may be most easily acquired by first listing the family of semiconductor devices available (several of which appear as multiple structures within integrated circuits) and proceeding to consider both their properties and the basic (qualitative) physics of their operation. Their use in circuits can then be treated in detail.

#### SEMICONDUCTOR DEVICES

- (i) The diode. Available in discrete form, as multiple arrays and within ic. The basic attribute is that of rectification but it also has applications as a voltage reference (Zener diode) and in the detection and measurement of radiation, including light.

- (ii) The bipolar transistor. Also available in discrete form and within ic. Can perform almost all electronic functions including amplification and switching, and can act as a constant-current source and a transducer.

- (iii) The field-effect transistor. Again available individually or within some microcircuits and can provide amplification and switching. Can also be used as a voltage-controlled resistor (VCR), constant-current source (or current limiter (CL)) and as a transducer.

- (iv) Four-layer devices. The family of Shockley diodes, thyristors and triacs which are essentially controllable switches. Most, but not all, can only be turned on (but not off) using a third electrode and so are normally found as discrete power control devices involving AC supplies.

Less important structures are also available and will be treated in the course of the text. Meanwhile, the basic properties of the foregoing list will be presented.

### DIODES AND ZENER DIODES

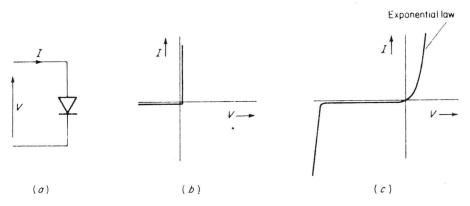

Figure 1.1(a) shows the symbol for a rectifier, or diode, while figure 1.1(b) illustrates an idealized electrical characteristic for the device.

When a forward voltage is applied, the resistance of the diode would ideally be zero and a forward current would flow (in the direction of the arrow in the diode symbol) which would be limited only by the external circuitry. On the other hand, the resistance of the diode would be infinite for a reverse voltage and no current would flow.

This ideal situation cannot be realized, however, and the characteristic of a practical diode is as shown in figure 1.1(c). Here, the application of a forward voltage produces a current which is an exponential function of that voltage. Conversely, a

**Figure 1.1.** The diode: (a) diode symbol and polarities; (b) ideal diode characteristics; (c) practical diode characteristics.

reverse voltage results in a small reverse leakage current which is largely a function of temperature.

These non-ideal characteristics imply that power is dissipated in a diode. For example, a diode passing 1 A of forward current would, typically, drop about 0.6 V, so that the device would have to be capable of dissipating a power of 0.6 W in the form of heat. If it were not capable of doing this at a temperature below its rated maximum then it would catastrophically fail. For this reason, the ambient temperature is clearly a deciding factor in the power rating of a diode.

'When a reverse voltage is applied, there appears, in addition to the small leakage current, a capacitance which is an inverse function of this voltage. Consequently, the diode can be used as a voltage-variable capacitor or *varactor*. Such diodes are used in high-frequency work for tuning purposes and, less commonly, in parametric amplifiers down to zero frequency.

Also shown in figure 1.1(c) is a sharp rise in reverse current when the reverse voltage reaches the *breakdown* level. This breakdown is due to both tunnelling and avalanche effects (both discussed later in the text) and may result in irreversible damage unless the current is limited by the external circuitry.

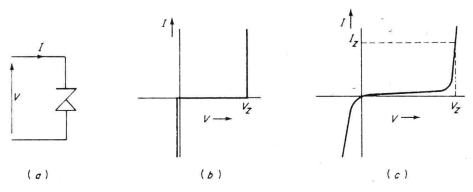

Non-destructive breakdown is also possible and is utilized in the Zener diode. The symbol used in this book is illustrated in figure 1.2(a), while diagrams (b) and (c) give idealized and attainable characteristics respectively. From these characteristics it will be seen that the Zener diode is, from a circuitry point of view, essentially a normal diode operated beyond breakdown, that is, in the reverse-current quadrant. (Note that in the relevant symbol, the arrow still points in the direction of forward current, for reasons of consistency.)

Ideally, the Zener diode would present zero resistance after breakdown so defining a precise voltage irrespective of current level, as is implied by figure 1.2(b). The

Figure 1.2. The Zener diode: (a) Zener diode symbol and polarities; (b) ideal Zener diode characteristic; (c) practical Zener diode characteristic.

attainable characteristic, however, shows that a small but finite breakdown resistance appears, so that it becomes necessary for the Zener voltage  $V_Z$  to be defined at a specified Zener current  $I_Z$ . Deviations from this current will then result in voltage variations, as is described in chapter 14. If the incremental resistance is small, however, the power dissipated will approximate to  $V_ZI$ . Hence, for a family of Zener diodes of a given physical size, the maximum permissible current will be inversely proportional to  $V_Z$ .

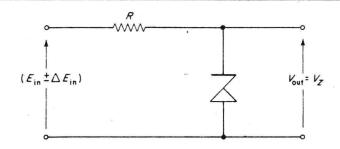

Whereas the normal diode is used as a rectifier, the basic application of the Zener diode is as a voltage reference device. Figure 1.3 shows how a direct but variable voltage may be applied to a resistor in series with a Zener diode so that  $V_{\rm Z}$  appears as a well regulated reference voltage. However, in both cases, the current must be regulated by external means, which is not necessarily so for the transistor, which has a third, or control electrode.

Figure 1.3. Zener diode voltage reference.