# COMPUTER CIRCUIT ANALYSIS

THEORY AND APPLICATIONS

FRANK A.ILARDI

# COMPUTER CIRCUIT ANALYSIS

Theory and Applications

FRANK A. ILARDI

Technical Career Institutes

Library of Congress Cataloging in Publication Data

ILARDI, FRANK A. date

Computer circuit analysis.

1. Electronic digital computers—Circuits. 2. Logic circuits. 3. Pulse circuits. 1. Title.

TK7888.4.14 621.3819'58'35 75-26529

ISBN 0-13-165357-1

To my sons Frank B., MICHAEL, and STEVEN

© 1976 by Prentice-Hall, Inc. Englewood Cliffs, New Jersey

All rights reserved. No part of this book may be reproduced in any form or by any means without permission in writing from the publisher.

10 9 8 7 6 5 4 3 2

Printed in the United States of America

PRENTICE-HALL INTERNATIONAL, INC., London PRENTICE-HALL OF AUSTRALIA, PTY. LIMITED, Sydney PRENTICE-HALL OF CANADA, LTD., Toronto PRENTICE-HALL OF INDIA PRIVATE LIMITED, New Delhi PRENTICE-HALL OF JAPAN, INC., Tokyo PRENTICE-HALL, OF SOUTHEAST ASIA PTE. LTD., Singapore WHITEHALL BOOKS LIMITED, Wellington, New Zealand

# COMPUTER CIRCUIT ANALYSIS

## **PREFACE**

This book was written after extensive discussions with representatives of the electronic industry. These people, who do the hiring for their firms, said they look for technical school graduates with good knowledge of electronics fundamentals. They feel that they can then teach them their particular system. It was noted that when these representatives interviewed prospective graduates, they tested them on their understanding of circuit theory similar to that included in this text.

This book evolved from classroom lecture notes used in courses in pulse and digital circuits at Technical Career Institutes (formerly RCA Institutes). These courses were highly successful in training students for employment with nearly every company in the electronics industry.

The first three chapters are included in this book because in some schools much of this material is not taught until the courses in pulse and digital circuits are given. To learn these subjects, a thorough understanding of network theory, semiconductor switching devices, and computer math and logic is essential. These chapters can be used by students studying the abovementioned topics for the first time or as an excellent review by those who have had courses covering this material.

The various circuits used in computers are discussed in Chapters 4 through 11. Chapter 12 is included to answer questions that have so often been asked by students of the author: How are these circuits used? How are they packaged? What determines the number of circuits that can be included in an integrated-circuit package?

The material presented in this book should also be of great value to

anyone already working in the electronics field. Because of the information covered in the first three chapters, a good background in electronics fundamentals is the only prerequisite to the use of this book. The most modern pulse and digital circuits are discussed, both a qualitative and a quantitative analysis is presented.

The author wishes to thank Sprague Electric Company, Fairchild Semiconductor, Signetics Corp., and Texas Instruments, Inc. for their cooperation. The information provided by these companies allowed the most

up-to-date material to be included in this text.

Special thanks is given to Mr. William Brecher (Instructor, Computer Department, Technical Career Institutes) from whom the author learned a great deal about computers, and to Jacqueline Ilardi who typed the manuscript and helped with other details.

FRANK A. ILARDI

# **CONTENTS**

|   | PREFACE                         |                                                                                                                                                                                                                                     |    |

|---|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1 | NETWORK ANALYSIS                |                                                                                                                                                                                                                                     |    |

|   | 1-2<br>1-3<br>1-4<br>1-5<br>1-6 | Thévenin's Theorem, 1 Norton's Theorem, 7 Thévenin to Norton and Norton to Thévenin Conversion, 10 Millman's Theorem, 12 Transient Response of RC Circuits, 16 RC Circuits with Step Function Voltage Inputs, 24 RC Attenuators, 29 |    |

| 2 | 2-1<br>2-2<br>2-3<br>2-4<br>2-5 |                                                                                                                                                                                                                                     | 33 |

|   |                                 | Nonsaturating Techniques, 62                                                                                                                                                                                                        |    |

2-9 Field Effect Transistors (FETs), 68

|   |                                                             | The FET as a Switch, 76 Summary, 77                                                                                                                                                                                                                                                                                                                                                                                |     |

|---|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3 | COM                                                         | APUTER MATH AND LOGIC                                                                                                                                                                                                                                                                                                                                                                                              | 83  |

|   | 3-3<br>3-4<br>3-5<br>3-6                                    | Number Systems, 84 Conversion Techniques, 86 Binary Arithmetic, 93 Complements, 98 Decimal Codes, 102 Boolean Algebra, 106 Basic Logical Design, 116 NAND, NOR, INHIBIT, and IMPLICATION Gates, 121 Summary, 124                                                                                                                                                                                                   |     |

| 4 | DIO                                                         | DE LOGIC                                                                                                                                                                                                                                                                                                                                                                                                           | 128 |

|   | 4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-8<br>4-9 | Static Analysis of Diode AND Gates, 128 A Practical Diode AND Gate, 131 Transient Analysis of AND Gates, 136 Static Analysis of Diode OR Gates, 139 A Practical Diode OR Gate, 142 Transient Analysis of OR Gates, 145 Static Analysis of Cascaded Diode Gates, 148 Level Shifting, 149 Transient Analysis of Cascaded Diode Gates, 150 Appendix 4-A: AND Gate Rise Time, 153 Appendix 4-B: OR Gate Fall Time, 154 |     |

| 5 | THE                                                         | INVERTER (NOT Gate)                                                                                                                                                                                                                                                                                                                                                                                                | 159 |

|   | 5-1<br>5-2<br>5-3                                           | The Basic Inverter, 159 Steady-state Analysis of the Basic Inverter, 161 A Saturation Mode Inverter with Collector Clamping, 165                                                                                                                                                                                                                                                                                   |     |

|   | 5-4                                                         | The Load (FAN-IN, FAN-OUT, and the UNIT LOAD Concept), 167                                                                                                                                                                                                                                                                                                                                                         |     |

|   | 5-5                                                         | Dc Noise Margins, 167                                                                                                                                                                                                                                                                                                                                                                                              |     |

|   |                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| RESISTOR-TRANSISTOR LOGIC RTL AND<br>RESISTOR-CAPACITOR TRANSISTOR LOGIC RCTL          |                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6-2<br>6-3                                                                             | Resistor-Capacitator-Transistor Logic RCTL, 177                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                        |                                                                                                                                                                                                                                                                          | 180                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 7-1                                                                                    | The Modern Integrated Circuit Version of Diode-Transistor Logic, 180                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7-3                                                                                    | Emitter-Coupled Logic ECL, 187<br>Wired Logic, 195                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TRANSISTOR-TRANSISTOR LOGIC TTL OR T <sup>2</sup> L WITH OUTPUT CIRCUIT VARIATIONS 204 |                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 8-2<br>8-3<br>8-4<br>8-5<br>8-6<br>8-7<br>8-8                                          | Steady-state Analysis of a TTL NAND Gate, 207 Transient Response of the TTL NAND Gate, 222 The TTL NOR Gate, 227 The TTL Inverter, 229 The TTL AND Gate, 230 The TTL OR Gate, 233 The AND-OR-INVERT Circuit, 233 Output Circuit Variations, 236                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| AST                                                                                    | ABLE AND MONOSTABLE MULTIVIBRATORS                                                                                                                                                                                                                                       | 256                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 9-2<br>9-3<br>9-4<br>9-5<br>9-6<br>9-7                                                 | A Modified Collector-coupled Astable MV, 268 Synchronization of the Collector-coupled Astable MV and Frequency Division, 270 The pnp Collector-coupled Astable MV, 271 The Collector-base Coupled Monostable Multivibrator, 273 An Application of the Monostable MV, 284 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                        | RESI 6-1 6-2 6-3 6-4 DIO EMI 7-1 7-2 7-3 7-4 TRA WIT 8-1 8-2 8-3 8-4 8-5 8-6 8-7 8-8 8-9 8-10 AST 9-1 9-2 9-3 9-4                                                                                                                                                        | RESISTOR-CAPACITOR TRANSISTOR LOGIC RCTL  6-1 RTL NOR Gates, 171 6-2 Analysis of the Multitransistor RTL NOR Gate, 173 6-3 Resistor-Capacitator-Transistor Logic RCTL, 177 6-4 Summary, 177  DIODE-TRANSISTOR LOGIC DTL EMITTER-COUPLED LOGIC ECL WIRED LOGIC  7-1 The Modern Integrated Circuit Version of Diode-Transistor Logic, 180 7-2 Emitter-Coupled Logic ECL, 187 7-3 Wired Logic, 195 7-4 Summary, 200  TRANSISTOR-TRANSISTOR LOGIC TTL OR T²L WITH OUTPUT CIRCUIT VARIATIONS  8-1 Construction of the Multi-emitter Transistor, 204 8-2 Steady-state Analysis of a TTL NAND Gate, 207 8-3 Transient Response of the TTL NAND Gate, 222 8-4 The TTL NOR Gate, 227 8-5 The TTL Inverter, 229 8-6 The TTL AND Gate, 233 8-7 The TTL OR Gate, 233 8-8 The AND-OR-INVERT Circuit, 233 8-9 Output Circuit Variations, 236 8-10 Summary, 252  ASTABLE AND MONOSTABLE MULTIVIBRATORS  9-1 The Collector-base Coupled Astable Multivibrator, 257 9-2 Circuit Analysis, 261 9-3 A Modified Collector-coupled Astable MV, 268 9-4 Synchronization of the Collector-coupled Astable MV and Frequency Division, 270 9-5 The pnp Collector-coupled Astable MV, 271 9-6 The Collector-base Coupled Monostable Multivibrator, 273 9-7 An Application of the Monostable MV, 284 |

| 10 | MODERN LOGIC FLIP-FLOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 288 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    | <ul> <li>10-1 The Basic Flip-flop, 288</li> <li>10-2 The Basic Logic Flip-flop, 293</li> <li>10-3 Types of Logic Flip-flops, 294</li> <li>10-4 Practical Logic Flip-flop Circuits, 297</li> <li>10-5 The Timing Problem, 301</li> <li>10-6 A D-type Flip-flop, 312</li> <li>10-7 The Relationships Between the Various Flip-flops, 314</li> </ul>                                                                                                                                          |     |

| 11 | SPECIAL-PURPOSE CIRCUITS                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 320 |

|    | 11-1 Internal Gates, 320 11-2 A Schottky-clamped TTL Gate, 324 11-3 Simple Lamp Drivers, 325 11-4 Relay Drivers, 327 11-5 A Transmission Line Driver and Terminator, 328 11-6 A Crystal-controlled Clock Pulse Generator, 328 11-7 The Schmitt Trigger, 330 11-8 Analysis of the Schmitt Trigger, 333 11-9 Fast Analysis of the Schmitt Trigger, 341 11-10 FET Logic Circuits, 342 11-11 CMOS Logic, 346 11-12 Three-state Logic TSL, 350 11-13 Interface Elements, 352 11-14 Summary, 354 |     |

| 12 | PACKAGING AND APPLICATIONS OF DIGITAL CIRCUITS                                                                                                                                                                                                                                                                                                                                                                                                                                             | 356 |

|    | 12-1 TTL Packages, 356 12-2 A Monostable Package, 372 12-3 Summary, 374 12-4 Complex Arrays, 374                                                                                                                                                                                                                                                                                                                                                                                           |     |

|    | INDEX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 401 |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

7

## NETWORK ANALYSIS

To analyze pulse and digital circuits, it is often necessary to replace the circuit with a network of components equivalent to the actual circuit. The equivalent circuit is obtained by applying one or more network theorems. It is then analyzed by using either standard techniques or other network theorems. In this chapter only Thévenin's, Norton's, and Millman's theorems, which are used extensively throughout the text, are covered. RC time constant theory is also discussed because an understanding of these principles is essential in pulse and digital circuit analysis.

### 1-1 Thévenin's Theorem

Thévenin's theorem states that any two-terminal linear network, no matter how complex, may be replaced by a single voltage source in series with a single impedance. The value of this Thévenin equivalent voltage  $V_{TH}$  is the same as the voltage that appears across the load terminals if the load is replaced by an open circuit. The value of the Thévenin impedance  $Z_{TH}$  is the same as the impedance seen by the load when all sources are replaced by their internal impedance.

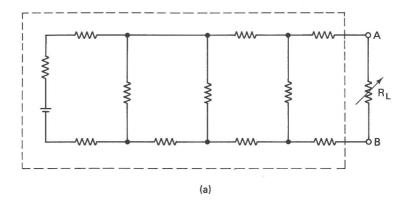

This theorem is extremely useful when a complex circuit with a changing (variable) load is analyzed. For example, every time that load resistance  $R_L$  changes in Fig. 1-1(a) all of the voltage drops and currents change. If the load voltage  $V_{R_L}$  must be determined for many different values of  $R_L$ , the entire circuit must be analyzed each time. In Fig. 1-1(b) that part of the circuit

Fig. 1-1 (a) A complex series parallel circuit with a varying load. (b) The unchanging part of (a) replaced by its Thévenin equivalent.

which does *not* change is replaced by its Thévenin equivalent circuit. Now each time that  $R_L$  changes the voltage across  $R_L$  is easily calculated by

$$V_{R_L} = V_{TH} \left( \frac{R_L}{R_L + R_{TH}} \right) \tag{1-1}$$

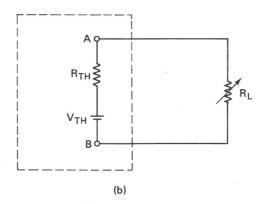

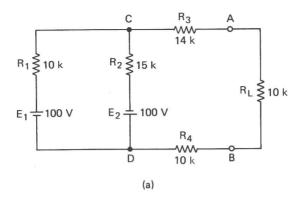

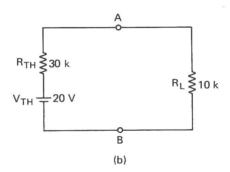

Thévenin's theorem is also very useful when the output voltage of a circuit containing several voltage or current sources must be determined. In Fig. 1-2 a circuit containing two voltage sources is replaced by its Thévenin equivalent to produce a simple series circuit. The values of  $V_{TH}$  and  $R_{TH}$  in Fig. 1-2 are calculated by using the rules stated in the theorem, as follows:

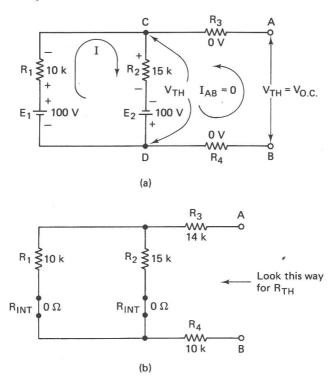

Determine  $V_{TH}$  by removing  $R_L$  and calculating the open-circuit voltage from A to  $B(V_{AB_{0c}})$ . Figure 1-3(a) shows the circuit that must be analyzed to find  $V_{TH}$ .

Fig. 1-2 (a) A circuit containing more than one source simplified in (b) by changing everything to the left of A and B to a Thévenin equivalent.

If  $R_{AB} = \infty$ ,

$$I_{AB}=0$$

and

$$V_{R_3} = V_{R_4} = 0$$

If  $V_{R_3} = 0$ ,

$$V_A = V_C$$

and if  $V_{R_4} = 0$ ,

$$V_B = V_D$$

Hence

$$V_{AB} = V_{CD}$$

and

$$V_{CD} = V_{R_2} + E_2 = V_{R_1} + E_1$$

Fig. 1-3 (a) The circuit that must be analyzed to find  $V_{TH}$  in Fig. 1-2. (b) The circuit that must be analyzed to find  $R_{TH}$  in Fig. 1-2.

Therefore, to find  $V_{TH}$ , solve for either  $V_{R_1}$  or  $V_{R_2}$  and add it to the appropriate voltage source. With  $R_{AB} = \infty$ , the only current I flows through the series circuit shown in Fig. 1-3(a). Since  $E_1$  and  $E_2$  are series aiding, the total voltage in this loop is

$$E_T = E_1 + E_2$$

= 100 + 100

$E_T = 200 \text{ V}$

and

$$V_{R_1} = E_T \frac{R_1}{R_1 + R_2}$$

$$= 200 \frac{10}{25}$$

$V_{R_1} = 80 \text{ V}$

Therefore,

$$V_{CD} = V_{R_1} + E_1$$

= (-80) + (100)

$V_{CD} = 20 \text{ V}$

and

$$V_{TH} = 20 \text{ V}$$

The polarities for  $V_{R_1}$  and  $E_1$  are those seen at the point C side of  $R_1$  and  $E_1$  when finding the voltage at C with respect to D.

Now solve for  $R_{TH}$  by replacing both sources with their internal resistance and by calculating the resistance seen by  $R_L$ . Fig. 1-3(b) shows the circuit that must be analyzed to find  $R_{TH}$ . Unless otherwise stated, assume that voltage sources have zero internal resistance and that current sources have infinite internal resistance. Then

$$R_{TH} = R_3 + R_4 + \frac{R_1 R_2}{R_1 + R_2}$$

$$= 14 + 10 + \frac{(10)(15)}{25}$$

$$R_{TH} = 30 \text{ k}\Omega$$

An alternate method of calculating  $V_{TH}$  is now shown.

$$V_{R_2} = E_T \frac{R_2}{R_1 + R_2}$$

$$= 200 \frac{15}{25}$$

$V_{R_2} = 120 \text{ V}$

Hence,

$$V_{CD} = V_{R_2} + E_2$$

= (120) + (-100)

$V_{CD} = 20 \text{ V}$

In either case

$$V_{TH} = 20 \text{ V}$$

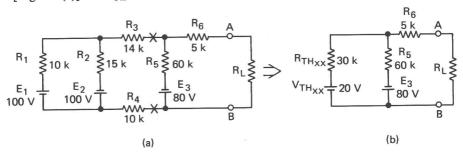

The Thévenin equivalent of more complex networks is found section by section. The circuit is broken (opened) so that a Thévenin equivalent can be determined for a circuit no more complex than the one illustrated in Fig.

1-3(a). Then the remaining circuit is replaced one section at a time. After each section is replaced, a new partial Thévenin equivalent is calculated until finally the entire circuit has been included. This is illustrated in Ex. 1-1 in which the Thévenin equivalent of Fig. 1-4(a) is calculated.

Example 1-1: Find the Thévenin equivalent of the circuit shown in Fig. 1-4(a).

**Solution:** If the circuit is broken at the points marked X, the circuit arrangement to the left of these points is exactly the same as Fig. 1-3(a), and since the same values are used,

$$V_{TH_{XX}} = 20 \text{ V}$$

and

$$R_{TH_{XX}} = 30 \text{ k}\Omega$$

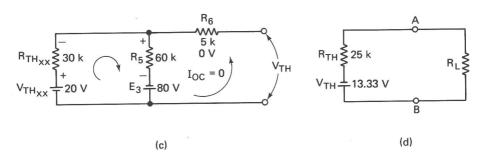

This results in Fig. 1-4(b). By removing  $R_L$  and solving the remaining circuit [Fig. 1-4(c)] for  $V_{TH}$  and  $R_{TH}$  the overall Thévenin equivalent is found.

Fig. 1-4 (a) A more complex network containing three sources. (b) Fig. (a) partially simplified by finding the Thévenin equivalent of everything to the left of the points marked X. (c) Fig. (b) showing the only current with  $R_L$  removed. (d) The overall Thévenin equivalent circuit seen by  $R_L$ .

Solving for  $V_{TH}$ , it is determined that

$$V_{TH} = V_{AB_{ac}} = V_{R_5} + E_3$$

where

$$V_{R_5} = (V_{TH_{XX}} + E_3) \frac{R_5}{R_5 + R_{TH_{XX}}}$$

$$= 100 \frac{60}{90}$$

$$V_{R_5} = 66.67 \text{ V}$$

Therefore,

$$V_{TH} = (+66.67) + (-80)$$

$V_{TH} = -13.33 \text{ V}$

Solving for  $R_{TH}$ , it is determined that

$$R_{TH} = R_6 + \frac{R_5 R_{TH_{XX}}}{R_5 + R_{TH_{XX}}}$$

$$= 5 + \frac{(60)(30)}{90}$$

$$R_{TH} = 25 \text{ k}\Omega$$

Because of the complexity of some circuits the Thévenin equivalent cannot always be found directly. In such cases other theorems are used to first simplify the circuit; then  $V_{TH}$  and  $R_{TH}$  are calculated.

### 1-2 Norton's Theorem

Norton's theorem states that any two-terminal linear network, no matter how complex, can be replaced by a single current source in parallel with a single impedance. The value of this Norton equivalent current  $I_N$  is the same as the current that flows between the load terminals if the load is replaced by a short circuit. The value of the Norton impedance  $Z_N$  is the same as the impedance seen by the load when all sources are replaced by their internal impedance. Note that  $Z_N$  is the same as  $Z_{TH}$ .

Norton's theorem is very useful when the load impedance  $Z_L \ll Z_N$ . For example, in Fig. 1-5,  $R_L$  varies between 10 and 100  $\Omega$ . When  $R_L = 10 \Omega$

$$I_L = I_N \frac{R_N}{R_L + R_N}$$

$$= 0.5 \text{ mA} \frac{10,000 \Omega}{10,010 \Omega}$$

$I_L \approx 0.5 \text{ mA}$