# Digital Electronics Practice Using Integrated Circuits

RP JAIN M M S ANAND

## Digital Electronics Practice Using Integrated Circuits

#### RP JAIN

Birla Institute of Technology and Spence Pilani

M M S ANAND

eel Authority of India Limited

#### © 1983, TATA McGRAW-HILL PUBLISHING COMPANY LIMITED

No part of this publication can be reproduced in any form or by any means without the prior written permission of the publishers

This edition can be exported from India only by the publishers, Tata McGraw-Hill Publishing Company Limited

This book has been subsidized by the Government of India through National Book Trust. India, for the benefit of students

Asst Sponsoring Editor: KALPANA SHUKLA

Asst Production Editor: RANJAN KAUL

Production Assistant: B L DOGRA

Rs. 38.00

Published by Tata McGraw-Hill Publishing Company Limited, 12/4 Asaf Ali Road, New Delhi 110 002 and printed by S.P. Jain at J. Samanta Machinery Company (P) Ltd., 14-A, Kamla Nagar, Delhi 110 007

#### PREFACE

There has been unprecedented growth in the field of digital techniques since Claude Shannon systematized and adapted George Boole's theoretical work in 1938. Now it has become one of the most fascinating and challenging fields of study.

The importance of digital electronics can be seen from a wide variety of industrial and consumer products, such as automated industrial machinery, computers, microprocessors, pocket calculators, digital watches and clocks, TV games, etc. The importance of digital electronics has increased owing to the advent of integrated circuit (IC) technology. The size, cost and power dissipation of electronic devices have been reduced by 2000: I from the days of vacuum tubes, and their performance, realiability and efficiency have greatly improved with the improvements in IC technology.

It can be confidently said that almost all graduates in electronics engineering will take up jobs calling for a knowledge of digital electronic principles and practice. Therefore, a sound education in digital electronics is vital for a successful career in-electronics. With this in view, we have attempted to write this book to fill the long-felt need of electronics engineering students, practising engineers and scientists. The book will prove extremely useful for a digital electronics course with an associated laboratory.

Students of physics and others with a knowledge of basic electronics but without any prior knowledge of digital systems and ICs will find this book very useful. A thorough understanding of the topics given here will enable them to study and understand the most fascinating fields of microprocessors, microcomputers, etc.

The book has been divided into six parts. The first two experiments of Part I introduce to the reader the basic digital building blocks—the gates, and the other three experiments deal with the characteristics of the gates with totem-pole, open-collector and tri-state outputs. It is very essential to know about these characteristics of ICs to effectively use them in any complex digital system.

Part II deals with the combinational logic circuits starting from simple functions such as half-adder and half-subtractor to more complex systems, such as arithmetic/logic units (ALU), multiplexers, demultiplexers, code converters, etc. All these functions are discussed in detail.

Part III starts with FLIP-FLOPS which are the basic building blocks for sequential circuits. Shift-registers and asynchronous and synchronous counters are thoroughly covered. Semiconductor memories have also been explained in a very simple and concise manner

Part IV deals with the pulse-generating circuits required in digital systems. In this part very useful and popular analog ICs, such as OP-AMP and timers have also been used, in addition to the available digital ICs.

Part V deals with analog-to-digital (A/D) and digital-to-analog (D/A) converters. These are used as input and output circuits for interfacting digital systems with the real world which is mostly analog.

Each experiment is followed by review questions which will give an opportunity to the students to test their understanding of the topic. At the end of most of the experiments, exercises have been included which will be of additional help in learning more about digital systems.

Based on the topics covered in Parts I through V, the general digital system design methodology have been evolved in Part VI. Trouble-shooting techniques and equipment required for this purpose have been included as a project. The other projects discussed are: the binary multiplier, digital clock, digital voltmeter (DVM), and digital frequency meter.

Useful information about digital ICs, such as the numbering of IC pins, details of IC sockets, interpretation of the information printed on ICs, etc. a: given in Appendix A.

TTL is the most popular and widely used IC technology today as far as small-scale (SSI) and metium-scale (MSI) ICs are concerned. The standard TTL family known as the 54/74-series has been used for experiments. Specifications of ICs of this series are given in Appendix B. It is recommended that the student reads Appendices A and B before starting the experimental work.

Appendix C deals with another important logic family, namely CMOS. Information regarding the 54C/74C-series of CMOS ICs and their interfacing with TTL ICs are given here. Appendix D deals with emitter-coupled logic (ECL).

Appendix E gives the pinout connections of about 200 different digital ICs of the 54/74-series which will prove to be very useful for any person working with the 54/77-series of the most popular TTL ICe or with the 54C/74C-series of CMOS ICs.

The specifications and pinouts of timers. OP-AMP, 7-segment LED, NIXIE tube and diodes used in the text are given in Appendix F.

The experiments have been designed generally for a three-hour laboratory session for an adequately prepared student. Therefore, either two laboratory sessions per week for one semester or one laboratory session per week for two semesters will be required for performing all the experiments and completing all the projects. Selected experiments can be done in other situations.

We are grateful to Dr C.R. Mitra, Director, BITS for providing all the necessary facilities. Our special thanks are due to Prof. I.J. Nagrath and Prof. K.V. Ramanan for encouragement and appreciation, and Prof. S.C. Rastogi for making available the necessary laboratory facilities. Many colleagues and students have contributed in bringing out this work, and we are thankful to all of them.

R P JAIN

M M S ANAND

### **CONTENTS**

Preface

#### Experiments

| Part | I BASIC GATES—FUNCTIONS AND CHARACTERISTICS               | 1   |

|------|-----------------------------------------------------------|-----|

| 1.   | Basic Logic Gates 3                                       |     |

| 2.   | Applications of Basic Gates for Gating Digital Signals 11 |     |

| 3.   | Characteristics of TTL Gates (Totem-Pole Output) 15       |     |

| 4.   | Characteristics of Open-Collector TTL Gates 21            |     |

| 5.   | Characteristics of Tri-State TTL Gates 27                 |     |

| Part | II COMBINATIONAL LOGIC CIRCUITS                           | 33  |

| 6.   | Logic Expressions and their Simplification 35             |     |

| 7.   | Arithmetic Circuits Using Gates 41                        |     |

| 8.   | IC Adder/Subtractor 45                                    |     |

|      | Arithmetic/Logic Unit 55                                  |     |

| 10.  | Digital Comparators 60                                    |     |

| 11.  | Parity Generator/Checker 63                               |     |

| 12.  | Code Converters 67                                        |     |

| 13.  | Encoders and Decoders 77                                  |     |

| 14.  | Multiplexers 87                                           |     |

| 15.  | Demultiplexers 96                                         |     |

| 16.  | Expandable Gates, Expanders and AND-OR-INVERT Gates 102   |     |

| Part | III FLIP-FLOPS, SEQUENTIAL LOGIC CIRCUITS AND             |     |

|      | MEMORIES                                                  | 109 |

| 17.  | FLIP-FLOP Circuits Using Gates 111                        |     |

| 18.  | FLIP-FLOP ICs 117                                         |     |

| 19.  | Shift-Registers and Ring-Counters 125                     |     |

| 20.  | Asynchronous Counters Using FLIP-FLOP ICs 131             |     |

| 21.  | Asynchronous Counter ICs 134                              |     |

| 23.  | Synchronous Counter ICs 142                               |     |

| 23.  | Synchronous Counter ICs 142                               |     |

| 24.  | Semiconductor Memories 149                                |     |

|   | ~  |       |

|---|----|-------|

| X | On | tents |

|   |    |       |

| Part                     | IV TIMING CIRCUITS                                                                                 | 157 |

|--------------------------|----------------------------------------------------------------------------------------------------|-----|

| 25.<br>26.<br>27.<br>28. | Monostable Multivibrators 159 Astable Multivibrators 167 IC Timer Circuits 170 Schmitt Trigger 178 |     |

| Part                     | t V ANALOG-TO-DIGITAL AND DIGITAL-TO-ANALOG CONVERTERS                                             | 183 |

| 29.<br>30.               | Digital-to-Analog Converters 185 Analog-to-Digital Converters 189                                  |     |

|                          | Projects                                                                                           |     |

| Par                      | t VI DIGITAL SYSTEMS DESIGN PROJECTS                                                               | 197 |

| 1.<br>2.                 | Logic Test Equipment 199 Binary Multiplier 203                                                     |     |

| 3.                       | Digital Clock 207                                                                                  | Gr. |

| 4.<br>5.                 | Digital Voltmeter 210 Digital Frequency Meter 213                                                  |     |

|                          | Appendices                                                                                         | 219 |

| A.                       | Information about Digital ICs 221                                                                  |     |

| В.<br>С.                 | Specifications of TTL ICs 225<br>CMOS Logic ICs 227                                                |     |

| D.                       | Emitter Coupled Logic (ECL) ICs 233                                                                |     |

| E.                       | Pinout Connections of ICs 236                                                                      |     |

| F.                       | Specifications of Other Devices 309 Standard SOP and POS Forms of Eq. (6.1) 314                    |     |

| G.<br>H.                 | Standard SOP and POS Forms of Eq. (6.1) 314  Design of Synchronous-Counters 315                    |     |

| I.                       | Pibliography 317                                                                                   |     |

| Ind                      | ex                                                                                                 | 321 |

## **PART I**

## BASIC GATES—FUNCTIONS AND CHARACTERISTICS

#### Experiment 1

#### BASIC LOGIC GATES

#### 1.1 AIM

To study the functions of basic logic gates: AND, OR, NOT, NAND, NOR and EX-OR.

#### 1.2 INTRODUCTION

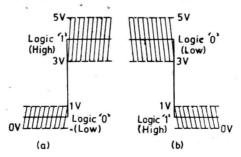

In digital electronic circuits, two discrete voltage levels are recognized as two logic levels, viz. logic '1' and logic '0'. These are also known as 'HIGH' and 'LOW' logic levels. Depending upon the actual voltages, there are two types of logic circuits: (i) positive logic—in which the higher voltage level corresponds to '1' (HIGH) and the lower level corresponds to '0' (LOW), and (ii) negative logic—in which the lower level corresponds to '1' (HIGH) and the higher level corresponds to '0' (LOW). Figure 1.1(a) and (b) shows the positive and negative logic voltage levels. It may be noted that a specified range of voltages (as shown by the shaded regions in Fig. 1.1) represents the '1' or '0' logic level.

Fig. 1.1 Voltage levels for: (a) positive logic; (b) negative logic

In digital circuits, there are only four basic operations which are required to be performed. These are AND, OR, NOT and FLIP-FLOP. There are two types of digital circuits: (i) combinational circuits and (ii) sequential circuits.

#### 4 Basic Gates-Functions and Characteristics

In combinational circuits, the outputs at any instant of time depend completely on the inputs present at that instant of time. In such circuits or y AND, OR and NOT operations are required. These circuits are discussed re.

In sequential circuits the outputs at any instant of time depend upon the past outputs as well as the inputs present at that instant of time. Here in addition to AND, OR and NOT operations, FLIP-FLOPS (FF) are also required. These will be studied later.

NAND and NOR operations are also defined which can be used to realize AND, OR and NOT operations.

The function, logic diagram and truth table for each of the gates are given in Table 1.1. This table illustrates the AND, OR, NAND and NOR gates with two inputs only, but the number of inputs can be more than two also.

Table 1.1 Logic diagrams, functions and truth tables of basic gates

| Gate | Logic diagram | Function       |     | Tr   | uth table |

|------|---------------|----------------|-----|------|-----------|

| AND  |               |                | Ing | outs | Output    |

|      |               | Y = A and $B$  | Λ   | В    | Y         |

|      | A •           | = A.B          | 0   | 0    | 0         |

|      | в⊷            | $= A \wedge B$ | 0   | 1    | 0         |

|      | = <u>3</u>    | = A B          | 1   | 0    | 0         |

|      |               |                | 1   | 1    | 1         |

| Y = A  or  B                      | ıt |

|-----------------------------------|----|

| A                                 |    |

|                                   |    |

| $= A \lor B \qquad 0  1 \qquad 1$ |    |

| 1 0 1                             |    |

| 1 1                               |    |

(Contd)

| Gate                                             | Logic diagram | Function                  |     | T    | ruth table |

|--------------------------------------------------|---------------|---------------------------|-----|------|------------|

| NOT<br>(Invertor)                                | •             |                           | I   | nput | Output     |

|                                                  | _             | Y = NOT A                 |     | A    | Y          |

| A •-                                             | <b>→</b>      | = A                       |     | 0    | 1          |

|                                                  |               |                           |     |      | 0          |

| NAND                                             |               |                           | In  | puts | Outpu      |

|                                                  |               | Y = A not and $B$         | A   | В    | Y          |

|                                                  |               | = A  NAND  B              | 0   | 0    | 1          |

| . A•                                             |               | $=\overline{A.B}$         | 0   | 1    | 1          |

| ₿⊷                                               |               | $= \overline{A \wedge B}$ | 1   | 0    | 1          |

|                                                  |               | $= A \uparrow B$          | 1   | 1    | 0          |

|                                                  |               | $=\overline{AB}$          |     |      | (W         |

| IOR                                              | 8             |                           | Inj | puts | Output     |

|                                                  | *             | Y = A not or $B$          | A   | В    | Y          |

| A •                                              |               | = A  NOR  B               | 0   | 0    | 1          |

| В•                                               |               | $=\overline{A+B}$         | 0   | 1    | 0          |

|                                                  |               | $= \overline{A \vee B}$   | 1   | 0    | 0          |

|                                                  |               | $= A \downarrow B$        | 1   | 1    | 0          |

| X-OR                                             | 3             | •                         | Ing | outs | Output     |

|                                                  | * * * *       | Y = A  ex-or  B           | A   | В    | Y          |

| A <b>←</b> − − − − − − − − − − − − − − − − − − − |               | $= A \oplus B$            | 0   | 0    | . 0        |

| 5                                                |               | = AB + AB                 | 0   | 1    | 1          |

|                                                  |               | $= A \forall B$           | 1   | 0    | 1          |

#### 6 Basic Gates-Functions and Characteristics

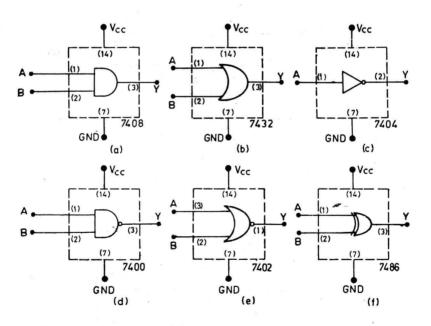

These functions can be realized by using discrete devices, such as diodes, bipolar junction transistors (BJTs), and field effect transistors (FETs). However, since these gates are now directly available in the integrated circuit (IC) form, we will be dealing with only ICs. Table 1.2 gives a list of available basic gates in the IC form.

| Table | 12  | Available | hacia | moto | IC. |

|-------|-----|-----------|-------|------|-----|

| Laule | 1.4 | Available | Dasic | gate | 163 |

| IC number   | Description               |

|-------------|---------------------------|

| 7400        | Quad 2-input NAND gates   |

| 7402        | Quad 2-input NOR gates    |

| 7404        | Hex inverters             |

| 7408        | Quad 2-input AND gates    |

| 7410        | Triple 3-input NAND gates |

| 7411        | Triple 3-input AND gates  |

| 7420        | Dual 4-input NAND gates   |

| 7421        | Dual 4-input AND gates    |

| 7427        | Triple 3-input NOR gates  |

| 7430        | 8-input NAND gate         |

| 7432        | Quad 2-input or gates     |

| 7486, 74386 | Quad EXCLUSIVE-OR gates   |

| 74133       | 13-input NAND gate        |

| 74135       | Quad Ex-or/Nor gates      |

| 74260       | Dual 5-input Nor gates    |

#### 1.3 EXPERIMENTS

#### 1.3.1 Basic Operations

#### (i) AND gate

Identify the terminals of the 7408 quad, 2-input IC and gate (refer Appendix E). Connect +5.0 V dc between  $V_{cc}$  and GND terminals (Positive terminal of the supply must be connected to the  $V_{cc}$  terminal). Use +5 V for logic '1' and 0 V for logic '0'. A section of the IC is shown in Fig. 1.2(a). Measure the output voltages for the various combinations of the input voltages given in Table 1.3 and verify the results with the truth table of the AND gate given in Table 1.1.

Table 1.3 Various input combinations

| A    | ×   | . B |

|------|-----|-----|

| 0 V  | - A | 0 V |

| 0 V. |     | 5 V |

| 5 V  |     | 0 V |

| 5 V  |     | 5 V |

Check if the output voltages for the logic levels '1' and '0' correspond to the values given in Fig. 1.1(a).

(ii) OR gate

Repeat (i) for a 7432 quad,

2-input IC OR gate, a section of which is shown in Fig. 1.2(b).

#### (iii) NOT gate

Repeat (i) for a 7404 hex IC inverter, a section of which is shown in Fig. 1.2(c).

#### (iv) NAND gate

Repeat (i) for a 7400 quad, 2-input IC NAND gate, a section of which is shown in Fig. 1.2(d).

#### (v) NOR gate

Repeat (i) for a 7402 quad, 2-input IC NOR gate, a section of which is shown in Fig. 1.2(e).

#### (vi) EX-OR gate

Repeat (i) for a 7486 quad, IC Ex-or gate, a section of which is shown in Fig. 1.2(f).

Fig. 1.2 Single sections of ICs: (a) 7408; (b) 7432; (c) 7404; (d) 7400; (e) 7402; (f) 7486

#### 1.3.2 Combinations of Gates

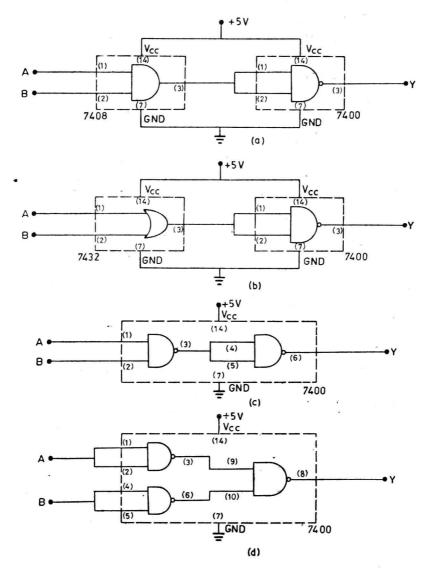

Set up the circuits shown in Fig. 1.3. Find experimentally the truth table for each circuit and verify theoretically. Match the truth table of each part with the truth tables given in Table 1,1 and name the operation performed by each part.

- 8 Basic Gates-Functions and Characteristics

- (ii) Replace each NAND gate in Fig. 1.3(c) and (d) by a NOR gate and repeat (i).

Fig. 1.3 Combinations of gates

#### **REVIEW QUESTIONS**

- 1.1 Give the name of the IC package used in the experiment.

- 1.2 How many gates are there in the following ICs?

(a) 7400, (b) 7404, (c) 7410, (d) 7430, and (e) 74260.

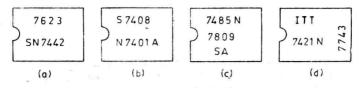

1.4 Identify the IC no. of the packages shown in Fig. 1.4.

Fig. 1.4 IC packages

- 1.5 What is the difference between the logic symbols of:

- (a) AND and NAND gate;

- (b) or and NOR gate; and

- (c) or and EX-OR gate.

- 1.6 Figure 1.5 gives an equivalent logic representation of a NAND gate. Make its truth table and compare it with the actual truth table of the NAND gate.

Fig. 1.5 An equivalent representation of NAND gate

4.7 Make a truth table for the logic symbol shown in Fig. 1.6 and name the operation performed by this circuit.

- 1.8 Make a NOT gate using:

- (a) a 2-input NAND gate;

- (b) a 2-input NOR gate;

- (c) a 3-input NAND gate;

- (d) a 3-input Nor gate; and

- (e) an EX-OR gate.

- 1.9 How will you use a 3-input

- (a) NAND gate as a 2-input NAND gate?

- (b) NOR gate as a 2-input NOR gate?

- (c) AND gate as a 2-input AND gate?

- (d) OR gate as a 2-input OR gate?

- 1.10 Can you use an EX-OR gate to compare two digital signals A and B and determine whether they are equal or not? If yes, explain how you will obtain it.

- 1.11 In the 74135 EX-OR/NOR IC, find the logic level to be applied at C to obtain

- (a)  $Y = A \oplus B$  and

- (b)  $Y = A \oplus B$