Microprocessors and Programmed Logic

#### Library of Congress Cataloging in Publication Data

Short, Kenneth L Microprocessors and programmed logic.

Bibliography: p. Includes index. 1. Microprocessors. I. Title. QA76.5.S496 001.6'4 79-23167 ISBN 0-13-581173-2

Editorial/production supervision and interior design by Steven Bobker Cover design by Edsal Enterprises Manufacturing buyers: Gordon Osbourne and Anthony Caruso

© 1981 by Prentice-Hall, Inc., Englewood Cliffs, N.J. 07632

All rights reserved. No part of this book may be reproduced in any form or by any means without permission in writing from the publisher.

Printed in the United States of America

10 9 8 7 6 5 4 3 2 1

Prentice-Hall International, Inc., London

Prentice-Hall of Australia Pty. Limited, Sydney

Prentice-Hall of Canada, Ltd., Toronto

Prentice-Hall of India Private Limited, New Delhi

Prentice-Hall of Japan, Inc., Tokyo

Prentice-Hall of Southeast Asia Pte. Ltd., Singapore

Whitehall Books Limited, Wellington, New Zealand

## Preface

The single most significant development in digital systems design in recent years has been the advent of the microprocessor, a central processing unit integrated on a single chip of silicon. The processing power and economics of the microprocessor have had a tremendous impact on the way digital systems are designed and on their scope of application.

This book is about the microprocessor. It is also about its related integrated circuits and the hardware and software design of microprocessor based systems. Its purpose is to first provide the reader with a thorough understanding of the basic hardware and software concepts necessary for the design of microprocessor based systems, and, further, to provide the reader with an in-depth knowledge of specific actual devices and the attendant practical considerations and design techniques necessary to effectively design systems using them.

A unique feature of this book is its utilization of a single microprocessor, the 8085A, as the example used to illustrate fundamental concepts. Use of a single microprocessor as the instructional example allows an increased depth of coverage of the operation, features, and limitations of a real device.

In addition, it allows use of a single consistent set of signals and signal names for interfacing the many logical devices which constitute a microprocessor system. Use of a single set of signal names simplifies the reader's task

in understanding hardware interfacing concepts and the functional operation of various LSI devices.

The 8085A is a general purpose 8-bit microprocessor. This microprocessor was chosen because of its widespread use in industrial applications and its widespread support. This support manifests itself in the form of documentation, application notes, and software and hardware development aids for the 8085A. In addition, there exists a large family of peripheral LSI devices which are designed to be compatible with the 8085A. Because of its wide applicability, the reader will find that the knowledge gained about the 8085A and its support devices is immediately applicable to many actual designs in industry.

A further advantage of studying a single microprocessor in depth is that the reader not only learns of the features of the device but also learns that with these features come attendant limitations which must be dealt with in any practical application. It should be noted that a reader following a device specific instructional approach will find that once a specific microprocessor and its application in digital system design has been mastered, it is relatively easy to understand the operation and application of other microprocessors from a study of the manufacturers' user manuals and application notes. This has been the experience of university and industry students who have followed this approach in the author's microprocessor courses over the past several years.

The design of microprocessor systems requires a knowledge of both hardware and software. It is assumed that the reader has a basic knowledge of digital hardware at the gate and flip-flop levels. This material can be found in any introductory book on digital systems design. The software concepts in this book are illustrated using assembly language for the 8085A. However, prior knowledge of assembly language programming is not necessary. Some general knowledge of computer programming in a high level language is desirable.

The goal has been to introduce the necessary hardware and software concepts in an elementary, systematic, and integrated fashion and to logically build upon these concepts. While the study of no single text can provide mastery in a subject area, it is believed that this text will provide the reader with a solid foundation for the development of proficiency in the design of microprocessor systems.

This book covers the topics recommended for inclusion in the course DL-3 Microprocessor Systems as part of a computer science and engineering curriculum as proposed by the Model Curriculum Subcommittee of the IEEE Computer Society.<sup>1</sup>

#### Acknowledgments

A number of people have contributed to this book being written. While I cannot thank them all, I would like to express my appreciation to Mr. Paul

<sup>1</sup>"A Curriculum in Computer Science and Engineering Committee Report." IEEE Service Center, 445 Hoes Lane, Piscataway, NJ 08854, January, 1977.

Preface

Becker, Mr. Don Buchout, Dr. Velio Marsocci, Mr. Casey Powell, Mr. Rich Reeder, and Dr. David Smith.

I would also like to thank the many students who, in using rough drafts of this text as class notes, have provided comments and suggestions which have led to the improvement of the text.

A very special thanks to Lee Cushman whose editing, organizational, and typing skills were critical to the writing of this book.

Kenneth L. Short

## Contents

#### Preface, xiv

#### 1 INTRODUCTION, 1

- 1.1 The Impact of LSI on Logic Design, 2

- 1.2 Approaches to the Utilization of LSI, 5

- 1.21 Custom LSI, 5

- 1.22 Catalog LSI, 6

- 1.23 Programmable LSI, 6

- 1.3 Microprocessor Systems, 13

- 1.4 Areas of Application, 16

- 1.5 Designing Microprocessor Systems, 19

References, 22

Bibliography, 22

Problems, 23

## 2 RANDOM ACCESS SEMICONDUCTOR MEMORIES, 27

- 2.1 Basic Memory Concepts, 28

- 2.1.1 Flip-Flops / 1-Bit Registers, 28

- 2.1.2 M-Bit Registers, 31

- 2.1.3 Memories, 34

- 2.2 Memory Classes, 36

- 2.3 Semiconductor RAM Device Organization, 39

- 2.4 Memory Device Timing and Operation, 43

- 2.5 Memory System Organization, 47

- 2.6 Interfacing Memory, 50

- 2.7 Memory Technology, 53

- 2.8 ROMs, 54

- 2.8.1 MOS ROMs, 55

- 2.8.2 Bipolar ROMs, 56

- 2.9 PROMs, EPROMs, and EAROMs. 56

- 2.9.1 Fusible Link PROMs, 57

- 2.9.2 Floating Gate EPROMs, 58

- 2.9.3 PROM Programmers, 60

- 2.9.4 EAROMs. 62

- 2.10 Read/Write Memory, 62

- 2.10.1 Bipolar RWM, 63

- 2.10.2 Static MOS RWM. 64

- 2.10.3 Dynamic MOS RWM. 64

References. 65

Bibliography, 66

Problems, 67

### 3 MICROPROCESSOR ARCHITECTURE AND OPERATION, 71

- 3.1 Basic Microprocessor Concepts, 72

- 3.1.1 Control Unit, 76

- 3.1.2 Internal Registers, 7

- 3.1.3 Arithmetic and Logic Unit, 80

- 3.1.4 The Microprocessor's State, 81

- 3.2 LSI Implementation of Microprocessors, 82

- 3.3 The 8085A Microprocessor, 84

- 3.3.1 Architecture of the 8085A, 87

- 3.3.2 Timing and Sequencing, 89

- 3.3.3 Memory and I/O Synchronization—The WAIT State,

- 3.3.4 The Halt State. 97

- 3.3.5 Power ON-Reset and Manual Reset, 97

- 3.4 A Minimum Configuration 8085A Microcomputer, 98

| 3.5 The 8080A Microprocessor and CPU Group, | 99 |  |  |

|---------------------------------------------|----|--|--|

| 3.6 Similarity of the 8085A and 8080A, 105  |    |  |  |

| References, 106                             |    |  |  |

| Bibliography, 106                           |    |  |  |

| Problems, 107                               |    |  |  |

## 4 DATA TRANSFER, LOGIC OPERATIONS, AND BRANCHING, 109

- 4.1 Instruction Sets. 110

- 4.2 Data Transfer Instructions, 112

- 4.2.1 Data Transfer To and From I/O Devices, 113

- 4.2.2 Data Transfer To and From Memory, 119

- 4.2.3 Creation of Additional Addressing Modes, 120

- 4.2.4 Transfer of Data Within the Microprocessor, 121

- 4.3 Logic Operations, 122

- 4.4 Flowcharting, 128

- 4.5 Branch Instructions, 131

- 4.6 Program Looping, 135

- 4.7 Software Delays, 138

References, 141

Bibliography, 141

Problems, 142

### 5 PROGRAM ASSEMBLY AND SIMULATION, 145

- 5.1 Programming Languages, 146

- 5.2 Software Development, 149

- 5.3 Assembler Source Programs, 153

- 5.4 Manual Assembly of Programs, 155

- 5.5 Assembler Directives—Pseudo Instructions, 157

- 5.6 Two-Pass Assemblers. 161

- 5.7 Macros, 165

- 5.8 Simulation, 169

- 5.9 Microcomputer Development Systems, 172

References, 177

Bibliography, 177

Problems, 177

### 6 THE STACK AND SUBROUTINES, 181

- 6.1 The Stack and Stack Operations, 182

- 6.2 Subroutines, 186

- 6.3 Conditional Calls and Returns, 191

| 6.4  | Passing Parameters, 192                               |

|------|-------------------------------------------------------|

| 6.5  | Subroutine Documentation, 196                         |

| 6.6  | Modular Program Structure, 197                        |

| 6.7  |                                                       |

| Bibl | iography, 199                                         |

|      | blems, 199                                            |

|      | , se                                                  |

|      |                                                       |

| ARI  | THMETIC OPERATIONS, 201                               |

| 7.1  | Unsigned Binary Integer Numbers, 202                  |

|      | 7.1.1 Addition, 203                                   |

|      | 7.1.2 Subtraction, 206                                |

|      | 7.1.3 Logical Shifts, 208                             |

|      | 7.1.4 Multiplication, 209                             |

|      | 7.1.5 Division, 211                                   |

| 7.2  | Two's Complement Numbers, 215                         |

|      | 7.2.1 Addition of Two's Complement Numbers, 217       |

|      | 7.2.2 Subtraction of Two's Complement Numbers, 219    |

|      | 7.2.3 Arithmetic Shifts, 221                          |

|      | 7.2.4 Multiplication and Division of Two's Complement |

|      | Numbers, 223                                          |

| 7.3  | BCD Numbers, 225                                      |

|      | 7.3.1 Addition of Unsigned BCD Numbers, 226           |

|      | 7.3.2 Ten's Complement and Subtraction of BCD Numbers |

|      | 228                                                   |

|      | 7.3.3 Multiplication and Division of BCD Numbers, 230 |

|      | 7.3.4 BCD-to-Binary Conversions, 230                  |

| 7.4  |                                                       |

| 7.5  |                                                       |

|      | 7.5.1 Floating Point Formats, 236                     |

|      | 7.5.2 Floating Point Arithmetic Routines, 238         |

| Refe | rences, 244                                           |

|      | ography, <i>244</i>                                   |

|      | lems, 245                                             |

|      |                                                       |

|      |                                                       |

|      |                                                       |

# 8 PROGRAM CONTROLLED I/O, 249

- 8.1 Introduction, 250

- 8.2 Isolated I/O, 251

- 8.3 Memory Mapped I/O, 258

- 8.4 MSI I/O Ports, 259

- 8.5 Program Controlled Parallel Transfer of Information, 265

- 8.6 Programmable LSI Ports, 269

8.6.1 Multifunction Devices Containing Programmable

I/O Ports, 269

8.6.2 Peripheral Interface Devices, 274

- 8.7 Serial Transfer of Information, 279

8.7.1 Asynchronous Serial Character Transfer, 281

8.7.2 Synchronous Serial Character Transfer, 285

- 8.8 Direct Microprocessor Serial I/O Pins, 286

- 8.9 Electrical Characteristics, 287

- 8.9.1 Line Drivers and Receivers, 287

- 8.9.2 Termination, 288

- 8.9.3 Standards, 289

References, 289 Bibliography, 290 Problems, 290

### 9 INTERRUPTS AND DMA, 293

- 9.1 Interrupts, 294

- 9.2 8085A Interrupt Structure, 297

- 9.3 Priority Interrupt Structures, 305

- 9.4 FIFO Buffers, 310

- 9.5 Real-Time Clocks and Interval Timers, 312 9.5.1 The 8155's Timer. 314

- 9.6 Considerations For Using Interrupts, 317 9.6.1 Shared Subroutines, 318

- 9.6.2 Disabling Interrupts, 318

- 9.6.3 Priority Assignments, 319

- 9.7 Direct Memory Access—DMA, 319

References, 325

Bibliography, 326

Problems, 326

### 10 DIGITAL PERIPHERAL DEVICES, 329

- 10.1 Manual Data Entry, 330 10.1.1 Mechanical Switches, 330 10.1.2 Keypads and Keyboards, 333

- 10.2 Displays, 341 10.2.1 LED Displays, 341 10.2.2 CRT Displays, 346

- 10.3 Printers, 352

11

| 10.4              | Mass Storage Systems, 355                               |  |  |

|-------------------|---------------------------------------------------------|--|--|

|                   | 10.4.1 Paper Tape, 355                                  |  |  |

|                   | 10.4.2 Cassettes and Cartridges, 359                    |  |  |

|                   | 10.4.3 Floppy Disks, 366                                |  |  |

| 10.5              | Hardware Implementation of Mathematical Functions, 374  |  |  |

|                   | 10.5.1 Limited Function High Speed Arithmetic ICs, 374  |  |  |

|                   | 10.5.2 Calculator ICs, 376                              |  |  |

|                   | 10.5.3 Arithmetic Processing Units—APUs, 377            |  |  |

| Refere            | ences, 380                                              |  |  |

|                   | graphy, <i>380</i>                                      |  |  |

|                   | ems, 381                                                |  |  |

|                   |                                                         |  |  |

|                   |                                                         |  |  |

|                   |                                                         |  |  |

| ANAL              | OG DATA INPUT AND OUTPUT, 383                           |  |  |

|                   |                                                         |  |  |

|                   | Analog Data, 384                                        |  |  |

| 11.2              |                                                         |  |  |

|                   | 11.2.1 The Ideal Op-Amp, 387                            |  |  |

|                   | 11.2.2 Common Op-Amp Circuits, 390                      |  |  |

|                   | 11.2.3 Differential and Instrumentation Amplifiers, 393 |  |  |

|                   | 11.2.4 Delay and Settling Time, 396                     |  |  |

| 11.3              | Digital to Analog Converters—DACs, 397                  |  |  |

|                   | 11.3.1 Input Codes, 400                                 |  |  |

|                   | 11.3.2 Weighted Resistor D/A Converters, 401            |  |  |

|                   | 11.3.3 R-2R Ladder D/A Converters, 403                  |  |  |

|                   | 11.3.4 $2^nR$ D/A Converters, 404                       |  |  |

|                   | 11.3.5 Reference Voltages, 404                          |  |  |

|                   | 11.3.6 Multiplying D/A Converters, 406                  |  |  |

| 11.4              | D/A Converter Specifications, 407                       |  |  |

| 11.5              | Microprocessor to D/A Converter Interface, 409          |  |  |

| 11.6              | Analog-to-Digital Converters, 412                       |  |  |

|                   | 11.6.1 Comparators, 414                                 |  |  |

|                   | 11.6.2 Counting A/D Converter, 416                      |  |  |

|                   | 11.6.3 Successive Approximation A/D Converters, 418     |  |  |

|                   | 11.6.4 Voltage to Frequency Converters, 420             |  |  |

|                   | 11.6.5 Pulse Width Converters, 421                      |  |  |

|                   | 11.6.6 Dual Slope Integrating A/D Converters, 421       |  |  |

| 11.7              | Sample and Hold Circuits, 424                           |  |  |

| 11.8              | Analog Multiplexers and Demultiplexers, 426             |  |  |

| 11.9              | Multichannel Data Acquisition Systems, 427              |  |  |

|                   | ences, 430                                              |  |  |

| Bibliography, 430 |                                                         |  |  |

| Probl             | ems, 431                                                |  |  |

12

#### MICROPROCESSOR SYSTEM DESIGN, 435

- 12.1 Requirements Definition, 436

- 12.1.1 Context Analysis, 437

- 12.1.2 Functional Specification, 437

- 12.1.3 Design Constraints, 438

- 12.2 Systematic Design, 438

- 12.2.1 Partitioning, 439

- 12.2.2 Selection of an Overall Implementation Method, 439

- 12.2.3 Types of Microprocessors, 440

- 12.2.4 Microprocessor Selection, 449

- 12.3 System Implementation, 454

- 12.3.1 Hardware Implementation, 454

- 12.3.2 Software Implementation, 456

- 12.4 Testing and Debugging, 459

- 12.4.1 Hardware Testing and Debugging, 459

- 12.4.2 Software Testing and Debugging, 462

- 12.4.3 System Testing and Debugging, 463

- 12.5 Documentation and Maintenance, 463

- 12.6 Multiple Microprocessor Systems, 464

12.6.1 Distributed Systems, 465

References. 475

Bibliography, 475

Problems, 476

#### APPENDICES, 479

- A Open Collector and Three-State Outputs, 481

- B Octal and Hexadecimal Numbers, 487

- C Intel 8085A Instruction Set. 489

- D ASCII Gharacter Set, 505

- E Virtual Ground Analysis, 507

Index. 513

1

# Introduction

A technological advance which is affecting the practice of logic design is the existence of the LSI microprocessor; a data flow and control on one to several LSI chips. In this case the logic designer's building blocks are data flows, control stores, and read/write memory chips. He arranges the chips and programs the control store.

Glen G. Langdon, Jr.\*

\*Logic Design: A Review of Theory and Practice. New York: Academic Press, Inc., 1974.

#### 1.1 THE IMPACT OF LSI ON LOGIC DESIGN

The basic goal of logic design is a system that functions as required and is reliable, easy to maintain, and cost effective. As a rule, simplicity of design is the key to the attainment of this goal. Whereas an overly complex design might meet the first requirement, it undoubtedly would fall short in the other areas.

In practical design, of course, cost effectiveness is of great importance. Generally speaking, the most cost effective design is usually the simplest and, because of its simplicity, more reliable and easier to maintain.

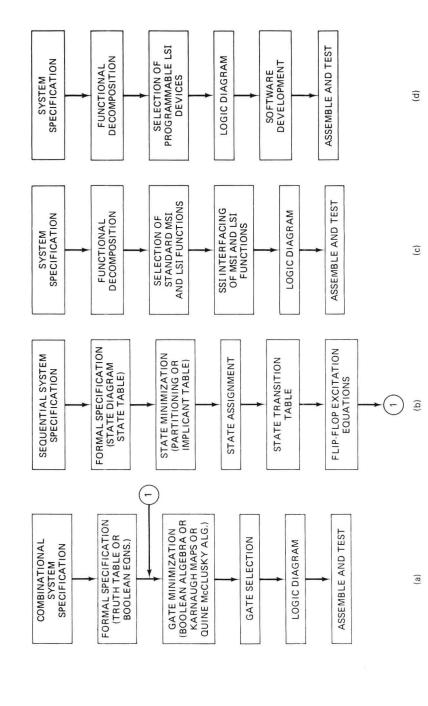

The total cost of a design at the system level includes expenditures for development, components, tooling, assembly, testing, system repair and maintenance, as well as a spare parts inventory. [1,2] This total cost is directly proportional to the number of components in a system, and the number of components has, in the past, been directly proportional to the number of gates and flip-flops. Conventional switching theoretic techniques of digital systems design are geared toward minimizing the number of gates and flip-flops, thereby minimizing the number of components in order to minimize system cost. See Figs. 1.1-1(a) and 1.1-1(b). These minimization techniques were developed originally for systems which used relays to implement gates and flip-flops. As technology advanced, vacuum tubes, then discrete component solid state devices replaced relays. Since the number of components was still proportional to the number of gates and flip-flops, even in designs constructed from vacuum tubes or discrete component solid state devices, the switching theoretic design techniques were still effective in minimizing system cost.

However, in the early 1960's, *Small Scale Integration, SSI*, provided small scale integrated circuits with as many as 12 gates integrated on a single silicon chip and packaged as a single multilead component. With integrated circuits, ICs, the number of components in a system was no longer proportional to the number of gates and flip-flops but was simply equivalent to the number of IC packages in the system. Thus, the reduction of system cost was dependent on the reduction of the total number of IC packages required. Although system designers could still apply the same switching theoretic techniques, simplification of a circuit which reduced the required number of gates or flip-flops resulted in a savings only if it also reduced the number of IC packages.

As IC technology advanced further, *Medium Scale Integration, MSI*, provided circuits with a logic complexity of 13 to 99 equivalent gates per package, and *Large Scale Integration, LSI*, provided circuits with a logic complexity of 100 or more equivalent gates per package, seriously compromising the effectiveness of conventional switching theoretic design techniques in reducing system cost. Fabrication techniques for MSI and LSI circuits, which make it as inexpensive to put 100 or more gates on a chip as 10 destroyed the gate-flip-flop/component-count relationship, and now, for systems implemented with

Flgure 1.1-1. Steps in digital system design: (a) combinational and (b) sequential design using gates and flip-flops (c) design using standard MSI and LSI circuits (d) design using programmable LSI circuits.

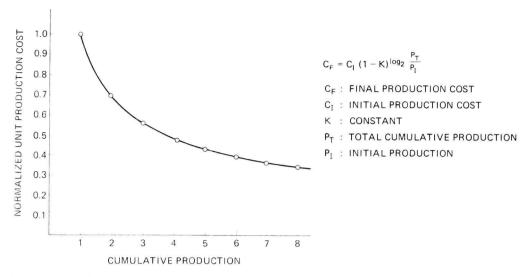

Figure 1.1-2. Semiconductor learning curve.

integrated circuits, total cost is directly proportional to the number of IC packages.<sup>1</sup>

Maximum utilization of LSI results in decreased system costs because LSI circuits provide more logic per package and require less power consumption. And reducing the number of lead connections by replacing many SSI and MSI packages with fewer LSI packages provides greater reliability, since a common source of failure for an IC is at a lead connection to the chip.

The economics of IC manufacture demand that entire functions requiring large numbers of gates be fabricated on a single chip. [3] The complexity of the functions is limited primarily by the chip area required for their fabrication. This area must not exceed that compatible with a high manufacturing yield. *Yield* is the percentage of acceptable ICs resulting from the manufacturing process. To limit the chip area, the number of external connections to the chip, which provide input and output data and control signals, must also be limited.

When medium and large scale integrated functions are produced in large quantities, the production cost can be amortized so that the price of these functions is far less than that of the equivalent functions implemented with SSI circuits. Utilization of standard MSI and LSI functions, although they might include gates which are unused in a particular application, is usually more economical than designing minimized logic implemented at the gate level. See Fig. 1.1-1(c).

<sup>&</sup>lt;sup>1</sup>Exceptions to this relationship occur in LSI systems which use microprocessors. In some applications software development costs may have a greater impact on total system cost than the hardware component count.