INTERNATIONAL STUDENT EDITION

OYONAA ONAWON

J.R. NOWICKI AND L.J. ADAM

# DIGITAL CIRCUITS

# J.R. NOWICKI

Senior Lecturer, Swindon College, Wiltshire

AND L.J. ADAM

Assistant Principal, Blackburn College, Lan

江苏工业学院图书馆 藏 书 章

# **Edward Arnold**

A division of Hodder & Stoughton LONDON MELBOURNE AUCKLAND

### © 1990 J. R. Nowicki and L. J. Adam

First published in Great Britain 1990

Distributed in the USA by Routledge, Chapman and Hall, Inc. 29 West 35th Street, New York, NY 10001

British Library Cataloguing in Publication Data

Nowicki, J.R.

Digital circuits.

- 1. Digital intergrated circuits

- I. Title II. Adam, L.J.

621.381'73

ISBN 0-7131-3641-3

All rights reserved. No part of this publication may be reproduced or transmitted in any form or by any means, electronically or mechanically, including photocopying, recording or any information storage or retrieval system, without either prior permission in writing from the publisher or a licence permitting restricted copying. In the United Kingdom such licences are issued by the Copyright Licensing Agency: 33–34 Alfred Place, London WC1E 7DP.

Typeset in 10/11 pt Times by Colset Private Limited, Singapore Printed and bound in Great Britain for Edward Arnold, a division of Hodder and Stoughton Limited, Mill Road, Dunton Green, Sevenoaks, Kent TN13 2YA by J.W. Arrowsmith Ltd, Bristol

# DIGITAL CIRCUITS

# **PREFACE**

The rapid development of computers, microprocessors and related digital equipment has meant that an increasing number of people have become interested in understanding how these devices work. There is no longer the computer elite that existed a few years ago. The low price of personal computers has meant that the mysteries of computing have been revealed to a large number of non-specialist users. Microcomputers are in use in commerce, industry and the home. The use of computers is not confined to any one category of people – engineers of all persuasions use them for circuit design, numerical control of machine tools, process control, and in many other areas. Business people use computers for data storage, word processing, financial management, and so on. Teachers use them in schools to help children develop an understanding of basic concepts in an interesting way. Home computer 'buffs' and 'hackers' are now commonplace. Some become quite fanatical – perhaps initially attracted by the hypnotic computer games but eventually taking a deeper interest in the inner working of their machines. This usually develops into a desire to expand the system in some way, forcing an interest to develop in the hardware of the computer.

A major area of expansion in recent years has been the telecommunications industry, which is now largely dependent upon digital systems. The modern technologies of satellite systems and robotics are under intense development. The end result of this is that there is a continuing demand for expertise in the fields of digital systems and computing. This book is intended to provide a starting point for those interested in finding out about digital circuitry.

Understanding digital circuits involves the acquisition of a number of skills and an appreciation of the basic digital components and systems. An understanding of the binary number system is essential, and this is fully explained in Chapter 2 together with details of the octal and hexadecimal number systems that are closely related to binary. In addition, Chapter 2 introduces a special code used in digital systems for handling decimal number representation.

Logical functions, relating logic circuit inputs and outputs, are described and manipulated using Boolean Algebra, a special form of algebra that allows symbolic representation of logic levels. This is explained in detail in Chapter 3. Simple logic gates are introduced in Chapter 4, which also contains examples of combinations of these gates to form circuits that are of general use. Specific circumstances dictate particular needs, and a study of this

chapter will provide the reader with the ability to design any non-time-dependent logic circuit to fulfil a specialist requirement. This could be anything from a simple interlock circuit to a memory decoding circuit for a microprocessor system. When circuit requirements become more complex, it is necessary to try to keep the number of components to a minimum. This is not because the cost of components is a major factor – if less components are used, power consumption and power dissipation are reduced, the number of connections to be made is less and the manufacturing process is simplified. In addition, the simpler a circuit is, the less likely (in general) it is to go wrong. Chapter 5 explains accordingly the various minimisation techniques available. Chapter 6 investigates the electrical aspects of digital circuitry and describes the major logic families available to the circuit designer, with the associated electrical implications. The assumption is made in Chapter 6 that the reader has some familiarity with simple transistor and associated electronics.

Temporary storage is of vital importance in digital systems, and Chapter 7 introduces the flip-flop or bistable, a device which can store a 0 or a 1. Registers, which are devices to store groups of 0s and 1s, are described in detail in Chapter 8, and Chapter 9 introduces the many types of counters that are used to produce particular sequences of patterns of 0s and 1s. Chapter 10 deals with logic circuits that perform arithmetic functions including addition, subtraction, multiplication and division.

There are many options available to the circuit designer when implementing a design. Chapter 11 deals with methods of implementation of digital circuits and includes details of logic arrays and multiplexers. Chapter 11 also introduces digital fault finding techniques and equipment. Chapter 12 examines the way in which bit patterns are used to represent a variety of quantities or operations including numbers, memory addresses and operations in computers and analogue equipment, illustrating the range of codes available for the various applications. Many coding circuits are introduced as examples of applications of the techniques of combinational and sequential logic design introduced in the text.

Appendix A gives some design exercises which can all be implemented using integrated circuits and which are suitable for laboratory exercises. Appendix B details advanced minimisation techniques, and Appendix C describes a practical circuit for a 12 or 24 hour clock which can be implemented using simple integrated circuits.

Swindon, 1989

# **CONTENTS**

| Pre | face                                                                                                        |                                                                           | v                                                                                |

|-----|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 1   | Digit                                                                                                       | al circuits and their application                                         | 1                                                                                |

|     | 1.1<br>1.2<br>1.3<br>1.4                                                                                    | Introduction Electrical aspects Applications of digital circuits Problems | 1<br>1<br>4<br>9                                                                 |

| 2   | Number systems                                                                                              |                                                                           |                                                                                  |

|     | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11<br>2.12<br>2.13<br>2.14<br>2.15 | Binary coded decimal numbers                                              | 11<br>12<br>12<br>14<br>15<br>16<br>17<br>19<br>22<br>25<br>27<br>29<br>33<br>35 |

| 3   | Logi                                                                                                        | c algebra                                                                 | 37                                                                               |

|     | 3.1<br>3.2<br>3.3<br>3.4                                                                                    | Introduction Logical operations The NOT operation The AND operation       | 37<br>37<br>38<br>38                                                             |

# viii Contents

|   | 3.5<br>3.6                                                                                                                                    | The OR operation Other combinational operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 40<br>40                                                                                              |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

|   | 3.7                                                                                                                                           | Theorems and laws of logic algebra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 42                                                                                                    |

|   | 3.8                                                                                                                                           | Simplification of logic functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 47                                                                                                    |

|   | 3.9                                                                                                                                           | Summary of useful identities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 51                                                                                                    |

|   | 3.10                                                                                                                                          | Functions of two variables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 51                                                                                                    |

|   | 3.11                                                                                                                                          | Derivation of a function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 52                                                                                                    |

|   | 3.12                                                                                                                                          | Minterm and maxterm forms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 53                                                                                                    |

|   | 3.13                                                                                                                                          | Canonical form                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 54                                                                                                    |

|   | 3.14                                                                                                                                          | Problems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 56                                                                                                    |

| 4 | Com                                                                                                                                           | binational logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 58                                                                                                    |

|   | 4.1                                                                                                                                           | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 58                                                                                                    |

|   | 4.2                                                                                                                                           | Basic logic elements and symbols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 58                                                                                                    |

|   | 4.3                                                                                                                                           | The AND, OR and NOT gates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 60                                                                                                    |

|   | 4.4                                                                                                                                           | The NAND and NOR gates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 62                                                                                                    |

|   | 4.5                                                                                                                                           | Forcing function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 63                                                                                                    |

|   | 4.6                                                                                                                                           | Implementation of the NOT gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 64                                                                                                    |

|   | 4.7                                                                                                                                           | Implementation of algebraic expressions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 65                                                                                                    |

|   | 4.8                                                                                                                                           | Gate equivalents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 67                                                                                                    |

|   | 4.9                                                                                                                                           | Exclusive-OR logic implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 69                                                                                                    |

|   | 4.10                                                                                                                                          | Exclusive-OR applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 70                                                                                                    |

|   |                                                                                                                                               | Exclusive-NOR logic implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 74                                                                                                    |

|   | 4.12<br>4.13                                                                                                                                  | One-bit magnitude comparator Problems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 75<br>77                                                                                              |

|   |                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                       |

| 5 | Minii                                                                                                                                         | nisation techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 80                                                                                                    |

| 5 |                                                                                                                                               | nisation techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                       |

| 5 | 5.1                                                                                                                                           | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 80                                                                                                    |

| 5 | 5.1<br>5.2                                                                                                                                    | Introduction Algebraic minimisation techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 80<br>80                                                                                              |

| 5 | 5.1<br>5.2<br>5.3                                                                                                                             | Introduction Algebraic minimisation techniques Veitch diagram and Karnaugh map                                                                                                                                                                                                                                                                                                                                                                                                                                             | 80<br>80<br>81                                                                                        |

| 5 | 5.1<br>5.2<br>5.3<br>5.4                                                                                                                      | Introduction Algebraic minimisation techniques Veitch diagram and Karnaugh map Simplification of Boolean functions using Karnaugh maps                                                                                                                                                                                                                                                                                                                                                                                     | 80<br>80<br>81<br>85                                                                                  |

| 5 | 5.1<br>5.2<br>5.3                                                                                                                             | Introduction Algebraic minimisation techniques Veitch diagram and Karnaugh map                                                                                                                                                                                                                                                                                                                                                                                                                                             | 80<br>80<br>81                                                                                        |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6                                                                                                        | Introduction Algebraic minimisation techniques Veitch diagram and Karnaugh map Simplification of Boolean functions using Karnaugh maps Tabular minimisation                                                                                                                                                                                                                                                                                                                                                                | 80<br>80<br>81<br>85<br>95                                                                            |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6                                                                                                        | Introduction Algebraic minimisation techniques Veitch diagram and Karnaugh map Simplification of Boolean functions using Karnaugh maps Tabular minimisation Problems                                                                                                                                                                                                                                                                                                                                                       | 80<br>80<br>81<br>85<br>95<br>98                                                                      |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6                                                                                                        | Introduction Algebraic minimisation techniques Veitch diagram and Karnaugh map Simplification of Boolean functions using Karnaugh maps Tabular minimisation Problems  Characteristics of logic families Introduction                                                                                                                                                                                                                                                                                                       | 80<br>80<br>81<br>85<br>95<br>98                                                                      |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>The c                                                                                               | Introduction Algebraic minimisation techniques Veitch diagram and Karnaugh map Simplification of Boolean functions using Karnaugh maps Tabular minimisation Problems  Characteristics of logic families                                                                                                                                                                                                                                                                                                                    | 80<br>80<br>81<br>85<br>95<br>98                                                                      |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>The c                                                                                               | Introduction Algebraic minimisation techniques Veitch diagram and Karnaugh map Simplification of Boolean functions using Karnaugh maps Tabular minimisation Problems Characteristics of logic families Introduction Logic families                                                                                                                                                                                                                                                                                         | 80<br>80<br>81<br>85<br>95<br>98<br>99                                                                |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>The c                                                                                               | Introduction Algebraic minimisation techniques Veitch diagram and Karnaugh map Simplification of Boolean functions using Karnaugh maps Tabular minimisation Problems  Characteristics of logic families Introduction Logic families The bipolar transistor as a switch                                                                                                                                                                                                                                                     | 80<br>80<br>81<br>85<br>95<br>98<br>99<br>100                                                         |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>The c<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6                                                     | Introduction Algebraic minimisation techniques Veitch diagram and Karnaugh map Simplification of Boolean functions using Karnaugh maps Tabular minimisation Problems  Characteristics of logic families Introduction Logic families The bipolar transistor as a switch Diode-transistor logic (DTL) Transistor-transistor logic (TTL) Totem pole output                                                                                                                                                                    | 80<br>80<br>81<br>85<br>95<br>98<br>99<br>100<br>100<br>104<br>110                                    |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>The c<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7                                              | Introduction Algebraic minimisation techniques Veitch diagram and Karnaugh map Simplification of Boolean functions using Karnaugh maps Tabular minimisation Problems  Characteristics of logic families Introduction Logic families The bipolar transistor as a switch Diode-transistor logic (DTL) Transistor-transistor logic (TTL) Totem pole output Other TTL gates                                                                                                                                                    | 80<br>80<br>81<br>85<br>95<br>98<br>99<br>100<br>100<br>104<br>110                                    |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>The c<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8                                       | Introduction Algebraic minimisation techniques Veitch diagram and Karnaugh map Simplification of Boolean functions using Karnaugh maps Tabular minimisation Problems  Characteristics of logic families Introduction Logic families The bipolar transistor as a switch Diode-transistor logic (DTL) Transistor-transistor logic (TTL) Totem pole output Other TTL gates Schottky TTL                                                                                                                                       | 80<br>80<br>81<br>85<br>95<br>98<br>99<br>100<br>100<br>104<br>110<br>113<br>116                      |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>The c<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9                                | Introduction Algebraic minimisation techniques Veitch diagram and Karnaugh map Simplification of Boolean functions using Karnaugh maps Tabular minimisation Problems  Characteristics of logic families Introduction Logic families The bipolar transistor as a switch Diode-transistor logic (DTL) Transistor-transistor logic (TTL) Totem pole output Other TTL gates Schottky TTL PMOS and NMOS logic families                                                                                                          | 80<br>80<br>81<br>85<br>95<br>98<br>99<br>100<br>100<br>104<br>110<br>113<br>116<br>119               |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br><b>The c</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10                 | Introduction Algebraic minimisation techniques Veitch diagram and Karnaugh map Simplification of Boolean functions using Karnaugh maps Tabular minimisation Problems  Characteristics of logic families Introduction Logic families The bipolar transistor as a switch Diode-transistor logic (DTL) Transistor-transistor logic (TTL) Totem pole output Other TTL gates Schottky TTL PMOS and NMOS logic families Complementary metal oxide semiconductor (CMOS) logic                                                     | 80<br>80<br>81<br>85<br>95<br>98<br>99<br>100<br>104<br>110<br>113<br>116<br>119<br>120               |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br><b>The c</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11         | Introduction Algebraic minimisation techniques Veitch diagram and Karnaugh map Simplification of Boolean functions using Karnaugh maps Tabular minimisation Problems  Characteristics of logic families Introduction Logic families The bipolar transistor as a switch Diode-transistor logic (DTL) Transistor-transistor logic (TTL) Totem pole output Other TTL gates Schottky TTL PMOS and NMOS logic families Complementary metal oxide semiconductor (CMOS) logic High speed CMOS (HCMOS)                             | 80<br>80<br>81<br>85<br>95<br>98<br>99<br>100<br>104<br>110<br>113<br>116<br>119<br>120<br>123        |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br><b>The c</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11<br>6.12 | Introduction Algebraic minimisation techniques Veitch diagram and Karnaugh map Simplification of Boolean functions using Karnaugh maps Tabular minimisation Problems  Characteristics of logic families Introduction Logic families The bipolar transistor as a switch Diode-transistor logic (DTL) Transistor-transistor logic (TTL) Totem pole output Other TTL gates Schottky TTL PMOS and NMOS logic families Complementary metal oxide semiconductor (CMOS) logic High speed CMOS (HCMOS) Emitter-coupled logic (ECL) | 80<br>80<br>81<br>85<br>95<br>98<br>99<br>100<br>104<br>110<br>113<br>116<br>119<br>120<br>123<br>126 |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br><b>The c</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11         | Introduction Algebraic minimisation techniques Veitch diagram and Karnaugh map Simplification of Boolean functions using Karnaugh maps Tabular minimisation Problems  Characteristics of logic families Introduction Logic families The bipolar transistor as a switch Diode-transistor logic (DTL) Transistor-transistor logic (TTL) Totem pole output Other TTL gates Schottky TTL PMOS and NMOS logic families Complementary metal oxide semiconductor (CMOS) logic High speed CMOS (HCMOS)                             | 80<br>80<br>81<br>85<br>95<br>98<br>99<br>100<br>104<br>110<br>113<br>116<br>119<br>120<br>123        |

|    |                                                                                                           | Contents ix |

|----|-----------------------------------------------------------------------------------------------------------|-------------|

| 7  | Bistable devices                                                                                          | 135         |

|    | 7.1 Introduction                                                                                          | 135         |

|    | 7.2 NAND gate bistable (NAND latch)                                                                       | 135         |

|    | 7.3 NAND latch applications                                                                               | 140         |

|    | 7.4 Unclocked and clocked SR bistables                                                                    | 141         |

|    | 7.5 Master-slave SR bistable                                                                              | 143         |

|    | 7.6 Master-slave JK bistable                                                                              | 147         |

|    | 7.7 Preset and clear inputs                                                                               | 149         |

|    | 7.8 A TTL JK master-slave bistable                                                                        | 149         |

|    | 7.9 D-type bistable                                                                                       | 150         |

|    | 7.10 T-type bistable                                                                                      | 154         |

|    | 7.11 CMOS bistables                                                                                       | 154         |

|    | <ul><li>7.12 Set-up and hold time</li><li>7.13 Bistable applications</li></ul>                            | 159<br>159  |

|    | 7.14 Problems                                                                                             | 159         |

|    |                                                                                                           |             |

| 8  | Registers                                                                                                 | 161         |

|    | 8.1 Introduction                                                                                          | 161         |

|    | 8.2 Register input/output techniques                                                                      | 161         |

|    | 8.3 Labelling of individual stages of registers and counte                                                |             |

|    | 8.4 Serial transmission                                                                                   | 163         |

|    | <ul><li>8.5 Serial input, serial output shift register</li><li>8.6 Bidirectional shift register</li></ul> | 163<br>167  |

|    | 8.7 Parallel transmission                                                                                 | 169         |

|    | 8.8 MOS and CMOS shift registers                                                                          | 175         |

|    | 8.9 Problems                                                                                              | 178         |

| 9  | Counters                                                                                                  | 179         |

|    | 9.1 Introduction                                                                                          | 179         |

|    | 9.2 Asynchronous counters                                                                                 | 179         |

|    | 9.3 Synchronous counters                                                                                  | 192         |

|    | 9.4 Synchronous decade counters                                                                           | 197         |

|    | 9.5 Shift register counters                                                                               | 201         |

|    | 9.6 Synchronous modulo counters                                                                           | 204         |

|    | 9.7 Problems                                                                                              | 209         |

| 10 | Logic circuits to perform arithmetic                                                                      | 210         |

|    | 10.1 Introduction                                                                                         | 210         |

|    | 10.2 Addition of binary numbers                                                                           | 210         |

|    | 10.3 Parallel full adders                                                                                 | 216         |

|    | 10.4 Subtraction of binary numbers                                                                        | 217         |

|    | 10.5 Addition and subtraction in two's complement form                                                    | 219         |

|    | 10.6 Serial binary multipliers                                                                            | 222         |

|    | 10.7 Binary dividers                                                                                      | 226         |

|    | 10.8 Problems                                                                                             | 227         |

| 11 | Integrated circuit implementation                                                                         | 228         |

|    | 11.1 Introduction                                                                                         | 228         |

|    | 11.2 Choice of logic family                                                                               | 229         |

# x Contents

|       | 11.3 Scale of implementation                           | 229 |  |  |  |

|-------|--------------------------------------------------------|-----|--|--|--|

|       | 11.4 Multiplexer logic                                 | 230 |  |  |  |

|       | 11.5 Logic arrays                                      | 232 |  |  |  |

|       | 11.6 Uncommitted logic arrays                          | 234 |  |  |  |

|       | 11.7 Integrated circuit packaging                      | 235 |  |  |  |

|       | 11.8 Breadboarding                                     | 237 |  |  |  |

|       | 11.9 Printed circuit board implementation              | 239 |  |  |  |

|       | 11.10 Test equipment                                   | 241 |  |  |  |

|       | 11.11 Problems                                         | 248 |  |  |  |

| 12    | Codes and coding circuits                              | 250 |  |  |  |

|       | 12.1 Introduction                                      | 250 |  |  |  |

|       | 12.2 Address representation in computers               | 250 |  |  |  |

|       | 12.3 Operation codes in computers                      | 252 |  |  |  |

|       | 12.4 Analogue representation                           | 255 |  |  |  |

|       | 12.5 Encoding circuits                                 | 255 |  |  |  |

|       | 12.6 Alphanumeric codes                                | 255 |  |  |  |

|       | 12.7 Binary coded decimal codes                        | 260 |  |  |  |

|       | 12.8 Gray codes                                        | 269 |  |  |  |

|       | 12.9 Generation of code sequences using counters       | 271 |  |  |  |

|       | 12.10 Coupling between decades in BCD counting systems | 282 |  |  |  |

|       | 12.11 Problems                                         | 284 |  |  |  |

| Ap    | pendix A Design exercises                              | 285 |  |  |  |

| Ap    | pendix B Advanced minimisation techniques              | 287 |  |  |  |

|       | B.1 Introduction                                       | 287 |  |  |  |

|       | B.2 Five-variable Karnaugh maps                        | 287 |  |  |  |

|       | B.3 Six-variable Karnaugh maps                         | 289 |  |  |  |

|       | B.4 Tabular minimisation of five-variable functions    | 290 |  |  |  |

| Ap    | pendix C Digital clock design                          | 301 |  |  |  |

| Index |                                                        |     |  |  |  |

# DIGITAL CIRCUITS AND THEIR APPLICATIONS

### 1.1 Introduction

In analogue electronic circuits, (sometimes called linear circuits), voltage levels can vary continuously. An example of this is a transistor amplifier which can amplify any voltage level within a specified range. Digital circuit voltage levels, however, are restricted to values which are predetermined. In most digital circuits there are only two levels, for example 0 V and 5 V. These voltage levels are referred to as logic levels. With 2-state logic these levels are referred to as either 0 or 1. By grouping 0s and 1s together, digital information can be monitored, modified or stored. This is the basis of operation of the many thousands of types of digital integrated circuits that are now readily available at low cost. This includes devices known as gates, bistables or flip-flops, registers, counters, multiplexers and microprocessors.

# 1.2 Electrical Aspects

It has already been explained that digital circuits generally operate on only two voltage levels. This will be assumed throughout this text. These voltage levels are not standard, however, and different forms of digital circuit (which are manufactured using different processes) may not be directly compatible. This is not an intentional ploy by circuit manufacturers to make life difficult – there are very good reasons for the differences. This

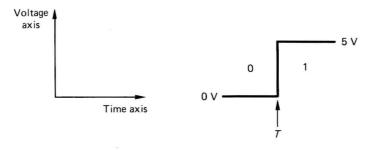

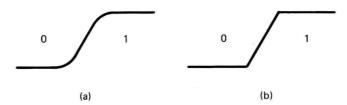

Fig 1.1 Positive-going transition with zero rise time

Fig 1.2 Positive-going transition with appreciable rise time

will become clear when Chapter 6 has been tackled. For the moment, however, particular voltage levels will be assumed. A system representing logic level 0 as 0 V and logic level 1 as 5 V is illustrated in Fig. 1.1.

This shows a waveform representation of logic levels at a **node**, or point in a circuit, that changes from 0 V (logic 0) to 5 V (logic 1) at time T. This is referred to as a **Positive-going transition**; alternatively, the transition at time T can be referred to as a **leading edge**. In reality it is not possible to change a voltage from one value to another instantaneously (zero rise time), and a more realistic impression is given in Fig. 1.2(a). For this reason transitions are often represented as in Fig. 1.2(b). Note that there is a delay, which means that the voltage takes time to rise to its final level.

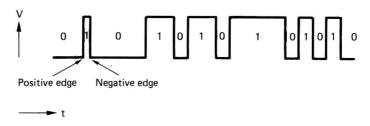

If transitions are excluded, only two voltage levels are possible, so a node in a circuit must be at one or other of these levels at any particular time. This **static** logic level could be checked with a d.c. voltmeter or with an oscilloscope. A sequence of voltage levels would be detected by the voltmeter as a succession of high and low voltages or by the oscilloscope, which traces out the variation of voltage with respect to time, as a waveform showing a series of positive and negative edges. At useful frequencies the d.c. voltmeter would be incapable of following the rapidly changing voltage levels, and an oscilloscope would then be essential. A typical waveform is represented in Fig. 1.3.

Fig 1.3 Waveform display on osculloscope

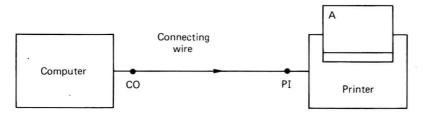

The sequence of 0s and 1s represented in Fig. 1.3 corresponds to **coded** information, for example it could represent a number or a letter of the alphabet. It is a common requirement to transmit such information from one part of a digital system to another – for example a digital computer may require to print the letter 'A' on a printer. One method is to connect the computer to the printer via a **serial** link. This is illustrated in Fig. 1.4.

If the voltage on the computer output (CO) is made to vary with respect to time, as previously shown in Fig. 1.3, the connecting wire will ensure that the same variation takes place at the printer input (PI). If the variation follows a sequence which is the code for the

Fig 1.4 Serial Link between computer and printer

letter 'A', the digital circuitry within the printer will recognise it and cause the 'A' to be printed.

The information, or data, that has been transmitted (i.e, the letter 'A') has been sent in a serial mode. The great advantage of serial transmission is that only one transmission line is required. The disadvantage is that, as only one voltage level can be sent at any one instant, serial transmission is relatively slow. An alternative method is to use parallel transmission as shown in Fig. 1.5.

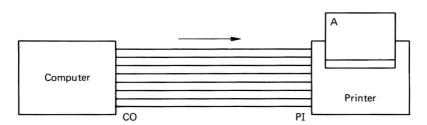

Fig 1.5 Parallel data transmission

With this method, if it is assumed that eight voltage levels are used to define the letter 'A' uniquely then the printer input will receive all the appropriate levels as soon as they are presented at the computer output. Clearly this is a faster method of data transmission than the serial case. The disadvantage of parallel transmission is that a greater number of lines is required, with the resulting penalties of cost and increased construction time.

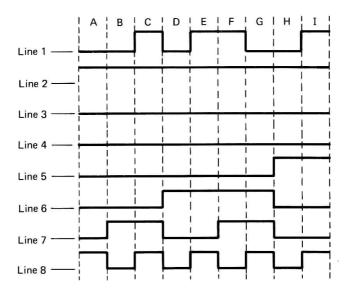

Generally speaking, parallel transmission is used over short distances and serial transmission over long distances where the extra lines would be too expensive. It will of course be required to send further characters to be printed in the example of Fig. 1.5, and all that is necessary is to present the codes in sequence at the computer output, to be received and printed in the same sequence at the printer. An oscilloscope could then be used on each line to show the sequence of voltage levels. The waveforms could be as given in Fig. 1.6 which shows all eight waveforms simultaneously. This shows the changing voltage levels on each line for the transmission of the characters A, B, C, D, E, F, G, H, I to the

In both the serial and parallel transmission examples illustrated, some form of accompanying timing signals would be required to regulate the points at which a new voltage level is transmitted and received.

# 4 Digital Circuits and their Applications

Fig 1.6 Sequence of parallel characters

# 1.3 Applications of Digital Circuits

# Control Applications

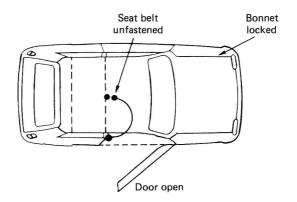

A major application of digital circuits is in the area of process control. A simple example would be a safety device for a motor vehicle. It may be a requirement that the engine will only be allowed to start under certain conditions. These conditions could be:

- (a) The driver's door is closed.

- (b) The driver must be wearing a seat belt.

- (c) The bonnet must be fastened.

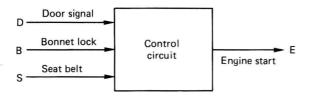

In this simple example each requirement can be defined in two-state terms, i.e. the driver's door will be open or closed, the seat belt will be fastened or unfastened, and the bonnet must be fastened or unfastened. This is illustrated in Fig. 1.7.

Fig 1.7 Simple control example

| Input device | Output signal |           |           |  |

|--------------|---------------|-----------|-----------|--|

| Door         | Bonnet        | Seat belt | To engine |  |

| 0            | 0             | 0         | 0         |  |

| 0            | 0             | 1         | 0         |  |

| 0 .          | 1             | 0         | 0         |  |

| 0            | 1             | 1         | 0         |  |

| 1            | 0             | 0         | 0         |  |

| 1            | 0             | 1         | 0         |  |

| 1            | 1             | 0         | 0         |  |

| 1            | 1             | 1         | 1         |  |

Table 1.1 Tabulation of all possible inputs

A microswitch could be used to detect whether the door is open or closed. If the door is closed the microswitch would generate, say, 5 V to feed to the control circuit. If the door is open, the switch would provide 0 V. If 5 V is assumed to be logic 1 and 0 V is assumed to be logic 0, then a 1 indicates a closed door and a 0 an open door. Similarly a contact in the seat belt fastening could produce a 1 to indicate a fastened seat belt and a 0 to indicate an unfastened seat belt. A fastened bonnet would be a 1 and an unfastened bonnet a logic 0. Only when all of these conditions are satisfied would the engine be allowed to start. The control circuit will only generate a 5 V output, representing permission to start the engine, in that case. A 1 therefore signifies 'enable engine start' and a 0 output 'inhibit engine start'. This is summarised in Table 1.1 above.

Note that only when the door is closed AND the bonnet is locked AND the seat belt is fastened (D = B = S = 1) will the engine be allowed to start (E = 1). A block diagram representing the circuit requirement is shown in Fig. 1.8.

This is an easy task for a digital circuit. The important point to note at this stage is the simple way in which the problem can be defined using logic levels 0 and 1. More complex control problems could be defined in the same way.

Fig 1.8 Circuit requirement

#### Example 1.1

A conveyor belt for a production line at a bottling plant must only be allowed to start under the following conditions:

- (a) Sufficient empty bottles are available at the start of the line.

- (b) The liquid in the bottle filler is higher than a minimum level.

- (c) Sufficient bottle caps are stored in the capping machine hopper.

- (d) Sufficient labels are available in the labelling machine.

- (e) Alternatively an override switch has been set.

Produce a table representing all possible inputs and the corresponding outputs.

# 6 Digital Circuits and their Applications

#### Solution

B = 1 means sufficient bottles.

F = 1 means liquid > minimum level.

C = 1 means sufficient caps.

L = 1 means sufficient labels.

S = 1 means override switch set.

The combinations of input values and resulting outputs are shown in Table 1.2.

|   |   | Inputs |   |   | Output | Inputs |   |   |   | Output |   |

|---|---|--------|---|---|--------|--------|---|---|---|--------|---|

| В | F | С      | L | S |        | В      | F | С | L | S      |   |

| 0 | 0 | 0      | 0 | 0 | 0      | 1      | 0 | 0 | 0 | 0      | 0 |

| 0 | 0 | 0      | 0 | 1 | 1      | 1      | 0 | 0 | 0 | 1      | 1 |

| 0 | 0 | 0      | 1 | 0 | 0      | 1      | 0 | 0 | 1 | 0      | 0 |

| 0 | 0 | 0      | 1 | 1 | 1      | 1      | 0 | 0 | 1 | 1      | 1 |

| 0 | 0 | 1      | 0 | 0 | 0      | 1      | 0 | 1 | 0 | 0      | 0 |

| 0 | 0 | 1      | 0 | 1 | 1      | 1      | O | 1 | 0 | 1      | 1 |

| 0 | 0 | 1      | 1 | 0 | 0      | 1      | 0 | 1 | 1 | 0      | 0 |

| 0 | 0 | 1      | 1 | 1 | 1      | 1      | 0 | 1 | 1 | 1      | 1 |

| 0 | 1 | 0      | 0 | 0 | 0      | 1      | 1 | O | 0 | 0      | 0 |

| 0 | 1 | 0      | 0 | 1 | 1      | 1      | 1 | 0 | 0 | 1      | 1 |

| 0 | 1 | 0      | 1 | 0 | 0      | 1      | 1 | 0 | 1 | 0      | 0 |

| 0 | 1 | 0      | 1 | 1 | 1      | 1      | 1 | 0 | 1 | 1      | 1 |

| 0 | 1 | 1      | 0 | 0 | 0      | 1      | 1 | 1 | 0 | 0      | 0 |

| 0 | 1 | 1      | 0 | 1 | 1      | 1      | 1 | 1 | 0 | 1      | 1 |

| 0 | 1 | 1      | 1 | 0 | 0      | 1      | 1 | 1 | 1 | 0      | 1 |

| 0 | 1 | 1      | 1 | 1 | 1      | 1      | 1 | 1 | 1 | 1      | 1 |

Table 1.2 Solution to Example 1.1

Study Table 1.2 to confirm an understanding of the solution. Using this technique, digital circuits can be designed to control any industrial process. Consider the case of a nuclear power station with its comprehensive interlock systems to ensure safety. Digital circuits can monitor a variety of parameters such as reactor temperature and pressure, control rod positions, and so on. Based on these parameter values, the circuit can generate appropriate control signals. Another example would be a railway signalling system which detects train positions and sets signals accordingly.

# Digital Computers and Microprocessor systems

Digital computers have now become a part of everyday life. They are used in offices, banks and institutions of all kinds, in aircraft and in the home. They have endless applications, limited only by the imagination of the human mind. Their great versatility arises from the fact that they are **programmable**. Programs of instructions, or **software**, can be loaded to suit the particular application. These include control applications such as those considered above, so that the problem of Example 1.1 could be solved by a digital computer using a special program.

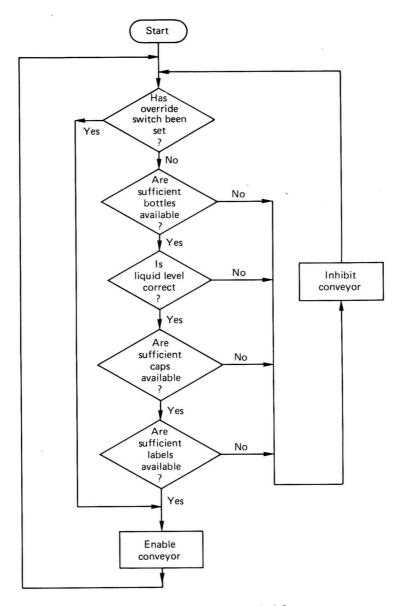

#### Example 1.2

Demonstrate how a program could be devised to solve the problem of Example 1.1 using a digital computer.

### Solution

This can best be illustrated by means of a flowchart, which is a diagrammatic representation of an algorithm solving the problem.

This is given in Fig. 1.9.

Fig 1.9 Flowchart for example 1.2