## SUPERCONDUCTIVITY ELECTRONICS

KO HARA Editor

# SUPERCONDUCTIVITY ELECTRONICS

KO HARA, Editor

#### Copyright © 1987 Ko Hara

The exclusive publication rights to this volume are granted to OHMSHA, LTD. by the copyright owner.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted, in any form or by any means, electronic, mechanical, recording or otherwise, without the prior permission in writing of the copyright owner and the publication rights holder.

ISBN: 4-274-03164-0 (OHMSHA)

ISBN: 0-13-876301-1 (PRENTICE HALL)

Publishers:

OHMSHA, LTD.

3-1 Kanda Nishiki-cho, Chiyoda-ku, Tokyo 101, Japan Sole distributors for Japan and

PRENTICE HALL, INC.

Englewood Cliffs, New Jersey 07632, USA Sole distributors outside Japan

# SUPERCONDUCTIVITY ELECTRONICS

#### Edited by

Ko Hara; Chiba Institute of Technology

#### **Organizing Committee:**

- H. Abe; NEC Corporation

- T. Fujita; Hiroshima University

- T. Goto; The University of Electro-Communications

- S. Hasuo; Fujitsu Laboratories Ltd.

- T. Hattanda; Nippon Telegraph and Telephone Corporation

- I. Iguchi; University of Tsukuba

- U. Kawabe; Hitachi Ltd.

- T. Kobayashi; Osaka University

- S. Kuriki; Hokkaido University

- Y. Okabe; The University of Tokyo

- M. Sugawara; Yokohama National University

- S. Takada; Electrotechnical Laboratory

- T. Yamashita; The Technological University of Nagaoka

- K. Yoshida; Kyushu University

#### **Preface**

This volume summarizes and makes available to overseas as well as domestic researchers in the field of superconductive electronics the outcomes of research and development in this field in Japan. It covers the last five years, i.e., since the Committee on Superconductive Electronics of the Japan Society for the Promotion of Science was established.

Before the committee was established, the Special Research Project on Superconductive Quantum Electronics started a three-year project in 1979 to financially support individual research workers in universities and also discussion and information exchange among researchers in universities, government, and related research institutions as well as industrial organizations. The results of R and D of the Special Project have been summarized in the Proceedings of the Symposium on Superconductive Quantum Electronics (issued March 1983). The key fabrication technology in those days was, roughly speaking, limited to the framework of lead alloy technology following the IBM developments. Nonetheless, Nb and NbN fabrication technology was developed and investigated with great effort during this period. Basic research expanded also during this time in such fields as integration of logic and memory circuit, single flux quantum logic, variety of SQUID applications (NMR, MCG, geophysics, solid state physics etc.), metrology applications (h/2e determination, noise, and temperature measurement), radio frequency applications (Josephson junction oscillator, detection, and mixing of microwave and laser), and weak link fabrication technology of good quality.

Fortunately, following the Special Research Project period, researches as well as population growth in this field in Japan expanded steadily despite world wide deceleration due to the stumbling of IBM's project on the high performance Josephson computer. Integrated circuit technology based on NbN and Nb–Aloxide–Nb junctions has nearly reached its peak, though practical applications must be considered. Fluxoid logic has been intensively studied together with the Josephson sampler to monitor the performance of logic transition. Measurement technology such as Josephson potentiometer and h/2e determination together with quantum Hall resistance are now opening new areas of low temperature quantum metrology. Josephson mixers of various kinds are reaching their ultimate performances. SQUID applications are becoming more and more practical

with combinations of planar signal coupling and Nb related fabrication technology. Improvements in weak link performance are accomplished by a variety of fabrication methods that will find numerous of applications in the future. Of importance are the exploratory trials in Chapter 5 of this volume, among which three terminal devices are of interest, where much more physics is necessitated.

As mentioned above, research and development in this field in Japan have made great progress during the JSPS period. However, effective demonstration and practical applications of this progress proved difficult to achieve. Superconductive electronics must some aspect inevitably compete with semiconductor electronics that is powerful in every aspect of technological, historical, and social viewpoints. Continuous efforts are being made by the superconductive electronics researchers.

Finally, discussion on the recent rapid progress in the high  $T_c$  oxide superconductor have not been included in this volume except for a few contributions. This has, no doubt, a big impact not only as a zero resistance conducting material, but also as a material for superconductivity on R&D electronics. Physics and technology of the thin film of this material (necessarily single crystal) with physically well defined surface for superconductive electronics should be the goal pursued with great effort to gain popularity in the general world.

Ko Hara

June 1987

### **Contents**

#### **Preface**

| I. | Josephson | Integrated Circuit                                              | . 1 |

|----|-----------|-----------------------------------------------------------------|-----|

|    | I·1 ]     | IC Technology                                                   |     |

|    | 1.        | Josephson IC Technology                                         | . 2 |

|    |           | S. Takada, I. Kurosawa, H. Nakagawa, M. Aoyagi, S. Kosaka,      |     |

|    |           | and F. Shinoki; Electrotechnical Laboratory                     |     |

|    | 2.        | Josephson IC Technology                                         | 10  |

|    |           | K. Hohkawa, M. Yamamoto, K. Kuroda,                             |     |

|    |           | and H. Yoshikiyo; NTT                                           |     |

|    | 3.        | Fabrication Technology for Josephson Integrated Circuits with   |     |

|    |           | Nb/AlO <sub>x</sub> /Nb Junctions                               | 22  |

|    |           | T. Imamura, H. Hoko, S. Ohara, S. Kotani, and S. Hasuo;         |     |

|    |           | Fujitsu Limited                                                 |     |

|    | 4.        | Josephson Logic Circuits                                        | 34  |

|    |           | S. Yano, Y. Hatano, and U. Kawabe; Hitachi Ltd.                 |     |

|    | 5.        | IC Technology                                                   | 46  |

|    |           | Y. Wada, J. Sone, H. Tsuge, J. S. Tsai, S. Tahara, M. Hidaka,   |     |

|    |           | T. Yoshida, I. Ishida, S. Nagasawa, and H. Abe; NEC Corp.       |     |

|    | I·2 I     | Fluxoid Logic Circuit                                           |     |

|    | 1.        | Unilateral Single–Flux–Quantum Logic Gates                      | 58  |

|    |           | T. Sugano and H. Miyake; The Univ. of Tokyo                     |     |

|    | 2.        | Fluxoid Logic Using a Single Flux Quantum                       | 66  |

|    |           | A. Inoue and Y. Okabe; The Univ. of Tokyo                       |     |

|    |           | A. Nakayama; The Univ. of Kanagawa                              |     |

|    | 3.        | Soliton Logic Circuits as Elements of Phase-Mode Josephson      |     |

|    |           | Computer System                                                 | 70  |

|    |           | K. Nakajima and Y. Sawada; Tohoku Univ.                         |     |

|    | 4.        | Fluxon Electronics                                              | 74  |

|    |           | S. Sakai and H. Akoh; Electrotechnical Laboratory.              |     |

|    | 5.        | Control of Soliton Propagation in a Josephson Transmission Line | 78  |

#### A. Matsuda and J. Nitta; NTT

|    | I·3      | Related Technology                                                                    |      |

|----|----------|---------------------------------------------------------------------------------------|------|

|    | 1.       | Josephson Sampler                                                                     | 82   |

|    |          | H. Akoh, S. Sakai, A. Yagi, and S. Takada; Electrotechnical                           |      |

|    |          | Laoratory                                                                             |      |

|    | 2.       | Pico-Second Waveform Observation by Using Josephson Sampler                           | 86   |

|    |          | K. Nakajima, A. Fujimaki, and Y. Sawada; Tohoku Univ.                                 |      |

|    | 3.       | An Ultra-High Speed Josephson Analog-to-Digital Converter                             | 90   |

|    |          | T. Nakanishi and H. Yoshikiyo; NTT                                                    |      |

|    | 4.       | Computer Simulations for Josephson Logic System                                       | 94   |

|    |          | M. Morisue and H. Hosoya; Saitama Univ.                                               |      |

|    | 5.       | Flux Trapping in Electrodes of Josephson Tunnel Junctions                             | 98   |

|    |          | F. Irie; Kinki Univ.                                                                  |      |

|    |          | N. Uchida, K. Enpuku, and K. Yoshida; Kyushu Univ.                                    |      |

| II | Analogue | Application                                                                           | 103  |

|    | П∙1      | Standard                                                                              |      |

|    |          |                                                                                       | 104  |

|    | 1.       | Josephson Potentiometer and Its Application                                           | 104  |

|    |          | Y. Murayama, Y. Sakamoto, and M. Koyanagi;                                            |      |

|    | 2        | Electrotechnical Laboratory  Absolute Messurement of the Messure Flux Quentum Using a |      |

|    | 2.       | 8                                                                                     | 100  |

|    |          | Superconducting Magnetic Levitation System                                            | 109  |

|    |          | F. Shiota; National Research Laboratory of Metrology                                  |      |

|    | 2        | K. Hara; Chiba Institute of Technology                                                |      |

|    | 3.       | Point–Contact Josephson Mixer for Frequency Measurement of FIR Lasers                 | 112  |

|    |          |                                                                                       | 113  |

|    |          | Y. Miki and E. Sakuma; National Research Laboratory of Metorology                     |      |

|    | 4.       | Quantized Hall Resistance                                                             | 117  |

|    | ٦.       | K. Shida; Electrotechnical Laboratory                                                 | 11/  |

|    |          | K. Shida, Electrotechnical Edobratory                                                 |      |

|    | II·2     | Josephson Mixers                                                                      |      |

|    | 1.       | An All–Niobium SIS Mixer for Radio Astronomy                                          | 121  |

|    |          | J. Inatani, T. Kasuga, A. Sakamoto, and M. Tsuboi;                                    | 121  |

|    |          | Nobeyama Radio Observatory                                                            |      |

|    | 2.       | Characteristics of Josephson Harmonic Mixers                                          | 125  |

|    | 2.       | K. Fujisawa and S. Kita; Osaka Univ.                                                  | . 23 |

|    | 3.       | The Evaluation of the Characteristics of Superconducting Mixers                       |      |

|    | ٥.       | in the Submillimeter Region                                                           | 129  |

|    |          | K. Sakai, M. Kobayashi, T. Takami, and S. Ohara;                                      | . 27 |

|    |          | Osaka Univ.                                                                           |      |

|     |            | Y. Hayashi and H. Ogawa; Nagoya Univ.                          |      |

|-----|------------|----------------------------------------------------------------|------|

|     | 4.         | Quasiparticle 30 GHz Mixer with A Nb-Based SIS Junction        | 133  |

|     |            | T. Noguchi, T. Takami, and K. Hamanaka;                        |      |

|     |            | Mitsubishi Electric Corp.                                      |      |

|     |            | COVID                                                          |      |

|     | II·3       | SQUID                                                          | 127  |

|     | 1.         | Integrated DC-SQUID Magnetometer                               | 13/  |

|     |            | M. Nakanishi, M. Koyanagi, S. Kosaka, A. Shoji, M. Aoyagi,     |      |

|     | 2          | and F. Shinoki; Electrotechnical Laboratory                    | 1.40 |

|     | 2.         | DC SQUIDS Using NbN Base Electrode Junctions                   | 140  |

|     | 2          | S. Kuriki, M. Matsuda, and K. Mizuno; Hokkaido Univ.           |      |

|     | 3.         | DC SQUID Using Niobium Thin–Film Point–Contact Josephson       | 144  |

|     |            | Junctions                                                      | 144  |

|     |            | S. Naito, Y. Higashino, and G. Uehara; Yokogawa Electric Corp. |      |

|     | 4.         | Integrated Thin–Film DC SQUID                                  | 1/10 |

|     | <b>4</b> , | N. Ohkawa, T. Noguchi, and K. Hamanaka;                        | 140  |

|     |            | Mitsubishi Electric Corp.                                      |      |

|     | 5.         | DC SQUID with a Resistively Shunted Inductance                 | 152  |

|     | 3.         | K. Enpuku and K. Yoshida; Kyushu Univ.                         | 132  |

|     | 6.         | Magnetic Measurements by SQUID Magnetometer                    | 156  |

|     | 0.         | Y. Takahashi and Y. Yamada; Shimadzu Corporation               | 150  |

|     | 7.         | Neuromagnetic Fields Measured with a SQUID                     | 160  |

|     |            | S. Kuriki, Y. Mizutani, and Y. Isobe; Hokkaido Univ.           | 100  |

|     | 8.         | Measurement of Magnetic Field Produced by Human Body with      |      |

|     |            | SQUID Magnetometer                                             | 164  |

|     |            | M. Kotani, K. Aihara, and Y. Uchikawa; Tokyo Denki Univ.       |      |

|     | 9.         | Graphic Studies on Magnetocardiograms                          | 168  |

|     |            | N. Awano; Fukushima Biomedical Institute of Environmental      |      |

|     |            | Disease,                                                       |      |

|     |            | Y. Sakauchi, K. Ohwada, and S. Kariyone;                       |      |

|     |            | Fukushima Medical College                                      |      |

|     | 10.        | Vector SQUID Magnetometer for Biomagnetic Measurement          | 172  |

|     |            | K. Shirae and H. Furukawa; Osaka Univ.                         |      |

| III | Device F   | abriction                                                      | 177  |

|     | Device     |                                                                | 1//  |

|     | III·1      | <b>Tunnel Josephson Junctions</b>                              |      |

|     | 1.         | High Quality Nb/AlO <sub>x</sub> /Nb Josephson Junctions       | 178  |

|     |            | S. Morohashi and S. Hasuo; Fujitsu Limited                     |      |

|     | 2.         | NbN/MgO/NbN Josephson Tunnel Junctions                         | 182  |

|     |            | A. Shoji, M. Aoyagi, S. Kosaka, and F. Shinoki;                |      |

|     |            | Electrotechnical Laboratory                                    |      |

|    | 3.      | All–Nb Josephson Junction Using Artificial Barriers          | 186 |

|----|---------|--------------------------------------------------------------|-----|

|    |         | O. Michikami, K. Tanabe, H. Asano, and Y. Katoh; NTT         |     |

|    | 4.      | Epitaxial NbN Josephson Junction                             | 190 |

|    |         | K. Hamasaki, T. Komata, and T. Yamashita;                    |     |

|    |         | The Technological Univ. of Nagaoka                           |     |

|    | III·2   | Weak Links                                                   |     |

|    | 1.      |                                                              | 194 |

|    |         | K. Hamasaki and T. Yamashita; The Technological Univ.        |     |

|    |         | of Nagaoka                                                   |     |

|    | 2.      |                                                              | 198 |

|    |         | M. Nakanishi; Electrotechnical Laboratory,                   |     |

|    |         | G. Uehara; Yokogawa Electric Works                           |     |

|    |         | K. Hara; Chiba Institute of Technology                       |     |

|    | 3.      | 122                                                          |     |

|    |         | Normal–Super Bilayers                                        | 202 |

|    |         | K. Fukuoka, M. Takatsu, and Y. Okabe;                        |     |

|    |         | The Univ. of Tokyo                                           |     |

|    | 4.      |                                                              | 206 |

|    |         | S. Yoshimori and M. Kawamura; Tokyo Institute of Technology  |     |

|    | 5.      |                                                              |     |

|    |         | T. Goto and Y. Takeda; The Univ. of Electro-Communications   |     |

|    | 6.      |                                                              | 214 |

|    |         | Y. Saito, K. Nagaseki, and S. Suganomata; The Univ.          |     |

|    |         | of Yamanashi                                                 |     |

|    | 7.      | Fabrication of Vertical Type Microbridges by Using Focused   |     |

|    |         | Ion Beams                                                    | 218 |

|    |         | K. Sera, K. Gamo, and S. Namba; Osaka Univ.                  |     |

| IV | Materia | l and Device Physics                                         | 222 |

| 11 | Materia | and Device I hysics                                          | 223 |

|    | 1.      | Niobium Single-Crystal Thin Films                            | 224 |

|    |         | G. Oya and Y. Sawada; Tohoku Univ.                           |     |

|    | 2.      | Superconducting $BaPb_{1-x}Bi_xO_3$ Film and Its Application | 228 |

|    |         | T. Murakami, M. Suzuki, Y. Enomoto, K. Moriwaki,             |     |

|    |         | and Y. Hidaka; NTT                                           |     |

|    | 3.      | Oxide Superconductors–High T <sub>c</sub> Superconductivity  | 232 |

|    |         | H. Takagi, S. Uchida, K. Kishio, K. Kitazawa,                |     |

|    |         | K. Fueki and S. Tanaka; The Univ. of Tokyo                   |     |

|    | 4.      | Josephson Network with Randomly Arrayed Fine Particles       | 236 |

|    |         | S. Kobayashi and T. Karasawa; The Univ. of Tokyo             |     |

|    |         | Y. Tada; Kawasaki Steel Co.                                  |     |

|    | 5.      | Organic Superconductor                                       | 240 |

|    |         |                                                              |     |

|    |                  | M. Tokumoto and K. Murata; Electrotechnical Laboratory    |         |

|----|------------------|-----------------------------------------------------------|---------|

|    | 6.               | Approach to the Room-Temperature Superconductor           | 244     |

|    |                  | <b>11. 1, 2</b>                                           |         |

| V  | Explorato        | ry Devices                                                | 251     |

|    | 1.               | Josephson Point–Contact Tunnel Junction                   | 252     |

|    |                  | S. Imai, S. Morita, Y. Takeuchi, and N. Mikoshiba;        |         |

|    | _                | Tohoku Univ.                                              | 251     |

|    | 2.               | Magnetic Barrier Tunnel Junction                          | 256     |

|    |                  | S. Imai, S. Morita, Y. Takeuchi, and N. Mikoshiba;        |         |

|    |                  | Tohoku Univ.                                              | 260     |

|    | 3.               | Flux-Flow Device                                          | 260     |

|    |                  | K. Yoshida and K. Enpuku; Kyushu Univ.                    |         |

|    |                  | F. Irie; Kinki Univ.                                      |         |

|    | 4.               | Abrikosov Vortex Memory                                   | 264     |

|    |                  | K. Miyahara, M. Mukaida, and K. Hohkawa; NTT              |         |

|    | 5.               | Quasiparticle Injection Device                            | 268     |

|    |                  | I. Iguchi; The Univ. of Tsukuba                           |         |

|    | 6.               | Phase-Quantum-Tunnel Junction                             | 273     |

|    |                  | M. Sugahara, N. Yoshikawa, M. Tayama, T. Akeyoshi,        |         |

|    |                  | and M. Kojima; Yokohama National Univ.                    |         |

|    | 7.               | Phase Cupled Squid                                        | 277     |

|    |                  | T. Yamashita; The Technological Univ. of Nagaoka          |         |

|    | 8.               | Voltage–Induced Modulation of Josephson Current           | 281     |

|    |                  | Y. Okabe and K. Takeuchi; The Univ. of Tokyo              |         |

|    | 9.               | InAs Coupled Superconducting Device                       | 285     |

|    |                  | T. Kawakami, H. Takayanagi, and K. Inoue; NTT             |         |

|    | 10.              | Superconducting Transistor                                | 289     |

|    |                  | T. Nishino, M. Hatano, and U. Kawabe; Hitachi, Ltd.       |         |

|    | 11.              | A Superconducting–Base Transistor                         | 293     |

|    |                  | H. Tamura, N. Fujimaki, and S. Hasuo;                     |         |

|    |                  | Fujitsu Laboratories Ltd.                                 |         |

|    | 12.              | Superconductor–Base Hot–Electron Transistors              | 297     |

|    |                  | T. Kobayashi and M. Tonouchi; Osaka Univ.                 |         |

| VI | <b>Cooling T</b> | Cechnology                                                | 301     |

|    |                  |                                                           |         |

|    | 1.               | Magnetic Refrigerator as a Cryocooler for Cryoelectronics | 302     |

|    |                  | H. Ogiwara and H. Nakagome; Toshiba Research              |         |

|    |                  | & Development Center                                      | <u></u> |

|    | 2.               | Cooling System for Superconducting Devices                | 310     |

|    |                  | T. Morita: Sumitomo Heavy Industries I td                 |         |

### I JOSEPHSON INTEGRATED CIRCUIT

- 1 IC TECHNOLOGY

- 2 FLUXOID LOGIC CIRCUIT

- 3 RELATED TECHNOLOGY

#### I-1-1 JOSEPHSON IC TECHNOLOGY

S.Takada, I.Kurosawa, H.Nakagawa, M.Aoyagi, S.Kosaka, and F.Shinoki

Electrotechnical Laboratory 1-1-4 Umezono, Sakuramura, Niiharigun, Ibaraki 305 Japan

#### **ABSTRACT**

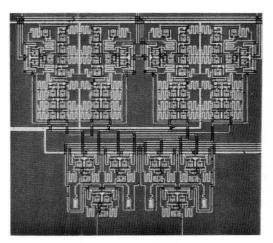

A Josephson integrated circuit(IC) technology developed at ETL for high speed digital applications is reviewed. Logic circuit technology using a 4JL(four junction logic) gate family is presented. Various circuits such as 2-bit ALU(arithmetic logic unit) and 4-bit shift-register have been developed using an Nb/Al-oxide/Nb junction technology. A new approach for realizing Josephson RAM(random access memory) in which the variable threshold memory cells are integrated is described. A more advanced technology of all-refractory planarization process has been developed and adapted to fabricate a 4x4-bit multiplier chip, in which more than 2800 Josephson junctions are integrated. The 4-bit multiplication was achieved in 1ns. A new fabrication process of CLIP(cross line pattern) method for integrating sub-micron NbN junctions in LSI chips has been developed, that shows small spreads in Josephson critical currents.

#### INTRODUCTION

Josephson digital LSIs have been expected to have high performance in both circuit speed and power dissipation. The superconducting digital system based on Josephson IC technology has also great advantages for realizing ultra-high speed computers because of extremely low loss and distortion for high speed signal transmission made by superconducting strip lines. Josephson integrated circuit technology has been evolved with the lead-alloy technology developed by IBM groups[1]. A number of circuits were demonstrated using this technology. More recently, Josephson IC technology has been accelerated by refractory junction technology such as NbN/ NbN[2] and Nb/ Nb[3]. Material research, integration process and circuit design have also been developed extensively. The circuits fabricated using refractory materials show higher performance than that of conventional devices.

In this paper, a new approach for Josephson IC technology developed at ETL is reviewed. First, the logic circuit technology based on a 4JL-gate family shows a feasibility to realize digital systems. Both combination logic circuits(2-bit ALU and 4-bit multiplexer) and sequential logic circuits(4-bit shift-register and 4-bit counter) have been developed. Second, the principle of a new Josephson memory cell named variable threshold memory is described. The cell has been extended to integrate a 1k-bit cell plane. Third, the all-refractory planarization process including spin-on glass process has been successfully demonstrated to develop a 4x4-bit multiplier circuit, which has a complexity at LSI level. Finally, a sub-micron tunnel junction process which is adaptable to integrate junctions with precise dimensions is discussed.

#### LOGIC CIRCUIT TECHNOLOGY USING 4JL-GATE

The 4JL-gate[4][5] consists of four Josephson junctions which are directly coupled in a closed loop. In this 4JL-gate, operating characteristics are essentially determined by the phase relations of the individual junctions, which gives us a wide fabrication tolerance in integrated circuits. The elimination of the inductances in the closed loop makes it possible to reduce the device size, resulting in faster switching speed. In fact, the delay time of 7ps at a power dissipation of 4µW has been achieved in a ten-stage chain of the 4JL-gates with 2.5µm square junctions[6].

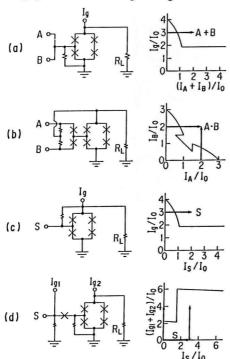

A 4JL-gate family is designed for making integrated logic circuit. Figure 1 shows schematic configurations of the 4JL-family gates; (a) two-input OR-, (b) two-input AND-, (c) AMP- and (d) timed

INVERT-gates, and their threshold curves, respectively[7]. Wide operating margin of more than  $\pm 35\%$  is obtained in each gate. In this gate family, the current-isolation function between input and output is performed by the OR-gate. OR-AND gate-cell[8] is useful to construct the circuits systematically. The AMP-gate is used to obtain a fan-out of 4.

A data-latch function is quite important in logic circuits, especially in sequential logics. A directly-coupled data-latch[9] which consists of five 4JL-gates and two single junctions is developed. The circuit

configuration is shown in Fig. 2. The latch can generate dual outputs of true(T) and complement(C), driving by a two-phase power supply P1 and P2 as is described in the figure. Single junctions Jp and Jn prevent the input signal from free-running for overlap-interval of P1 and P2.

A flip-flop function is achieved to make a feedback loop by using two data-latch circuits. This data-latch do not need any inductances for the data storage, so that the sequential circuit size can be reduced, resulting high speed operations.

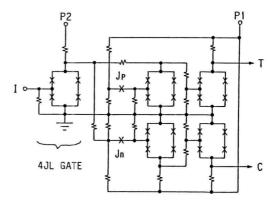

Nb/Al-oxide/Nb junctions were used to make Josephson integrated logic circuits. In order to integrate small junctions with high Vm, an Nb underlayer[10] was introduced. Figure 3 shows a cross section of the circuit. A junction sandwich with a 2-inch Si wafer size was first made on the Nb underlayer which was defined by the base-electrode pattern. The tunnel barrier was made by thermal oxidation of the Al film surface with a pure oxygen gas of 1 torr at ambient temperature. Each junction was defined by an RIE(reactive ion etching) process with CF4 gas. MgO thin

Fig.1. 4JL-family gates and their threshold curves.

Fig.2. Direct-coupled data-latch.

Fig.3. Schematic cross section of the circuit.

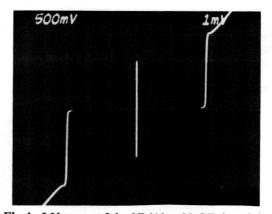

Fig.4. I-V curve of the Nb/Al-oxide/Nb junction. Vertical:0.5mA/div, horizontal:1mV/div.

film[11] protects a SiO layer on a ground plane during the RIE process. Insulations between each junction were performed with a self-aligned SiO evaporated film[12]. Interconnections of the junctions and Au-In resistors were done by Pb-In alloy wiring. An example of current-voltage characteristics of the Nb/Al-oxide/Nb junction fabricated is shown in Fig.4. A gap-voltage of 2.8mV and a Vm of up to 50mV are shown.

Josephson 2-bit ALU circuit[13] was designed using the 4JL-family gates. In order to obtain a high speed logic operations, a carry-look ahead logic is introduced instead of ripple carry one.

The circuit was designed based on the 3µm Nb/Al-oxide/Nb junction (Vg=2.8mV, Vm=50mV) and an impedance(Zo=14ohm) of the 3µm-superconducting strip line. The 3µm ORgate has a maximum gate current Im=0.2mA. The OR-gate can be operated at a nominal bias current of 0.75·Im with a power dissipation of 1.7µW.

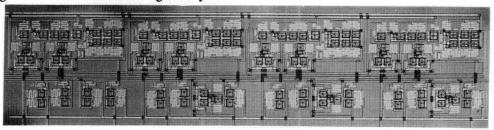

The Josephson 2-bit ALU circuit was fabricated using the 3µm Nb/Al-oxide/Nb junction process. A photograph of the circuit fabricated is shown in Fig.5. 178 4JL-family gates are integrated in the circuit. The circuit size is about 0.8mm x 2mm.

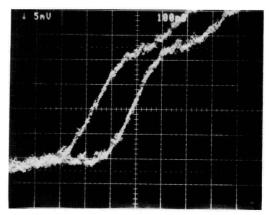

The ALU was tested at 4.2K supplying monopolar pulse current to a power line with a Josephson regulator. Every ALU operation of 32 kinds of arithmetic/logic functions was confirmed completely. Delay time measurements of the ALU were also performed in the power current range between 50mA and 93mA. A constant delay time of 225ps was measured in the power current range between 50mA and 70mA at the operation of A•B function. This constant delay time is due to a regulated power voltage which is delivered to each 4JL-gate. Figure 6 shows the output waveforms obtained for delay time measurement at the power current of 93mA, which gave the fastest operation. Time interval of two waveforms shows the delay time of 157ps which corresponds 12 stages of the logic gates. The power dissipation of the ALU is 580µW. By computer simulations, operating time of the ALU was estimated to be 180ps with a power dissipation of 261µW at the nominal bias condition.

The ALU was designed based on a bit-slice configuration which extends bit-length easily. 16-

Fig.5. 2-bit ALU circuit fabricated with 3µm Nb/Al-oxide/Nb junction technology.

Fig.6. Output waveforms of the ALU for delay time measurement.

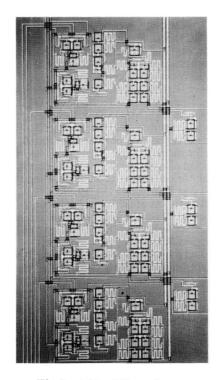

Fig.7. 4-bit digital counter.

bit ALU can be composed by connecting eight 2bit ALU in parallel. Additional circuits which generate both generation and propagation signals are required for carry bits. In this configuration, the operating speed of the 16-bit ALU is estimated

to be about 405ps.

A 4-bit digital counter[11] was designed using the 4JL-gate family and the directly-coupled datalatchs. Figure 7 shows a photograph of the 4-bit counter circuit which was fabricated with the 3µm Nb/Al-oxide/Nb junction technology described previously. The counter has three operating functions of counting, data-loading and clearing, adaptable for a program counter. The circuit size is 0.33mm x 1.4mm in which 103 4JL-gates are integrated. The counter was tested at 4.2K with the two-phase power supply, and the operations of every functions were confirmed. Operating speed of the 4-bit counter is estimated to be up to 3GHz with a power dissipation of 161µW.

A 4-bit shift-register [14] was also designed and fabricated. Figure 8 shows a photograph of the 4-bit shift-register circuit. The circuit size is about 0.3mm x 0.8mm. The register has four functions of shifting, data-loading, data-holding and clearing. Every functions were confirmed by supplying the two-phase power supply at 4.2K. The operating time is 195ps with a power dissipation of 116µW by computer simulations.

High speed multiplexer[15] was designed based on the 4JL OR-AND gate cell. Figure 9 shows the 4-bit multiplexer circuit fabricated using the 3µm Nb/Al-oxide/Nb junction technology. Four input signals are first stored in the latch to generate 4-bit dual outputs. In the second stage, the multiplexer circuit selects the one bit dual outputs from the 4-bits. The circuit tests were successfully carried out with the two-phase power supply. Every latch and multiplexer operation was confirmed. Operating delays were estimated to be 150ps and 60ps for the latch and the multiplexer, respectively.

These results show that the very complicated logic circuits such as CPU can be constructed by combining and extending these 4JL circuits developed here.

### VARIABLE THRESHOLD MEMORY TECHNOLOGY

It is very important to realize memory devices for constructing Josephson digital systems.

Fig.8. 4-bit shift-register.

Fig.9. 4-bit multiplexer.

Considerable efforts have been done to achieve full operations of memory chips. A complete operation of Josephson memories, however, has not yet been achieved in LSI levels. A main reason is that the tolerance required for fabrication of Josephson memory circuits is smaller than that current technology can offer. Therefore, new approaches are needed in both the fabrication process and the memory circuit design. A refractory junction process has been recently developed which gives a good uniformity of the critical current in circuits. The variable threshold memory cell has been proposed and developed, which has a large operating margin[16].

The variable threshold memory cell has a very simple structure, i.e., an equivalent asymmetrical dc SQUID structure without a sense gate in it. Figure 10 shows a schematic configuration of the cell, in which one of two junctions of the dc SQUID is a three-junction SQUID gate J1 functioning as a write gate