数字逻辑设计(VHDL)基础 Fundamentals of Digital Logic with VHDL Design (英文版)

斯蒂芬·布朗 (Stephen Brown) 兹翁科·弗拉内希奇 (Zvonko Vranesic)

### 时代教育·国外高校优秀教材精选

# 数字逻辑设计(VHDL)基础 (英文版)

Fundamentals of Digital Logic with VHDL Design

(美) 斯蒂芬・布朗 (Stephen Brown) 著兹翁科・弗拉内希奇 (Zvonko Vranesic)

Stephen Brown, Zvonko Vranesic

Fundamentals of Digital Logic with VHDL Design

ISBN: 0-07-012591-0

Copyright © 2000 by the McGraw-Hill Companies, Inc.

Original language published by The McGraw-Hill Companise, Inc. All Rights reserved. No part of this publication may be reproduced or distributed in any means, or stored in a database or retrieval system, without the prior written permission of the publisher.

Authorized English language reprint edition jointly published by McGraw-Hill Education (Asia) Co. and China Machine Press. This edition is authorized for sale in the People's Republic of China only, excluding Hong Kong, Macao SAR and Taiwan. Unauthorized export of this edition is a violation of the Copyright Act. Violation of this law is subject to Civil and Criminal Penalties.

本书英文影印版由<u>机械工业出版社</u>和美国麦格劳-希尔教育出版(亚洲)公司合作出版。此版本仅限在中华人民共和国境内(不包括香港、澳门特别行政区及台湾地区)销售。未经许可之出口,视为违反著作权法,将受法律之制裁。未经出版者预先书面许可,不得以任何方式复制或抄袭本书的任何部分。

本书封面贴有 McGraw-Hill 公司激光防伪标签,无标签者不得销售。 北京市版权局著作权合同登记号:图片:01-2002-1878号

#### 图书在版编目(CIP)数据

数字逻辑设计 (VHDL) 基础=Fundamentals of Digital Logic with VHDL Design/(美)朗(Brow, S.),(美)弗拉内希奇(Vranesic, Z.)著.—北京:机械工业出版社,2002,8

时代教育. 国外高校优秀教材精选 ISBN 7-111-10640-7

I. 数… Ⅱ. ①朗…②弗… Ⅲ. ①数字逻辑 - 逻辑设计 - 高等学校 - 教材 - 英文②硬件描述语言, VHDL - 程序设计 - 高等学校 - 教材 - 英文 Ⅳ. TP302. 2

中国版本图书馆 CIP 数据核字 (2002) 第 053664 号

机械工业出版社(北京市百万庄大街 22 号 邮政编码 100037)

责任编辑:周 娟 封面设计:鞠 杨

责任印制:付方敏

北京铭成印刷有限公司印刷·新华书店北京发行所发行

2002年5月第1版第1次印刷

1000mm×1400mm B5・26.625 印张・1029 千字

定价: 63.00 元

凡购本书,如有缺页、倒页、脱页,由本社发行部调换

本社购书热线电话 (010) 68993821、68326677-2527

封面无防伪标均为盗版

## 国外高校优秀教材审定委员会

主任委员: 杨叔子

委员 (按姓氏笔画为序):

CPLD 和 FPGA 这类复杂的用户可编程逻辑器件,正以其编程方便、集成度高、速度快、价格低等特点越来越受到电子设计者的青睐。VHDL 硬件描述语言是数字逻辑电路设计者的得力工具,是现代电子设计的基础语言。硬件描述语言的种类很多,成为 IEEE 标准的语言有两种: VHDL 和 VerilogHDL 语言。

目前已出版的很多关于 VHDL 语言的教材和参考书都是从语法规则、程序结构两个方面介绍的,从语言基础讲述数字逻辑的程序设计。

本书则是数字逻辑设计方面的入门教材,在介绍传统的数字逻辑电路基本概念的同时,引入 VHDL 语言的描述方法。书中采用 MAX+Plus II CAD 软件工具,其目的是在基本概念和实际应用之间,通过电子设计自动化(EDA)的 CAD 方法建立它们的桥梁,使初学者在学习数字逻辑电路的同时逐步掌握 VHDL 语言的描述方法。全书给出 100 多个设计例子,可边学习,边上机实验,在实验中掌握 VHDL 语言的描述方法,使本书更适合初学者自学。书中的例子由浅入深,对较难的设计例子进行了清楚的说明,从而构成本书的特色。本书由于起点较低,也可作为双语教材使用。

陈文楷 北京工业大学 2002 年 4 月

### 出版说明

随着我国加入 WTO, 国际间的竞争越来越激烈,而国际间的竞争实际上也就是人才的竞争、教育的竞争。为了加快培养具有国际竞争力的高水平技术人才,加快我国教育改革的步伐,教育部近来出台了一系列倡导高校开展双语教学、引进原版教材的政策。以此为契机,机械工业出版社拟于近期推出一系列国外影印版教材,其内容涉及高等学校公共基础课,以及机、电、信息领域的专业基础课和专业课。

引进国外优秀原版教材,在有条件的学校推动开展英语授课或双语教学,自然也引进了先进的教学思想和教学方法,这对提高我国自编教材的水平,加强学生的英语实际应用能力,使 我国的高等教育尽快与国际接轨,必将起到积极的推动作用。

为了做好教材的引进工作,机械工业出版社特别成立了由著名专家组成的国外高校优秀教材审定委员会。这些专家对实施双语教学做了深入细致的调查研究,对引进原版教材提出许多建设性意见,并慎重地对每一本将要引进的原版教材一审再审,精选再精选,确认教材本身的质量水平,以及权威性和先进性,以期所引进的原版教材能适应我国学生的外语水平和学习特点。在引进工作中,审定委员会还结合我国高校教学课程体系的设置和要求,对原版教材的教学思想和方法的先进性、科学性严格把关,同时尽量考虑原版教材的系统性和经济性。

这套教材出版后,我们将根据各高校的双语教学计划,举办原版教材的教师培训,及时地 将其推荐给各高校选用。希望高校师生在使用教材后及时反馈意见和建议,使我们更好地为教 学改革服务。

机械工业出版社 2002年3月

## **CONTENTS**

|     | <b>0 0 1</b> .                            | `    |                  |                                                            |

|-----|-------------------------------------------|------|------------------|------------------------------------------------------------|

| 序   |                                           |      |                  |                                                            |

| 出   | <b>饭说明</b>                                |      |                  |                                                            |

|     | apter 1                                   |      |                  |                                                            |

|     | ESIGN CONCEPTS 1                          | 2.9  | Introdu<br>2.9.1 | action to VHDL 51 Representation of Digital Signals in     |

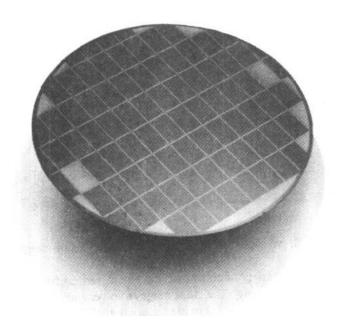

| 1.1 | Digital Hardware 2                        |      |                  | VHDL 52                                                    |

|     | 1.1.1 Standard Chips 4                    |      | 2.9.2            | Writing Simple VHDL Code 52                                |

|     | 1.1.2 Programmable Logic Devices 4        |      | 2.9.3            | How Not to Write VHDL Code 54                              |

|     | 1.1.3 Custom-Designed Chips 5             | 2.10 |                  | iding Remarks 55                                           |

| 1.2 | •                                         |      |                  | ms 56                                                      |

| 1.3 | Design of Digital Hardware 8              |      | Refere           | nces 60                                                    |

|     | 1.3.1 Basic Design Loop 8                 |      |                  |                                                            |

|     | 1.3.2 Design of a Digital Hardware Unit 9 |      | pter             |                                                            |

| 1.4 | Logic Circuit Design in this Book 12      | IMP  | LEME             | NTATION TECHNOLOGY 61                                      |

| 1.5 | Theory and Practice 14                    | 3.1  | Transia          | tor Switches 63                                            |

|     | References 15                             | 3.1  |                  |                                                            |

|     |                                           | 3.3  |                  | Logic Gates 65<br>Logic Gates 68                           |

|     | apter 2                                   | 3.3  | 3.3.1            | Speed of Logic Gate Circuits 75                            |

| INT | TRODUCTION TO LOGIC                       | 3.4  |                  | re Logic System 76                                         |

| CII | RCUITS 17                                 | 3.5  |                  | ed Chips 77                                                |

|     |                                           | 3.3  | 3.5.1            | 7400-Series Standard Chips 77                              |

| 2.1 | Variables and Functions 18                | 2.6  |                  |                                                            |

| 2.2 | Inversion 21                              | 3.6  | 3.6.1            | nmable Logic Devices 81  Programmable Logic Array (PLA) 81 |

| 2.3 | Truth Tables 22                           |      | 3.6.2            | Programmable Array Logic (PAL) 84                          |

| 2.4 | Logic Gates and Networks 23               |      | 3.6.3            | Programming of PLAs and PALs 86                            |

|     | 2.4.1 Analysis of a Logic Network 24      |      | 3.6.4            | Complex Programmable Logic Devices                         |

| 2.5 | Boolean Algebra 27                        |      | 3.0.1            | (CPLDs) 88                                                 |

|     | 2.5.1 The Venn Diagram 30                 |      | 3.6.5            | Field-Programmable Gate Arrays 92                          |

|     | 2.5.2 Notation and Terminology 34         |      | 3.6.6            | Using CAD Tools to Implement                               |

|     | 2.5.3 Precedence of Operations 34         |      |                  | Circuits in CPLDs and FPGAs 96                             |

| 2.6 | Synthesis Using AND, OR, and NOT          | 3.7  | Custom           | Chips, Standard Cells, and Gate                            |

|     | Gates 35                                  |      | Arrays           |                                                            |

|     | 2.6.1 Sum-of-Products and Product-of-Sums |      | •                | l Aspects 100                                              |

|     | Forms 37                                  |      | 3.8.1            | MOSFET Fabrication and Behavior 100                        |

| 2.7 | Design Examples 41                        |      | 3.8.2            | MOSFET On-Resistance 104                                   |

|     | 2.7.1 Three-Way Light Control 42          |      | 3.8.3            | Voltage Levels in Logic Gates 105                          |

|     | 2.7.2 Multiplexer Circuit 43              |      | 3.8.4            | Noise Margin 107                                           |

| 2.8 | Introduction to CAD Tools 45              | ;    | 3.8.5            | Dynamic Operation of Logic Gates 108                       |

|     | 2.8.1 Design Entry 46                     |      | 3.8.6            | Power Dissipation in Logic Gates 111                       |

|     | 2.8.2 Synthesis 48                        | -    | 3.8.7            | Passing 1s and 0s Through Transistor                       |

|     | 2.8.3 Functional Simulation 49            |      | • • •            | Switches 112                                               |

|     | 2.8.4 Summary 49                          |      | 3.8.8            | Fan-in and Fan-out in Logic Gates 114                      |

CONTENTS

| 3.9<br>3.10 | Transmission Gates 120 3.9.1 Exclusive-OR Gates 121 3.9.2 Multiplexer Circuit 122 Implementation Details for SPLDs, | CPLDs,     | Nt  |                       | r 5<br>REPRESENTATION<br>THMETIC CIRCUITS 217 |

|-------------|---------------------------------------------------------------------------------------------------------------------|------------|-----|-----------------------|-----------------------------------------------|

|             | and FPGAs 123                                                                                                       |            | 5.1 | Position              | onal Number Representation 218                |

|             | 3.10.1 Implementation in FPGAs 12                                                                                   | 29         |     | 5.1.1                 | Unsigned Integers 218                         |

| 3.11        | Concluding Remarks 131                                                                                              |            |     | 5.1.2                 | Conversion between Decimal                    |

|             | Problems 132                                                                                                        |            |     | 2111-2                | and Binary Systems 219                        |

|             | References 141                                                                                                      |            |     | 5.1.3                 | Octal and Hexadecimal<br>Representations 220  |

|             | apter 4                                                                                                             |            | 5.2 | Additi                | on of Unsigned Numbers 222                    |

|             | TIMIZED IMPLEMENTATION                                                                                              |            |     | 5.2.1                 | Decomposed Full-Adder 226                     |

| OF I        | Logic Functions 143                                                                                                 |            |     | 5.2.2                 | Ripple-Carry Adder 227                        |

|             | 77 1 1 1 1 1 1 1 1                                                                                                  |            |     | 5.2.3                 | Design Example 228                            |

| 4.1         | Karnaugh Map 144                                                                                                    |            | 5.3 |                       |                                               |

| 4.2         | Strategy for Minimization 152                                                                                       |            | 3.3 | •                     | Numbers 228                                   |

|             | 4.2.1 Terminology 153                                                                                               |            |     | 5.3.1                 | Negative Numbers 228                          |

|             | 4.2.2 Minimization Procedure 154                                                                                    | 150        |     | 5.3.2                 | Addition and Subtraction 232                  |

| 4.3         | Minimization of Product-of-Sums Fo                                                                                  |            |     | <b>5</b> .3. <b>3</b> | Adder and Subtractor Unit 236                 |

| 4.4         | Incompletely Specified Functions 1                                                                                  | 60         |     | 5.3.4                 | Radix-Complement Schemes 237                  |

| 4.5         | Multiple-Output Circuits 161                                                                                        |            |     | 5.3.5                 | Arithmetic Overflow 241                       |

| 4.6         | NAND and NOR Logic Networks 1                                                                                       | 65         |     | 5.3.6                 | Performance Issues 242                        |

| 1.7         | Multilevel Synthesis 167                                                                                            | 4          | 5.4 | Fast Ac               | lders 243                                     |

|             | 4.7.1 Factoring 168                                                                                                 |            |     | 5.4.1                 | Carry-Lookahead Adder 243                     |

|             | 4.7.2 Functional Decomposition 17                                                                                   |            | 5.5 | Design                | of Arithmetic Circuits Using CAD              |

|             | 4.7.3 Multilevel NAND and NOR Cit                                                                                   | rcuits 1// |     | Tools                 | _                                             |

| 8.1         | Analysis of Multilevel Circuits 180                                                                                 |            |     | 5.5.1                 | Design of Arithmetic Circuits Using           |

| 1.9         | Cubical Representation 185                                                                                          |            |     | 5.5.1                 | Schematic Capture 250                         |

|             | 4.9.1 Cubes and Hypercubes 185                                                                                      |            |     | 5.5.2                 | Design of Arithmetic Circuits Using           |

| .10         | Minimization Using Cubical                                                                                          |            |     | 3.5.2                 | VHDL 253                                      |

|             | Representation 189                                                                                                  | 100        |     | 5.5.3                 | Representation of Numbers in VHDL             |

|             | 4.10.1 Generation of Prime Implicants                                                                               |            |     | 0.5.5                 | Code 256                                      |

|             | 4.10.2 Determination of Essential Prim                                                                              | ie         |     | 5.5.4                 | Arithmetic Assignment Statements 258          |

|             | Implicants 192 4.10.3 Complete Procedure for Finding                                                                | . 5        | .6  |                       | ication 262                                   |

|             | 4.10.3 Complete Procedure for Finding a Minimal Cover 194                                                           | , 3        | .0  | -                     |                                               |

| 1.1         | Practical Considerations 196                                                                                        |            |     | 5.6.1                 | Array Multiplier for Unsigned Numbers 263     |

|             |                                                                                                                     |            |     | <b>5</b> ( 2          |                                               |

|             | CAD Tools 197 4.12.1 Logic Synthesis and Optimization                                                               | n 100 -    | _   |                       | Multiplication of Signed Numbers 264          |

|             | 4.12.1 Logic Synthesis and Optimization 4.12.2 Physical Design 199                                                  | 11 190 5.  |     |                       | umber Representations 267                     |

|             | 4.12.3 Timing Simulation 201                                                                                        |            |     | 5.7.1                 | Fixed-Point Numbers 267                       |

|             | 4.12.4 Summary of Design Flow 202                                                                                   |            |     | 5.7.2                 | Floating-Point Numbers 267                    |

|             | 4.12.5 Examples of Circuits Synthesize                                                                              | d          |     | 5.7.3                 | Binary-Coded-Decimal                          |

|             | from VHDL Code 204                                                                                                  | _          |     |                       | Representation 269                            |

| 13          | Concluding Remarks 210                                                                                              | 5.         | .8  | ASCII C               | Character Code 273                            |

|             | Problems 211                                                                                                        |            |     | Problem               | s 276                                         |

|             | References 214                                                                                                      |            |     | Reference             | ces 280                                       |

| C F     | napter 6                                                                       | 7.7 Summary of Terminology 350                                     |

|---------|--------------------------------------------------------------------------------|--------------------------------------------------------------------|

| C       | OMBINATIONAL-CIRCUIT                                                           | 7.8 Registers 350                                                  |

|         | UILDING BLOCKS 281                                                             | 7.8.1 Shift Register 351                                           |

| D       | CILDING DECERS 201                                                             | 7.8.2 Parallel-Access Shift Register 352                           |

| 6.1     | Multiplexers 282                                                               | 7.9 Counters 353                                                   |

|         | 6.1.1 Synthesis of Logic Functions Using                                       | 7.9.1 Asynchronous Counters 353                                    |

|         | Multiplexers 287                                                               | 7.9.2 Synchronous Counters 356                                     |

|         | 6.1.2 Multiplexer Synthesis Using Shannon's                                    | S 7.9.3 Counters with Parallel Load 360                            |

|         | Expansion 288                                                                  | 7.10 Reset Synchronization 360                                     |

| 6.2     | Decoders 295                                                                   | 7.11 Other Types of Counters 364                                   |

|         | 6.2.1 Demultiplexers 298                                                       | 7.11.1 BCD Counter 364                                             |

| 6.3     | Encoders 300                                                                   | 7.11.2 Ring Counter 365                                            |

|         | 6.3.1 Binary Encoders 300                                                      | 7.11.3 Johnson Counter 366                                         |

|         | 6.3.2 Priority Encoders 301                                                    | 7.11.4 Remarks on Counter Design 367                               |

| 6.4     | Code Converters 302                                                            | 7.12 Using Storage Elements with CAD Tools 367                     |

| 6.5     | Arithmetic Comparison Circuits 304                                             | 7.12.1 Including Storage Elements                                  |

| 6.6     | VHDL for Combinational Circuits 304                                            | in Schematics 367                                                  |

|         | 6.6.1 Assignment Statements 305                                                | 7.12.2 Using Latches and Flip-Flops in VHDL                        |

|         | 6.6.2 Selected Signal Assignment 305                                           | Code 370                                                           |

|         | 6.6.3 Conditional Signal Assignment 308                                        | 7.12.3 Using VHDL Sequential Statements                            |

|         | 6.6.4 Generate Statements 312                                                  | for Storage Elements 370                                           |

|         | 6.6.5 Concurrent and Sequential Assignment                                     | 7.13 Using Registers and Counters with CAD                         |

|         | Statements 315                                                                 | Tools 375                                                          |

|         | 6.6.6 Process Statement 315                                                    | 7.13.1 Including Registers and Counters                            |

|         | 6.6.7 Case Statement 321                                                       | in Schematics 375                                                  |

| 6.7     | Concluding Remarks 324                                                         | 7.13.2 Registers and Counters in VHDL                              |

|         | Problems 326                                                                   | Code 378                                                           |

|         | References 330                                                                 | 7.13.3 Using VHDL Sequential Statements                            |

|         |                                                                                | for Registers and Counters 379                                     |

| C h     | apter 7                                                                        | 7.14 Design Examples 387                                           |

| Fr.     | ip-Flops, Registers,                                                           | 7.14.1 Bus Structure 387                                           |

|         | UNTERS, AND A SIMPLE                                                           | 7.14.2 Simple Processor 400 7.14.3 Reaction Timer 413              |

|         | OCESSOR 331                                                                    |                                                                    |

| rk      | UCESSUR 551                                                                    | 7.15 Concluding Remarks 418                                        |

| 7.1     | Basic Latch 333                                                                | Problems 418                                                       |

| 7.2     | Gated SR Latch 335                                                             | References 424                                                     |

|         | 7.2.1 Gated SR Latch with NAND Gates 337                                       | / Chantan 9                                                        |

| 7.3     | Gated D Latch 338                                                              | Chapter o                                                          |

| 7.5     | 7.3.1 Effects of Propagation Delays 340                                        | Synchronous Sequential                                             |

| 7.4     | Master-Slave and Edge-Triggered                                                | CIRCUITS 427                                                       |

| . / . 🕶 | D Flip-Flops 341                                                               | 0.1 Paris Davies Stems 400                                         |

|         | 7.4.1 Master-Slave D Flip-Flop 341                                             | 8.1 Basic Design Steps 429                                         |

|         | 7.4.1 Master-Slave D Php-110p 341 7.4.2 Edge-Triggered D Flip-Flop 342         | 8.1.1 State Diagram 429                                            |

|         | 7.4.2 Eage-Higgered D Hip-Hop 342 7.4.3 D Flip-Flops with Clear and Preset 344 | 8.1.2 State Table 431                                              |

| 7.5     | T Flip-Flop 346                                                                | 0, 110 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                           |

| 1.5     | 7.5.1 Configurable Flip-Flops 349                                              | 8.1.4 Choice of Flip-Flops and Derivation of Next-State and Output |

| 7.6     | JK Flip-Flop 349                                                               | Expressions 433                                                    |

| 7.0     | VIX I IAP'I IUP UTV                                                            | DAPICOSIONO 433                                                    |

ix

|                            | 8.1.5                                                                                                                                            | Timing Diagram 435                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | C h             | apte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | r 9                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | 8.1.6                                                                                                                                            | Summary of Design Steps 436                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | .As             | VNCHI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RONOUS SEQUENTIAL                                                                                                                                                                                                                                                                                                                                                                     |

| 8.2                        | State-                                                                                                                                           | Assignment Problem 440                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | rs 515                                                                                                                                                                                                                                                                                                                                                                                |

|                            | 8.2.1                                                                                                                                            | One-Hot Encoding 442                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CI              | RCUII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5 515                                                                                                                                                                                                                                                                                                                                                                                 |

| 8.3                        | Mealy                                                                                                                                            | State Model 444                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9.1             | Async                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | chronous Behavior 516                                                                                                                                                                                                                                                                                                                                                                 |

| 8.4                        | Design                                                                                                                                           | n of Finite State Machines Using CAD                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9.2             | Analy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | sis of Asynchronous Circuits 519                                                                                                                                                                                                                                                                                                                                                      |

|                            | Tools                                                                                                                                            | 449                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9.3             | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | esis of Asynchronous Circuits 528                                                                                                                                                                                                                                                                                                                                                     |

|                            | 8.4.1                                                                                                                                            | VHDL Code for Moore-Type FSMs 449                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9.4             | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Reduction 540                                                                                                                                                                                                                                                                                                                                                                         |

|                            | 8.4.2                                                                                                                                            | Synthesis of VHDL Code 451                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9.5             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Assignment 555                                                                                                                                                                                                                                                                                                                                                                        |

|                            | 8.4.3                                                                                                                                            | Simulating and Testing the Circuit 454                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7.5             | 9.5.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Transition Diagram 558                                                                                                                                                                                                                                                                                                                                                                |

| *                          | 8.4.4                                                                                                                                            | An Alternative Style of VHDL Code 456                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 | 9.5.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Exploiting Unspecified Next-State                                                                                                                                                                                                                                                                                                                                                     |

|                            | 8.4.5                                                                                                                                            | Summary of Design Steps When Using                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 | J.U. <u>-</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Entries 561                                                                                                                                                                                                                                                                                                                                                                           |

|                            |                                                                                                                                                  | CAD Tools 456                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 | 9.5.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | State Assignment Using Additional                                                                                                                                                                                                                                                                                                                                                     |

|                            | 8.4.6                                                                                                                                            | Specifying the State Assignment in                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | State Variables 565                                                                                                                                                                                                                                                                                                                                                                   |

|                            | 0.47                                                                                                                                             | VHDL Code 458                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 | 9.5.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | One-Hot State Assignment 569                                                                                                                                                                                                                                                                                                                                                          |