PEARSON

国外电子与电气工程经典图书系列

Digital Systems: Principles and Applications

(Eleventh Edition)

(英文影印版)

# 国外电子与电气工程经典图书系列

# 数字系统原理及应用(英文影印版)

(第十一版)

# **Digital Systems: Principles and Applications**

(Eleventh Edition)

[美] Ronald J. Tocci Neal S. Widmer

科学出版社

## 内容简介

本书对现代数字系统的原理和技术进行了全面的论述,既讲述了数字系统的基本原理,又涵盖了应用数字电路设计中传统的和现代的设计方法及开发技术,包括如何处理系统层面的设计问题。另外,在提供数字电路和系统的所有重要基础内容的同时,还介绍了现在以及未来职业生涯中所需的很多实用工具。本书在内容体系上,先以符号和框图的形式讨论基本逻辑运算,分析组合逻辑电路及时序逻辑电路,在读者理解了数字电路的基本原理之后,再来讨论门电路及触发器的内部电路和电特性;同时,硬件描述语言(AHDL和VHDL)贯穿于各章节之中,不仅用来描述基本逻辑器件,而且用于设计简单的数字系统。此外,本书给出了丰富的例题、复习题、习题,每章末还有小结及重要术语,便于教学和自学。

本书可作为电类各专业信号与系统课程的双语教材或参考书,也可供工程技术人员参考。

Original edition, entitled *Digital Systems: Principles and Applications*, 11th Edition, 978-0-13-510382-1 by Ronald J. Tocci, published by Pearson Education, Inc, publishing as Pearson, Copyright © 2011 by Pearson Education. Inc.

All rights reserved. No part of this book may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage retrieval system, without permission from Pearson Education, Inc.

China edition published by PEARSON EDUCATION ASIA LTD., and SCIENCE PRESS LTD Copyright © 2012

Authorized for sale and distribution in the People's Republic of China exclusively (except Taiwan, Hong Kong SAR and Macau SAR). 本版本仅可在中国地区(除台湾、香港与澳门)销售与发行。本书封面贴有 Pearson Education (培生教育出版集团) 激光防伪标签。无标签者不得销售。

#### 图书在版编目(CIP)数据

数字系统原理及应用= Digital Systems:Principles and Applications: 11 版:英文/(美)托茨(Tocci, R. J.)等著. 一北京: 科学出版社, 2012

(国外电子与电气工程经典图书系列)

ISBN 978-7-03-032512-9

I.①数··· II.①托··· III. ①数字系统-高等学校-教材-英文 IV. ①TP271

中国版本图书馆 CIP 数据核字(2011)第 205196 号

责任编辑: 王鑫光 匡 敏/责任印制: 张克忠/封面设计: 迷底书装

# 科学出版社出版

北京东黄城根北街16号 邮政编码: 100717 http://www.sciencep.com

保定市中画美凯印刷有限公司 印刷

科学出版社发行 各地新华书店经销

2012年1月第 一 版 开本: 787×1092 1/16

2012年1月第一次印刷 印张: 61 1/4

字数: 14 500 000

定价: 149.00元

(如有印装质量问题, 我社负责调换)

To you, Cap, for loving me for so long; and for the million and one ways you brighten the lives of everyone you touch.

—RJT

To my father, Ed, who inspired my career in electronics; my mother, Gladys, who taught me the most important things in life, my wife, Kris, who is my helper and encourager; and all the great teachers whom I esteem as my role models.

-NSW

To my expanding family, Marita, David, Ryan, Christy, and Jeannie.

-GLM

This book is a comprehensive study of the principles and techniques of modern digital systems. It teaches the fundamental principles of digital systems and covers thoroughly both traditional and modern methods of applying digital design and development techniques, including how to manage a systems-level project. The book is intended for use in two- and four-year programs in technology, engineering, and computer science. Although a background in basic electronics is helpful, most of the material requires no electronics training. Portions of the text that use electronics concepts can be skipped without adversely affecting the comprehension of the logic principles.

#### What's New in This Edition?

The following list summarizes the improvements in the eleventh edition of Digital Systems. Details can be found in the section titled "Specific Changes" on page x.

- Revised introductory Chapter 1. By focusing on familiar telecommunications examples, this chapter demonstrates fundamental concepts in systems from the telegraph to the cell phone.

- More worked examples and figures have been added to chapters.

- More simple problems have been added to the problem sets at the end of the early chapters. Some more complex problems are added throughout as well.

- A new emphasis on the use of megafunctions, easily defined (using a software "wizard") fundamental building blocks for digital systems. This is in addition to extensive coverage of the fundamentals of hardware description languages.

- Chapter 10 has a new major section. A microwave oven controller is presented as a full system project showing all the steps of project management.

- Analog interfacing (Chapter 11) has been expanded to cover pipelined ADC and various examples of systems applications.

- Memory system material (Chapter 12) has been updated to describe the devices available today and what is projected for the future.

- FPGA coverage has been greatly updated in Chapter 13.

#### **General Features**

In industry today, getting a product to market very quickly is important. The use of modern design tools, CPLDs, and FPGAs allows engineers to progress from concept to functional silicon very quickly. Microcontrollers have taken over many applications that once were implemented by digital circuits, and DSP has been used to replace many analog circuits. It is amazing that microcontrollers, DSP, and all the necessary glue logic can now be consolidated onto a single FPGA using a hardware description language with advanced development tools. Today's students must be exposed to these modern tools, even in an introductory course. It is every educator's responsibility to find the best way to prepare graduates for the work they will encounter in their professional lives.

The standard SSI and MSI parts that have served as "bricks and mortar" in the building of digital systems for over 40 years are now nearing obsolescence. Many of the techniques that have been taught over that time have focused on optimizing circuits that are built from these outmoded devices. The topics that are uniquely suited to applying the old technology but do not contribute to an understanding of the new technology are being de-emphasized. From an educational standpoint, however, these small ICs do offer a way to study simple digital circuits, and the wiring of circuits using breadboards is a valuable pedagogic exercise. They help to solidify concepts such as binary inputs and outputs, physical device operation, and practical limitations, using a very simple platform. Consequently, we have chosen to continue to introduce the conceptual descriptions of digital circuits and to offer examples using conventional standard logic parts. For instructors who continue to teach the fundamentals using SSI and MSI circuits, this edition retains those qualities that have made the text so widely accepted in the past. Many hardware design tools even provide an easy-to-use design entry technique that will employ the functionality of conventional standard parts with the flexibility of programmable logic devices. A digital design can be described using a schematic drawing with pre-created building blocks that are equivalent to conventional standard parts, which can be compiled and then programmed directly into a target PLD with the added capability of easily simulating the design within the same development tool.

We believe that graduates will actually apply the concepts presented in this book using higher-level description methods and more complex programmable devices. The major shift in the field is a greater need to understand the description methods, rather than focusing on the architecture of an actual device. Software tools have evolved to the point where there is little need for concern about the inner workings of the hardware but much more need to focus on what goes in, what comes out, and how the designer can describe what the device is supposed to do. We also believe that graduates will be involved with projects using state-of-the-art design tools and hardware solutions.

This book offers a strategic advantage for teaching the vital topic of hardware description languages to beginners in the digital field. VHDL is undisputedly an industry standard language at this time, but it is also very complex and has a steep learning curve. Beginning students are often discouraged by the rigorous requirements of various data types, and they struggle with understanding edge-triggered events in VHDL. Fortunately, Altera offers AHDL,

Preface V

a less demanding language that uses the same basic concepts as VHDL but is much easier for beginners to master. So, instructors can opt to use AHDL to teach introductory students or VHDL for more advanced classes. This edition offers more than 40 AHDL examples, more than 40 VHDL examples, and many examples of simulation testing. All of these design files are available on the web site (www.pearsonhighered.com/electronics).

Altera's latest software development system is Quartus II. The material in this text does not attempt to teach a particular hardware platform or the details of using a software development system. We have chosen to show what this tool can do, rather than train the reader how to use it. However, tutorials have been included on the web site that make it easy to learn the software tools.

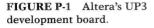

Max7000 series of CPLDs are still available and can be programmed through a simple parallel printer port interface or by using Altera/Terasic's usb-blaster interface cable. Complete development boards are available that offer the normal types of inputs and outputs like logic switches, pushbuttons, clock signals, LEDs, and 7-segment displays. Many boards also offer standard connectors for readily available computer hardware, such as a standard keyboard, computer mouse, VGA video monitor, COM ports, audio in/out jacks, plus two 40-pin general-purpose I/O ribbon connectors that allow connection to any digital peripheral hardware. The Altera UP3 development board is shown in Figure P-1. The Terasic DE0, DE1, and DE2 (shown in Figure P-2) boards are highly recommended for lab instruction and are available for a very reasonable price.

Our approach to HDL and PLDs gives instructors several options:

- The HDL material can be skipped entirely without affecting the continuity of the text.

- 2. HDL can be taught as a separate topic by skipping the material initially and then going back to the last sections of Chapters 3, 4, 5, 6, 7, and 9 and then covering Chapter 10.

- HDL and the use of PLDs can be covered as the course unfolds chapter by chapter—and woven into the fabric of the lecture/lab experience.

FIGURE P-2 Altera's DE2 development board.

Among all specific hardware description languages, VHDL is clearly the industry standard and is most likely to be used by graduates in their careers. We have always felt that it is a bold proposition, however, to try to teach VHDL in an introductory course. The nature of the syntax, the subtle distinctions in object types, and the higher levels of abstraction can pose obstacles for a beginner. For this reason, we have included Altera's AHDL as the recommended introductory language for freshman and sophomore courses. We have also included VHDL as the recommended language for more advanced classes or introductory courses offered to more mature students. We do not recommend trying to cover both languages in the same course. Sections of the text that cover the specifics of a language are clearly designated with a color bar in the margin. The HDL code figures are set in a color to match the color-coded text explanation. The reader can focus only on the language of his or her choice and skip the other. Obviously, we have attempted to appeal to the diverse interests of our market, but we believe we have created a book that can be used in multiple courses and will serve as an excellent reference after graduation.

# **Chapter Organization**

Many instructors opt to not use the chapters of a textbook in the sequence in which they are presented. This book was written so that, for the most part, each chapter builds on previous material, but it is possible to alter the chapter sequence somewhat. The first part of Chapter 6 (arithmetic operations) can be covered right after Chapter 2 (number systems), although this will lead to a long interval before the arithmetic circuits of Chapter 6 are encountered. Much of the material in Chapter 8 (IC characteristics) can be covered earlier (e.g., after Chapter 4 or 5) without creating any serious problems.

This book can be used either in a one-term course or in a two-term sequence. In a one-term course, limits on available class hours might require omitting some topics. Obviously, the choice of deletions will depend on factors such as program or course objectives and student background. Sections in each chapter that deal with troubleshooting, PLDs, HDLs, or microcomputer applications can be deferred to an advanced course.

FIGURE P-3 Letters denote categories of problems, and asterisks indicate that corresponding solutions are provided at the end of the text.

#### **PROBLEMS**

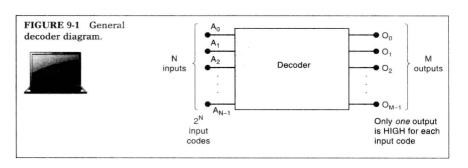

#### SECTION 9-1

- B 9-1. Refer to Figure 9-3. Determine the levels at each decoder output for the following sets of input conditions.

- (a)\*All inputs LOW

- (b)\*All inputs LOW except  $E_3 = HIGH$

- (c) All inputs HIGH except  $\overline{E}_1 = \overline{E}_2 = \text{LOW}$

- (d) All inputs HIGH

- B 9-2\*What is the number of inputs and outputs of a decoder that accepts 64 different input combinations?

**PROBLEM SETS** This edition includes six categories of problems: basic (B), challenging (C), troubleshooting (T), new (N), design (D), and HDL (H). Undesignated problems are considered to be of intermediate difficulty, between basic and challenging. Problems for which solutions are printed in the back of the text or on the web site (www.pearsonhighered.com/electronics) are marked with an asterisk (see Figure P-3).

**PROJECT MANAGEMENT AND SYSTEM-LEVEL DESIGN** Several real-world examples are included in Chapter 10 to describe the techniques used to manage projects. These applications are generally familiar to most students studying electronics, and the primary example of a digital clock is familiar to everyone. Many texts talk about top-down design, but this text demonstrates the key features of this approach and how to use the modern tools to accomplish it.

**SIMULATION FILES** This edition also includes simulation files that can be loaded into Electronics Workbench Multisim<sup>®</sup>. The circuit schematics of many of the figures throughout the text have been captured as input files for this popular simulation tool. Each file has some way of demonstrating the operation of the circuit or reinforcing a concept. In many cases, instruments are attached to the circuit and input sequences are applied to demonstrate the concept presented in one of the figures of the text. These circuits can then be modified as desired to expand on topics or create assignments and tutorials for students. All figures in the text that have a corresponding simulation file on the web site are identified by the icon shown in Figure P-4.

FIGURE P-4 The icon denotes a corresponding simulation file on the Web.

<sup>\*</sup>Answers to problems marked with an asterisk can be found in the back of the text.

## **Specific Changes**

The major changes in the topical coverage are listed here.

- Chapter 1. Casting a vision in the reader's mind is more important today than ever before. Modern digital systems are quite complex but can be used to demonstrate fundamental concepts. To show the reader that the principles are not new, but the methods to implement the principles have grown, Chapter 1 starts by explaining digital principles over the evolution of the telecommunications systems. The simple telegraph demonstrates the use of 1s and 0s to encode information. The telephone is used to demonstrate analog representation of a voice. Analog and digital representations are compared and contrasted in the context of a system. Finally, the new terminology and fundamentals of digital systems are shown to be combined in today's cell phones.

- Chapter 2. Many new problems were added as subparts to problems to further reinforce those concepts and give instructors more flexibility in assignments.

- Chapter 4. The material introducing PLD programming and development software has been updated and improved.

- Chapter 5. Changes include Quartus II schematic entry using standard library flip-flop and latch devices and versatile megafunction LPM components. Additional functional simulation examples are provided.

- Chapter 6. More Quartus II schematic entry examples are given. Emphasis is on easy-to-use megafunctions. Discussion of HDL adders has been simplified. Several new problems on arithmetic processes have been added.

- Chapter 7. This chapter has been revised to provide an alternate schematic capture approach to studying counters and registers with Quartus II megafunctions instead of just using standard MSI logic chips. More figures and examples have been added. Problems have been revised to allow course selection of design entry approach for schematics.

- Chapter 8. A new section that reviews the electrical characteristics of a representative FPGA has been added.

- Chapter 9. The use of megafunctions in Quartus to replace the legacy TTL standard parts functions is introduced for each major functional block.

- Chapter 10. A major new project example of a microwave oven controller is presented. It is decomposed into the fundamental building blocks that were presented throughout previous chapters, showing the role of each block and the signals that connect the blocks. This reinforces the need for several levels of hierarchy and demonstrates the strategic decisions that are made along the way. The fundamental blocks are left to be described/implemented by the reader as exercises similar to the many examples offered throughout previous chapters.

- Chapter 11. More example problems and figures have been added. The pipelined ADC technique is summarized. Example system applications for analog interfacing are discussed.

- Chapter 12. The generic descriptions of memory circuits are updated to show the most common control signals found on ICs today: tristate output enables and write enables. Read/Write bus cycle descriptions are updated as well. The material on Flash memory has been updated and made to more generically cover flash ICs today. A new topic is presented distinguishing between NAND and NOR flash technology: circuitry, features, advantages,

and disadvantages. Dynamic RAM is also updated with more general descriptions of typical ICs used today. Magnetoresistive memory is defined and explained to be a potentially major memory technology for the future. The section on optical memory is improved, and a new section on magnetic disk technology has been added.

Chapter 13. Example PLD devices have been updated to newer technology. Introductory material on older GAL chips has been reduced.

### **Retained Features**

This edition retains all of the features that made the previous editions so widely accepted. It utilizes a block diagram approach to teach the basic logic operations without confusing the reader with the details of internal operation. All but the most basic electrical characteristics of the logic ICs are withheld until the reader has a firm understanding of logic principles. In Chapter 8, the reader is introduced to the internal IC circuitry. At that point, the reader can interpret a logic block's input and output characteristics and "fit" it properly into a complete system.

The treatment of each new topic or device typically follows these steps: the principle of operation is introduced; thoroughly explained examples and applications are presented, often using actual ICs; short review questions are posed at the end of the section; and finally, in-depth problems are available at the end of the chapter. These problems, ranging from simple to complex, provide instructors with a wide choice of student assignments. These problems are often intended to reinforce the material without simply repeating the principles. They require students to demonstrate comprehension of the principles by applying them to different situations. This approach also helps students to develop confidence and expand their knowledge of the material.

The material on PLDs and HDLs is distributed throughout the text, with examples that emphasize key features in each application. These topics appear at the end of each chapter, making it easy to relate each topic to the general discussion earlier in the chapter or to address the general discussion separately from the PLD/HDL coverage.

The extensive troubleshooting coverage is spread over Chapters 4 through 12 and includes presentation of troubleshooting principles and techniques, case studies, 17 troubleshooting examples, and 46 *real* troubleshooting problems. When supplemented with hands-on lab exercises, this material can help foster the development of good troubleshooting skills.

This edition offers more than 220 worked-out examples, more than 660 review questions, and more than 640 chapter problems/exercises. Some of these problems are applications that show how the logic devices presented in the chapter are used in a typical microcomputer system. Answers to a majority of the problems immediately follow the Glossary. The Glossary provides concise definitions of all terms in the text that have been highlighted in boldface type.

An IC index is provided at the back of the book to help readers locate easily material on any IC cited or used in the text. The back endsheets provide tables of the most often used Boolean algebra theorems, logic gate summaries, and flip-flop truth tables for quick reference when doing problems or working in the lab.

## **Supplements**

An extensive complement of teaching and learning tools has been developed to accompany this textbook. Each component provides a unique function, and each can be used independently or in conjunction with the others.

#### WEB RESOURCES

- Quartus II Web Version software from Altera. This is the latest development system software from Altera, which offers more advanced features and supports new PLD devices such as the Cyclone family of FPGAs, found on many of the newest educational boards.

- Tutorials. Gregory Moss has developed tutorials that have been used successfully for several years to teach introductory students how to use Altera Quartus II software. These tutorials are available in PDF format. With the help of these tutorials, anyone can learn to modify and test all the examples presented in this text, as well as develop his or her own designs.

- Design files from the textbook figures. More than 40 design files in each language are presented in figures throughout the text. Students can load these into the Altera software and test them.

- Solutions to selected problems: HDL design files. A few of the end-of-chapter problem solutions are available to students. (All of the HDL solutions are available to instructors in the *Instructor's Resource Manual*.) Solutions for Chapter 7 problems include some large graphic and HDL files that are not published in the back of the book but are available on the web site.

- Circuits from the text rendered in Multisim<sup>®</sup>. Students can open and work interactively with approximately 100 circuits to increase their understanding of concepts and prepare for laboratory activities. The Multisim circuit files are provided for use by anyone who has Multisim software.

- Supplemental material introducing microprocessors and microcontrollers. For the flexibility to serve the diverse needs of the many different schools, an introduction to this topic is presented as a convenient bridge between a digital systems course and an introduction to microprocessors/microcontrollers course.

#### STUDENT RESOURCES

- Lab Manual: A Design Approach. This lab manual, written by Gregory Moss, contains topical units with lab projects that emphasize simulation and design. It utilizes the Altera Quartus II software in its programmable logic exercises and features both schematic capture and hardware description language techniques. The new edition contains many new projects and examples. (ISBN 0-13-215381-5)

- Lab Manual: A Troubleshooting Approach. This manual, written by Jim DeLoach and Frank Ambrosio, is presented with an analysis and troubleshooting approach. (ISBN 0-13-512395-X).

- Companion Website (www.pearsonhighered.com/tocci). This site offers students a free online study guide to help them review the material learned in the text and check their understanding of key topics.

#### INSTRUCTOR RESOURCES

Online Instructor's Resource Manual. This manual contains worked-out solutions for all end-of-chapter problems in this textbook. (ISBN 0-13-512385-2)

Preface

Online Lab Solutions Manual. Worked-out lab results for both lab manuals are featured in this manual. (ISBN 0-13-512382-8)

- Online PowerPoint<sup>®</sup> presentations. Figures from the text, in addition to Lecture Notes for each chapter, are available. (ISBN 0-13-512386-0)

- *Online TestGen.* A computerized test bank is available. (ISBN 0-13-512383-6)

To access supplementary materials online, instructors need to request an instructor access code. Go to www.pearsonhighered.com/irc, where you can register for an instructor access code. Within 48 hours after registering, you will receive a confirming e-mail, including an instructor access code. Once you have received your code, go to the site and log on for full instructions on downloading the materials you wish to use.

## Acknowledgments

We are grateful to all those who evaluated the tenth edition and provided answers to an extensive questionnaire:

Kyung Bae, Liberty University

Dr. Scott Grenquist, Wentworth Institute of Technology

Andy Huertaz, CNM Community College

Elias Kougianos, University of North Texas

Vern Sproat, Stark State College of Technology

Tristan Tayag, Texas Christian University

Emil Vazquez, Valencia Community College

Dr. Ece Yaprak, Wayne State University

Their comments, critiques, and suggestions were given serious consideration and were invaluable in determining the final form of the eleventh edition.

We also are greatly indebted to Professor Frank Ambrosio, Monroe Community College, for his usual high-quality work on the indexes and the *Instructor's Resource Manual*; and Professors Russ Aubrey and Gene Harding, Purdue University, for their technical review of topics and many suggestions for improvements. We appreciate the cooperation of the Altera Corporation for their support in granting permission to use their software package and their figures from technical publications.

A writing project of this magnitude requires conscientious and professional editorial support, and Prentice Hall came through again in typical fashion. We thank the staff at Prentice Hall and Sudip Sinha at Aptara® Corp. for their help to make this publication a success. We want to give special thanks and recognition to Lois Porter for the outstanding job she did as our copyeditor and proofreader, often helping us to identify technical errors in addition to improving our writing.

And finally, we want to let our wives and our children know how much we appreciate their support and their understanding. We hope that we can eventually make up for all the hours we spent away from them while we worked on this revision.

Ronald J. Tocci Neal S. Widmer Gregory L. Moss

**CHAPTER 1**

1-1

| 1-2  | Numerical Representations 6          |    |  |  |  |  |

|------|--------------------------------------|----|--|--|--|--|

| 1-3  | Digital and Analog Systems 9         |    |  |  |  |  |

| 1-4  | Digital Number Systems 14            |    |  |  |  |  |

| 1-5  | Representing Binary Quantities 18    |    |  |  |  |  |

| 1-6  | Digital Circuits/Logic Circuits 20   |    |  |  |  |  |

| 1-7  | Parallel and Serial Transmission 22  |    |  |  |  |  |

| 1-8  | Memory 23                            |    |  |  |  |  |

| 1-9  | Digital Computers 24                 |    |  |  |  |  |

|      |                                      |    |  |  |  |  |

|      |                                      |    |  |  |  |  |

| CHA  | PTER 2 Number Systems and Codes      | 32 |  |  |  |  |

| 2-1  | Binary-to-Decimal Conversions 34     |    |  |  |  |  |

| 2-2  | Decimal-to-Binary Conversions 35     |    |  |  |  |  |

| 2-3  | Hexadecimal Number System 37         |    |  |  |  |  |

| 2-4  | BCD Code 42                          |    |  |  |  |  |

| 2-5  | The Gray Code 44                     |    |  |  |  |  |

| 2-6  | Putting It All Together 46           |    |  |  |  |  |

| 2-7  | The Byte, Nibble, and Word 46        |    |  |  |  |  |

| 2-8  | Alphanumeric Codes 48                |    |  |  |  |  |

| 2-9  | Parity Method for Error Detection 50 |    |  |  |  |  |

| 2-10 | Applications 53                      |    |  |  |  |  |

|      |                                      |    |  |  |  |  |

|      |                                      |    |  |  |  |  |

**Introductory Concepts**

Introduction to Digital 1s and 0s 4

2

| CHAPTER 3 Describing Logic Circuits |                                                           |     |  |  |  |  |

|-------------------------------------|-----------------------------------------------------------|-----|--|--|--|--|

| 3-1                                 | Boolean Constants and Variables 67                        |     |  |  |  |  |

| 3-2                                 | Truth Tables 67                                           |     |  |  |  |  |

| 3-3                                 | OR Operation with OR Gates 68                             |     |  |  |  |  |

| 3-4                                 | AND Operation with AND Gates 72                           |     |  |  |  |  |

| 3-5                                 | NOT Operation 75                                          |     |  |  |  |  |

| 3-6                                 | Describing Logic Circuits Algebraically 76                |     |  |  |  |  |

| 3-7                                 | Evaluating Logic-Circuit Outputs 78                       |     |  |  |  |  |

| 3-8                                 | Implementing Circuits from Boolean<br>Expressions 81      |     |  |  |  |  |

| 3-9                                 | NOR Gates and NAND Gates 83                               |     |  |  |  |  |

| 3-10                                | Boolean Theorems 86                                       |     |  |  |  |  |

| 3-11                                | DeMorgan's Theorems 90                                    |     |  |  |  |  |

| 3-12                                | Universality of NAND Gates and NOR Gates 93               |     |  |  |  |  |

| 3-13                                | Alternate Logic-Gate Representations 96                   |     |  |  |  |  |

| 3-14                                | Which Gate Representation to Use 99                       |     |  |  |  |  |

| 3-15                                | Propagation Delay 105                                     |     |  |  |  |  |

| 3-16                                | Summary of Methods to Describe Logic Circuits 106         |     |  |  |  |  |

| 3-17                                | Description Languages Versus Programming<br>Languages 108 |     |  |  |  |  |

| 3-18                                | Implementing Logic Circuits with PLDs 110                 |     |  |  |  |  |

| 3-19                                | HDL Format and Syntax 112                                 |     |  |  |  |  |

| 3-20                                | Intermediate Signals 115                                  |     |  |  |  |  |

|                                     |                                                           |     |  |  |  |  |

| СНА                                 | PTER 4 Combinational Logic Circuits                       | 128 |  |  |  |  |

| 4-1                                 | Sum-of-Products Form 130                                  |     |  |  |  |  |

| 4-2                                 | Simplifying Logic Circuits 131                            |     |  |  |  |  |

| 4-3                                 | Algebraic Simplification 132                              |     |  |  |  |  |

| 4-4                                 | Designing Combinational Logic Circuits 137                |     |  |  |  |  |

| 4-5                                 | Karnaugh Map Method 143                                   |     |  |  |  |  |

| 4-6                                 | Exclusive-OR and Exclusive-NOR Circuits 154               |     |  |  |  |  |

| 4-7                                 | Parity Generator and Checker 159                          |     |  |  |  |  |

| 4-8                                 | Enable/Disable Circuits 161                               |     |  |  |  |  |

| 4-9                                 | Basic Characteristics of Digital ICs 163                  |     |  |  |  |  |

| 4-10                                | Troubleshooting Digital Systems 170                       |     |  |  |  |  |

| 4-11                                | Internal Digital IC Faults 172                            |     |  |  |  |  |

| 4-12                                | External Faults 176                                       |     |  |  |  |  |

| 4-13                                | Troubleshooting Case Study 178                            |     |  |  |  |  |

| 4-14                                | Programmable Logic Devices 180                            |     |  |  |  |  |

| 4-15                                | Representing Data in HDL 187                              |     |  |  |  |  |

| 4-16                                | Truth Tables Using HDL 191                                |     |  |  |  |  |

| 4-17                                | Decision Control Structures in HDL 194                    |     |  |  |  |  |

| CHA  | PTER 5     | Flip-Flops and Related Devices                | 218 |

|------|------------|-----------------------------------------------|-----|

| 5-1  | NAND Ga    | te Latch 221                                  |     |

| 5-2  | NOR Gate   | e Latch 226                                   |     |

| 5-3  | Troublesh  | nooting Case Study 229                        |     |

| 5-4  | Digital Pu | ulses 230                                     |     |

| 5-5  | Clock Sign | nals and Clocked Flip-Flops 231               |     |

| 5-6  | Clocked S  | -R Flip-Flop 234                              |     |

| 5-7  | Clocked J  | -K Flip-Flop 237                              |     |

| 5-8  | Clocked I  | Flip-Flop 240                                 |     |

| 5-9  | D Latch (  | Transparent Latch) 242                        |     |

| 5-10 | Asynchro   | nous Inputs 243                               |     |

| 5-11 |            | Timing Considerations 246                     |     |

| 5-12 |            | Timing Problem in FF Circuits 249             |     |

| 5-13 |            | Applications 251                              |     |

| 5-14 |            | Synchronization 251                           |     |

| 5-15 |            | g an Input Sequence 252                       |     |

| 5-16 |            | age and Transfer 253                          |     |

| 5-17 |            | ta Transfer: Shift Registers 255              |     |

| 5-18 |            | y Division and Counting 258                   |     |

| 5-19 | 7.43       | uputer Application 262                        |     |

| 5-20 |            | rigger Devices 264                            |     |

| 5-21 |            | (Monostable Multivibrator) 264                |     |

| 5-22 |            | nerator Circuits 268                          |     |

| 5-23 |            | nooting Flip-Flop Circuits 271                |     |

| 5-24 |            | al Circuits in PLDs Using Schematic Entry 276 |     |

| 5-25 |            | al Circuits Using HDL 280                     |     |

| 5-26 | _          | gered Devices 284                             |     |

| 5-27 |            | uits with Multiple Components 289             |     |

| СНА  | APTER 6    | Digital Arithmetic:                           | 200 |

|      | D: *       | Operations and Circuits                       | 308 |

| 6-1  | -          | Idition and Subtraction 310                   |     |

| 6-2  |            | ting Signed Numbers 311                       |     |

| 6-3  |            | in the 2's-Complement System 318              |     |

| 6-4  |            | on in the 2's-Complement System 319           |     |

| 6-5  |            | ation of Binary Numbers 322                   |     |

| 6-6  | -          | vision 323                                    |     |

| 6-7  |            | ition 324                                     |     |

| 6-8  |            | mal Arithmetic 326                            |     |

| 6-9  |            | ic Circuits 329                               |     |

| 6-10 |            | Binary Adder 330                              |     |

| 6-11 | Design of  |                                               |     |

6-12 Complete Parallel Adder with Registers 335

| 6-13 | Carry Propagation 337                            |     |

|------|--------------------------------------------------|-----|

| 6-14 | Integrated-Circuit Parallel Adder 338            |     |

| 6-15 | 2's-Complement Circuits 340                      |     |

| 6-16 | ALU Integrated Circuits 343                      |     |

| 6-17 | Troubleshooting Case Study 347                   |     |

| 6-18 | Using Altera Library Functions 349               |     |

| 6-19 | Logical Operations on Bit Arrays with HDLs 356   |     |

| 6-20 | HDL Adders 357                                   |     |

| 6-21 | Parameterizing the Bit Capacity of a Circuit 359 |     |

|      |                                                  |     |

| CHA  | PTER 7 Counters and Registers                    | 374 |

|      |                                                  | 3/4 |

| 7-1  | Asynchronous (Ripple) Counters 376               |     |

| 7-2  | Propagation Delay in Ripple Counters 380         |     |

| 7-3  | Synchronous (Parallel) Counters 382              |     |

| 7-4  | Counters with MOD Numbers $< 2^N$ 385            |     |

| 7-5  | Synchronous Down and Up/Down Counters 392        |     |

| 7-6  | Presettable Counters 394                         |     |

| 7-7  | IC Synchronous Counters 396                      |     |

| 7-8  | Decoding a Counter 406                           |     |

| 7-9  | Analyzing Synchronous Counters 409               |     |

| 7-10 | Synchronous Counter Design 413                   |     |

| 7-11 | Altera Library Functions for Counters 421        |     |

| 7-12 | HDL Counters 426                                 |     |

| 7-13 | Wiring HDL Modules Together 438                  |     |

| 7-14 | State Machines 446                               |     |

| 7-15 | Register Data Transfer 458                       |     |

| 7-16 | IC Registers 458                                 |     |

| 7-17 | Shift Register Counters 467                      |     |

| 7-18 | Troubleshooting 471                              |     |

| 7-19 | Megafunction Registers 474                       |     |

| 7-20 | HDL Registers 477                                |     |

| 7-21 | HDL Ring Counters 484                            |     |

| 7-22 | HDL One-Shots 485                                |     |

|      |                                                  |     |

| CHA  | PTER 8 Integrated-Circuit Logic Families         | 514 |

| 8-1  | Digital IC Terminology 516                       |     |

| 8-2  | The TTL Logic Family 525                         |     |

| 8-3  | TTL Data Sheets 529                              |     |

| 8-4  | TTL Series Characteristics 533                   |     |

| 8-5  | TTL Loading and Fan-Out 536                      |     |

| 8-6  | Other TTL Characteristics 541                    |     |

|      | 011                                              |     |

|      |                                                  |     |