国外电子信息精品著作(影印版)

# 智能AD和DA转换

# **Smart AD and DA Conversion**

Pieter Harpe Hans Hegt Arthur van Roermund

**黑**科学出版社

# 国外电子信息精品著作(影印版)

# Smart AD and DA Conversion 智能 AD 和 DA 转换

Pieter Harpe

Hans Hegt

Arthur van Roermund

斜 学 出 版 社 北 京

#### 内容简介

近年来, 工业变革带动了数字电路和模拟电路技术的发展。在数 模(DA)和模数(AD)的转换中,智能化的概念被提出,用来检测模拟量的缺 陷并加以修正。

本书首先介绍了当前数据转换设计领域的发展趋势和所面临的挑战, 并在宏观上阐述了智能转换的概念。然后,应用智能转换的概念,结合两个 设计实例,解决了具体的设计缺陷。最后得出结论:应用智能转换的概念, 转换器的芯片面积、功耗、静态精度和动态精度得到了改善,有效地提高了 DA 和 AD 的转换性能。

本书适应面广,无论对于该学科的专家、教授、研究生,还是本科生、普 通技术人员都有极大的参考价值。

Pieter Harpe, Hans Hegt, Arthur van Roermund: Smart AD and DA Conversion

Copyright © 2010 Springer

This reprint has been authorized by Springer-Verlag (Berlin/Heidelberg/ New York) for sale in the People's Republic of China only and not for export therefrom.

#### 图书在版编目(CIP)数据

智能 AD 和 DA 转换 = Smart AD and DA Conversion:英文/(美)哈比 (Harpe, P.)等编著. 一影印版. 一北京: 科学出版社, 2013

(国外电子信息精品著作)

ISBN 978-7-03-036496-8

Ⅰ.①智… Ⅱ.①哈… Ⅲ.①数字电路-电子技术-英文 ②模拟电路-电 子技术-英文 IV. ①TN79 ②TN710

中国版本图书馆 CIP 数据核字(2013)第 012663 号

责任编辑:余 丁/责任印制:张 倩/封面设计:陈

科学出版社出版

北京东黄城根北街 16 号 邮政编码:100717

http://www.sciencep.com

三河市骏老印刷厂 印刷

科学出版社发行 各地新华书店经销

2013年2月第 一 版 开本: B5(720×1000) 2013年2月第一次印刷 印张: 11 1/4 字数: 234 000

定价: 60.00元

(如有印装质量问题,我社负责调换)

Dr.ir. Pieter Harpe Holst Centre – IMEC High Tech Campus 31 Eindhoven 5656 AE The Netherlands pieter.harpe@imec-nl.nl web@pieterharpe.nl

Dr.ir. Hans Hegt

Department of Electrical Engineering

Eindhoven University of Technology

Den Dolech 2

Eindhoven

5612 AZ

The Netherlands

J.A.Hegt@tue.nl

Prof.dr.ir. Arthur van Roermund Department of Electrical Engineering Eindhoven University of Technology Den Dolech 2 Eindhoven 5612 AZ The Netherlands A.H.M.y.Roermund@tue.nl

Series Editors

Mohammed Ismail

Dept. Electrical and Computer Engineering

Ohio State University

Neil Avenue

43210

Columbus

US

ismail@ee.eng.ohio-state.edu

Mohamad Sawan Dépt. Génie Informatique Ecole Polytechnique de Montreal H3C 3A7 Montreal CA Mohamad.sawan@polymtl.ca

ISBN 978-90-481-9041-6 e-ISBN 978-90-481-9042-3 DOI 10.1007/978-90-481-9042-3 Springer Dordrecht Heidelberg London New York

Library of Congress Control Number: 2010927405

© Springer Science+Business Media B.V. 2010

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Cover design: eStudio Calamar S.L.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

# 《国外电子信息精品著作》序

20世纪90年代以来,信息科学技术成为世界经济的中坚力量。随着经济全球化的进一步发展,以微电子、计算机、通信和网络技术为代表的信息技术,成为人类社会进步过程中发展最快、渗透性最强、应用面最广的关键技术。信息技术的发展带动了微电子、计算机、通信、网络、超导等产业的发展,促进了生命科学、新材料、能源、航空航天等高新技术产业的成长。信息产业的发展水平不仅是社会物质生产、文化进步的基本要素和必备条件,也是衡量一个国家的综合国力、国际竞争力和发展水平的重要标志。在中国,信息产业在国民经济发展中占有举足轻重的地位,成为国民经济重要支柱产业。然而,中国的信息科学支持技术发展的力度不够,信息技术还处于比较落后的水平,因此,快速发展信息科学技术成为我国迫在眉睫的大事。

要使我国的信息技术更好地发展起来,需要科学工作者和工程技术人员付出 艰辛的努力。此外,我们要从客观上为科学工作者和工程技术人员创造更有利于 发展的环境,加强对信息技术的支持与投资力度,其中也包括与信息技术相关的 图书出版工作。

从出版的角度考虑。除了较好较快地出版具有自主知识产权的成果外,引进国外的优秀出版物是大有裨益的。洋为中用,将国外的优秀著作引进到国内,促进最新的科技成就迅速转化为我们自己的智力成果,无疑是值得高度重视的。科学出版社引进一批国外知名出版社的优秀著作,使我国从事信息技术的广大科学工作者和工程技术人员能以较低的价格购买,对于推动我国信息技术领域的科研与教学是十分有益的事。

此次科学出版社在广泛征求专家意见的基础上,经过反复论证、仔细遴选,共引进了接近30本外版书,大体上可以分为两类,第一类是基础理论著作,第二类是工程应用方面的著作。所有的著作都涉及信息领域的最新成果,大多数是2005年后出版的,力求"层次高、内容新、参考性强"。在内容和形式上都体现了科学出版社一贯奉行的严谨作风。

当然,这批书只能涵盖信息科学技术的一部分,所以这项工作还应该继续下去。对于一些读者面较广、观点新颖、国内缺乏的好书还应该翻译成中文出版,这有利于知识更好更快地传播。同时,我也希望广大读者提出好的建议,以改进和

完善丛书的出版工作。

总之,我对科学出版社引进外版书这一举措表示热烈的支持,并盼望这一工作取得更大的成绩。

中国科学院院士

中国科学院院士中国工程院院士2006年12月

# ANALOG CIRCUITS AND SIGNAL PROCESSING

Consulting Editor: Mohammed Ismail. Ohio State University

For other titles published in this series, go to www.springer.com/series/7381

# List of symbols and abbreviations

| Symbol      | Description                           | Unit              |

|-------------|---------------------------------------|-------------------|

| ADC         | Analog to digital converter           |                   |

| CSA         | Current source array                  |                   |

| $D_a$       | $R_{1,a} - R_{1,1}$                   |                   |

| DAC         | Digital to analog converter           |                   |

| DNL         | Differential non-linearity            | LSB               |

| $\Delta$    | Time-skew error                       | S                 |

| <b>ENOB</b> | Effective number of bits              | bit               |

| <b>ERBW</b> | Effective resolution bandwidth        | Hz                |

| FoM         | Figure of merit                       | J/conversion-step |

| FS          | Digital full scale amplitude          |                   |

| $f_s$       | Sampling frequency                    | Hz                |

| $G_e$       | Gain error                            |                   |

| INL         | Integral non-linearity                | LSB               |

| LSB         | Least significant bit                 |                   |

| M           | MLS order                             |                   |

| m           | MLS length                            |                   |

| MLS         | Maximum length sequence               |                   |

| MSB         | Most significant bit                  |                   |

| N           | Resolution                            | bit               |

| $O_e$       | Offset error                          | V, LSB            |

| $R_{a,b}$   | Discrete cross-correlation of a and b |                   |

| $R_s$       | Discrete auto-correlation of $s[n]$   |                   |

| r[n]        | Single-bit MLS                        |                   |

| s[n]        | Multi-bit MLS                         |                   |

| SFDR        | Spurious free dynamic range           |                   |

| SNDR        | Signal to noise and distortion ratio  |                   |

| SNR         | Signal to noise ratio                 |                   |

| THD         | Total harmonic distortion             |                   |

| T&H         | Track and hold                        |                   |

| u[n]        | Response to a multi-bit MLS           |                   |

| $V_{CM}$    | Common-mode voltage                   | V                 |

| $V_{fs}$    | Analog full scale amplitude           | V                 |

# **Contents**

| Lis | st of symbols and abbreviations |                                  | ix |

|-----|---------------------------------|----------------------------------|----|

| 1.  | INT                             | RODUCTION                        | 1  |

| 2.  | AD                              | AND DA CONVERSION                | 3  |

|     | 1                               | Introduction                     | 3  |

|     | 2                               | Trends in applications           | 4  |

|     | 3                               | Trends in technology             | 5  |

|     | 4                               | Trends in system design          | 6  |

|     | 5                               | Performance criteria             | 8  |

|     | 6                               | Conclusion                       | 9  |

| 3.  | SMA                             | ART CONVERSION                   | 11 |

|     | 1                               | Introduction                     | 11 |

|     | 2                               | Smart concept                    | 11 |

|     | 3                               | Application of the smart concept | 15 |

|     | 4                               | Focus in this work               | 16 |

|     | 5                               | Conclusion                       | 17 |

| 4.  | SMART DA CONVERSION             |                                  | 19 |

|     | 1                               | Introduction                     | 19 |

|     | 2                               | Area of current-steering DACs    | 21 |

|     | 3                               | Correction of mismatch errors    | 24 |

|     | 4                               | Sub-binary variable-radix DAC    | 25 |

|     |                                 |                                  |    |

|    | 5               | Design example                                      | 33  |

|----|-----------------|-----------------------------------------------------|-----|

|    | 6               | Conclusion                                          | 40  |

| 5. | DES             | SIGN OF A SUB-BINARY VARIABLE-RADIX DAC             | 41  |

|    | 1               | Schematic design                                    | 41  |

|    | 2               | Layout                                              | 45  |

|    | 3               | Self-measurement-circuit implementation             | 46  |

|    | 4               | Experimental results                                | 47  |

|    | 5               | Conclusion                                          | 54  |

| 6. | SM.             | ART AD CONVERSION                                   | 57  |

|    | 1               | Introduction                                        | 57  |

|    | 2               | Literature review                                   | 58  |

|    | 3               | High-speed high-resolution AD conversion            | 60  |

|    | 4               | Smart calibration                                   | 67  |

|    | 5               | Conclusion                                          | 70  |

| 7. | DES             | SIGN OF AN OPEN-LOOP T&H CIRCUIT                    | 73  |

|    | 1               | Literature review                                   | 73  |

|    | 2               | Design goal                                         | 75  |

|    | 3               | T&H architecture                                    | 75  |

|    | 4               | Sampling core architecture                          | 76  |

|    | 5               | Output buffer architecture                          | 78  |

|    | 6               | T&H design                                          | 88  |

|    | 7               | Experimental results                                | 91  |

|    | 8               | Conclusion                                          | 102 |

| 8. | T&H CALIBRATION |                                                     | 103 |

|    | 1               | Introduction                                        | 103 |

|    | 2               | T&H accuracy                                        | 104 |

|    | 3               | T&H calibration method                              | 105 |

|    | 4               | Analog correction parameters                        | 106 |

|    | 5               | Digitally assisted analog correction                | 113 |

|    | 6               | Simulation results                                  | 117 |

|    | 7               | Implementation of the calibration method and layout | 119 |

|    | 8               | Experimental results                                | 120 |

|    | 9               | Conclusion                                          | 124 |

| CC              | INIE | NIS                                                 | VII |

|-----------------|------|-----------------------------------------------------|-----|

| 9.              | Т&   | H CALIBRATION FOR TIME-INTERLEAVED ADCS             | 125 |

|                 | 1    | Introduction                                        | 125 |

|                 | 2    | Channel matching in time-interleaved T&H's          | 128 |

|                 | 3    | Channel mismatch calibration                        | 129 |

|                 | 4    | Channel mismatch detection                          | 132 |

|                 | 5    | Channel mismatch correction                         | 145 |

|                 | 6    | Simulation results                                  | 147 |

|                 | 7    | Implementation of the calibration method and layout | 149 |

|                 | 8    | Experimental results                                | 150 |

|                 | 9    | Conclusion                                          | 153 |

| 10. CONCLUSIONS |      | .155                                                |     |

| References      |      | 157                                                 |     |

| Inc             | lex  |                                                     | 163 |

# Chapter 1

# INTRODUCTION

The history of the application of semiconductors for controlling currents goes back all the way to 1926, in which Julius Lilienfeld filed a patent for a "Method and apparatus for controlling electric currents" [1], which is considered the first work on metal/semiconductor field-effect transistors. More well-known is the work of William Shockley, John Bardeen and Walter Brattain in the 1940s [2, 3], after which the development of semiconductor devices commenced. In 1958, independent work from Jack Kilby and Robert Noyce led to the invention of integrated circuits. A few milestones in IC design are the first monolithic operational amplifier in 1963 (Fairchild  $\mu$ A702, Bob Widlar) and the first one-chip 4-bit microprocessor in 1971 (Intel 4004).

Ever since the start of the semiconductor history, integration plays an important role: starting from single devices, ICs with basic functions were developed (e.g. opamps, logic gates), followed by ICs that integrate larger parts of a system (e.g. microprocessors, radio tuners, audio amplifiers). Following this trend of system integration, this eventually leads to the integration of analog and digital components in one chip, resulting in mixed-signal ICs: digital components are required because signal processing is preferably done in the digital domain; analog components are required because physical signals are analog by nature. Mixed-signal ICs are already widespread in many applications (e.g. audio, video); for the future, it is expected that this trend will continue, leading to a larger scale of integration.

Given the trend of mixed-signal integration, this leads to both new challenges and new opportunities with respect to the integrated analog components. Challenges are for example testing of the performance of analog components that are embedded inside a large system, or the fact that the IC technology is optimized for digital circuitry, which can be disadvantageous for analog components. On the other hand, the mixed-signal integration also gives

opportunities, like the possibility to shift parts of the system from the analog to the digital domain, or vice versa. From this point of view, the aim of this work is to investigate concepts to improve the performance of analog components by making use of the opportunities that are offered by mixed-signal system integration. This 'smart' concept will be applied to analog-to-digital and digital-to-analog converters, as these components are essential in mixed-signal systems.

The outline of this book is as follows: Chapter 2 studies trends and expectations in converter design with respect to applications, technology evolution and system design. Problems and opportunities are identified, and an overview of performance criteria is given. In Chapter 3, the smart concept is introduced that takes advantage of the expected opportunities (described in Chapter 2) in order to solve the anticipated problems. Chapters 4 and 5 apply the smart concept to digital-to-analog converters. In the discussed example, the concept is applied to reduce the area of the analog core of a current-steering DAC. In Chapter 4, the theory is presented while Chapter 5 discusses the implementation and experimental results. Chapter 6 up to Chapter 9 focus on the application of the smart concept to analog-to-digital converters. The main goal here is to improve the performance in terms of speed/power/accuracy. Chapter 6 introduces the general concept and defines key factors for the analog design and the smart approach in order to achieve the targeted high performance. Then, Chapter 7 deals with the analog design of an open-loop track-and-hold circuit. Experimental results are presented and compared against prior art. In Chapters 8 and 9, two calibration techniques are presented and experimentally verified by using the track-and-hold from Chapter 7. Finally, conclusions are drawn in Chapter 10.

# Chapter 2

# AD AND DA CONVERSION

This chapter studies trends and expectations in converter design with respect to applications, technology evolution and system design. Problems and opportunities are identified, and an overview of performance criteria is given. In Chapter 3, the smart concept is introduced that takes advantage of the expected opportunities in order to solve the anticipated problems.

#### 1. Introduction

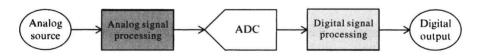

Electronic systems perform functions on many different types of signals, like: audio, video, medical images or RF communication signals. Despite the large variety, all signals are analog by nature in the physical world. However, at present most of the signal processing or signal storage is preferably performed in the digital domain. This leads to the need for analog-to-digital and digital-to-analog conversion. Actual systems can include both AD and DA conversion, or either one of the two. A general view on AD conversion is given in Fig. 2.1: the analog input signal is transferred to the digital domain through an ADC. Dependent on the situation, analog signal processing can be applied before the actual conversion, like pre-amplification, filtering or demodulation. Also, digital signal processing can be applied after the conversion, like error correction, filtering or data compression.

Figure 2.1. General view on AD conversion.

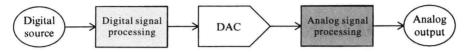

A general view on DA conversion is given in Fig. 2.2: the digital input signal is transferred to the analog domain through a DAC. Dependent on the situation, digital signal processing can be applied before the actual conversion, like encoding or filtering. Also, analog signal processing can be applied after the conversion, like modulation or filtering.

Figure 2.2. General view on DA conversion.

This work focusses on the actual AD and DA conversion, neglecting the other components of the signal processing chain.

# 2. Trends in applications

A trend in applications is that they typically demand a higher performance in terms of speed, accuracy, power consumption and chip-area. A motivation for the increase in demand is illustrated below.

#### Speed and accuracy

Over time, speed and accuracy requirements of an application are typically increasing. For example, the audio CD standard used 16 bit/44.1 kHz data, while current DVD players often use 24 bit/192 kHz. For digital still cameras, a 3 megapixel sensor with 12 bit dynamic range was state-of-the-art in 1999. Ten years later, state-of-the-art evolved to 25 megapixel sensors with 14 bit dynamic range. For wireless communication, the data-rate requirements are increasing, thus leading to a higher speed and/or accuracy requirement for the converters.

### Power

In many situations, the power consumption is an important factor: e.g. to prevent problems due to thermal heating or to extend the lifetime of a battery-operated device. For example, for the previously mentioned still cameras, the battery lifetime improved from 400 shots to 4,000 shots on one battery. Though the reasons for this improvement are diverse, it shows that reducing power consumption is an important feature.

#### Area

For all applications, the chip-area is a cost-factor. Thus, area reduction is preferable when possible.

Concluding, the trends in applications lead to the challenge that more and more performance is expected from the AD/DA converters. To meet this challenge, two important opportunities are: trends in technology and trends in system

design. Both these factors might be used beneficially as will be discussed in the following sections.

# 3. Trends in technology

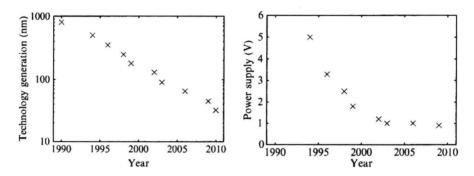

In technology development, the most important trend is down-scaling of the devices for each technology generation. Next to that, also the power supply is being reduced. Figure 2.3 shows the development of technology and power supply as a function of time for the UMC foundry [4]. While the technology scales down at a relatively constant rate, the power supply scaling flattens out because of threshold limitations.

Figure 2.3. Technology scaling and supply scaling as a function of time.

For digital designs, both trends are beneficial as they enable:

#### Higher speed

Because of the reduction of the dimensions of the devices and the interconnect, the associated capacitances are also reduced, resulting in a higher speed of operation.

## • Lower power-consumption

The power consumption of digital circuits is proportional to  $CV_{DD}^2$ . As both the capacitances and the supply are being reduced, the power consumption will also decrease.

#### Smaller area

The smaller dimensions result in a smaller area or a higher integration density.

On the other hand, the same trends are not necessarily beneficial for analog designs. For a noise-limited system, the noise-power requirement (kT/C) results in a minimum C-value to be implemented. Moreover, as the supply scales down, the signal power most likely also scales down, thus requiring

even an increase in C to maintain the SNR. Because of that, analog circuits do not directly take advantage of scaling to achieve a higher speed or a lower power-consumption. Apart from that, technology scaling also complicates analog design because of the following reasons:

#### Short channel effects

For smaller transistor geometries, secondary effects become more and more important. Because of that, the complexity of the transistor behavior increases, which complicates accurate circuit design.

### Low voltage operation

The reduced supply voltage limits the number of transistors that can be stacked, which complicates the implementation of certain circuit topologies.

While digital circuit design benefits from technology scaling, analog circuit design is getting more complicated. For mixed-signal designs, like AD and DA converters, it seems a logical option to shift some of the analog problems to the digital domain to be able to benefit from technology scaling.

# 4. Trends in system design

As mentioned previously in Chapter 1, there is a tendency to integrate more and more components of a system into a single chip. As signal processing is predominantly performed in the digital domain while physical signals are analog by nature, this leads to the integration of analog and digital components in one chip, resulting in mixed-signal ICs. For the integrated analog components, the system integration offers both new challenges and new opportunities. Some of the challenges that become more important because of the mixed-signal integration are the following:

#### • Hostile environment

Digital circuits create a hostile environment for the analog circuits by causing interference, which potentially reduces the performance of the analog circuits.

#### Testing

A stand-alone analog component can be tested directly for functionality or performance. On the other hand, analog components embedded in a large integrated system cannot be accessed directly, thus complicating test methodologies. A dedicated test-mode or an internal self-test strategy might be necessary to facilitate testing.

#### Yield

Especially when combining many different components into one integrated chip, the overall yield might be affected adversely by critical components.