TURING 图灵原版电子与电气工程系列

CAMBRIDGE

Digital Integrated Circuit Design

From VLSI Architectures to CMOS Fabrication

## 数字集成电路设计

从VLSI体系结构到CMOS制造

(英文版)

| Digital In<br>Circuit De                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | s to CMOS Fabrication |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| E SANCE DE LES CONTRACTOR DE L | HUBERT KAESLIN        |

TURING 图灵原版电子与电气工程系列

Digital Integrated Circuit Design

From VLSI Architectures to CMOS Fabrication

### 数字集成电路设计 从VLSI体系结构到CMOS制造

(英文版)

[瑞士] Hubert Kaeslin 著

人民邮电出版社 求 京

#### 图书在版编目(CIP)数据

数字集成电路设计:从VLSI体系结构到CMOS制造: 英文/(瑞士)克斯林(Kaeslin, H.)著.—北京:人 民邮电出版社,2010.5

(图灵原版电子与电气工程系列)

ISBN 978-7-115-22358-6

I. ①数… II. ①克… III. ①数字集成电路 - 电路设计 - 英文 IV. ① TN431.2

中国版本图书馆CIP数据核字 (2010) 第 030009 号

#### 内容提要

本书从架构与算法讲起,介绍了功能验证、VHDL建模、同步电路设计、异步数据获取、能耗与散热、信号完整性、物理设计、设计验证等必备技术,还讲解了VLSI经济运作与项目管理,并简单阐释了CMOS技术的基础知识,全面覆盖了数字集成电路的整个设计开发过程。

本书既可作为高等院校微电子、电子技术等相关专业高年级师生和研究生的参考教材,也可供半导体行业工程师参考。

#### 图灵原版电子与电气工程系列

#### 数字集成电路设计:从VLSI体系结构到CMOS制造(英文版)

◆ 著 [瑞士] Hubert Kaeslin

责任编辑 马晓燕

◆ 人民邮电出版社出版发行 北京市崇文区夕照寺街14号

邮编 100061 电子函件 315@ptpress.com.cn

网址 http://www.ptpress.com.cn

三河市海波印务有限公司印刷

◆ 开本:787×1092 1/16

印张:54.25

彩插:4

字数:872 千字

2010年5月第1版

印数:1-2000册

2010年 5月河北第 1 次印刷

著作权合同登记号 图字:01-2010-0206号

ISBN 978-7-115-22358-6

定价:119.00元

读者服务热线:(010) 51095186 印装质量热线:(010) 67129223 反盗版热线:(010) 67171154

#### 版权声明

Digital Integrated Circuit Design: From VLSI Architectures to CMOS Fabrication, First Edition (ISBN 9780521882675) by Hubert Kaeslin, first published by Cambridge University Press 2008.

All rights reserved.

This reprint edition for the People's Republic of China is published by arrangement with the Press Syndicate of the University of Cambridge, Cambridge, United Kingdom.

© Cambridge University Press & Posts & Telecom Press 2010.

This book is in copyright. No reproduction of any part may take place without the written permission of Cambridge University Press and Posts & Telecom Press.

This edition is for sale in the People's Republic of China (excluding Hong Kong SAR, Macao SAR and Taiwan Province) only.

此版本仅限在中华人民共和国境内(不包括香港、澳门特别行政区及台湾地区)销售。

#### **Preface**

#### Why this book?

Designing integrated electronics has become a multidisciplinary enterprise that involves solving problems from fields as disparate as

- Hardware architecture

- Software engineering

- · Marketing and investment

- Solid-state physics

- Systems engineering

- Circuit design

- Discrete mathematics

- Electronic design automation

- Layout design

- Hardware test equipment and measurement techniques

Covering all these subjects is clearly beyond the scope of this text and also beyond the author's proficiency. Yet, I have made an attempt to collect material from the above fields that I have found to be relevant for deciding whether or not to develop digital Very Large Scale Integration (VLSI) circuits, for making major design decisions, and for carrying out the actual engineering work.

The present volume has been written with two audiences in mind. As a textbook, it wants to introduce engineering students to the beauty and the challenges of digital VLSI design while preventing them from repeating mistakes that others have made before. Practising electronics engineers should find it appealing as a reference book because of its comprehensiveness and the many tables, checklists, diagrams, and case studies intended to help them not to overlook important action items and alternative options when planning to develop their own hardware components.

What sets this book apart from others in the field is its top-down approach. Beginning with hardware architectures, rather than with solid-state physics, naturally follows the normal VLSI design flow and makes the material more accessible to readers with a background in systems engineering, information technology, digital signal processing, or management.

#### Highlights

- Most aspects of digital VLSI design covered

- Top-down approach from algorithmic considerations to wafer processing

- Systematic overview on architecture optimization techniques

- Scalable concepts for simulation testbenches including code examples

- Emphasis on synchronous design and HDL code portability

- Comprehensive discussion of clocking disciplines

- Key concepts behind HDLs without too many syntactical details

- A clear focus on the predominant CMOS technology and static circuit style

- Just as much semiconductor physics as digital VLSI designers really need to know

- Models of industrial cooperation

- What to watch out for when purchasing virtual components

- Cost and marketing issues of ASICs

- Avenues to low-volume fabrication

- Largely self-contained (required previous knowledge summarized in two appendices)

- Emphasis on knowledge likely to remain useful in the years to come

- Many illustrations that facilitate recognizing a problem and the options available

- Checklists, hints, and warnings for various situations

- A concept proven in classroom teaching and actual design projects

#### A note to instructors

Over the past decade, the capabilities of field-programmable logic devices, such as FPGAs and CPLDs, have grown to a point where they have become invaluable ingredients of many electronic products, especially of those designed and marketed by small and medium-sized enterprises. Beginning with the higher levels of abstraction enables instructors to focus on those topics that are equally relevant irrespective of whether a design eventually gets implemented as a mask-programmed custom chip or from components that are just configured electrically. This material is collected in chapters 1 to 5 of the book and best taught as part of the Bachelor degree for maximum dissemination. No prior introduction to semiconductors is required. For audiences with little exposure to digital logic and finite state machines, the material can always be complemented with appendices A and B.

Learning how to design mask-programmed VLSI chips is then open to Master students who elect to specialize in the field. Designing electronic circuits down to that level of detail involves many decisions related to electrical, physical, and technological issues. An abstraction to purely logical models is no longer valid since side effects may cause an improperly designed circuit to behave differently than anticipated from digital simulations. How to cope with clock skew, metastability, layout parasitics, ground bounce, crosstalk, leakage, heat, electromigration, latch-up, electrostatic discharge, and process variability in fact makes up much of the material from chapter 6 onwards.

Again, the top-down organization of the book leaves much freedom as to where to end a class. A shorter course might skip chapter 8 as well as all material on detailed layout design that begins with section 11.5 on the grounds that only few digital designers continue to address device-level issues today. A similar argument also applies to the CMOS semiconductor technology introduced in chapter 14. Chapter 13, on the other hand, should not be dropped because, by definition, there are no engineering projects without economic issues playing a decisive role.

For those primarily interested in the business aspects of microelectronics, it is even possible to put together a quick introductory tour from chapters 1, 13, and 15 leaving out all the technicalities associated with actual chip design.

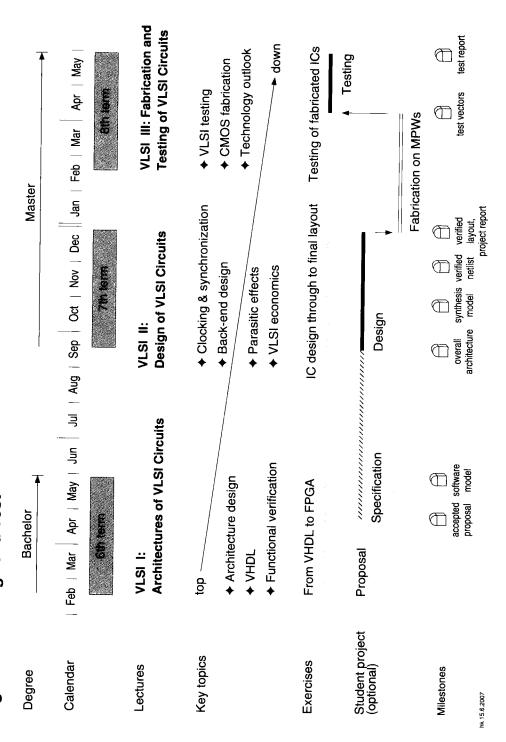

The figure below explains how digital VLSI is being taught by the author and his colleagues at the ETH. Probably the best way of preparing for an engineering career in the electronics and microelectronics industry is to complete a design project where circuits are not just being modeled and simulated on a computer but actually fabricated. Provided they come up with a meaningful project proposal, our students are indeed given this opportunity, typically working in teams of two. Following tapeout at the end of the 7th term, chip fabrication via an external multi-project wafer service takes roughly three months. Circuit samples then get systematically tested by their very developers in their 8th and final term. Needless to say that students accepting this offer feel very motivated and that industry highly values the practical experience of graduates formed in this way.

The technical descriptions and procedures in this book have been developed with the greatest of care; however, they are provided as is, without warranty of any kind. The author and editors of the book make no warranties, expressed or implied, that the equations, programs, and procedures in this book are free of error, or are consistent with any particular standard of merchantability, or will meet your requirements for any particular application. They should not be relied upon for solving a problem whose incorrect solution could result in injury to a person or loss of property.

# Syllabus of ETH Zurich in Digital VLSI Design and Test

#### Acknowledgements

This volume collects the insight and the experience that many persons have accumulated over the last couple of years. While I was fortunate enough to compile the text, I am indebted to all those who have been willing to share their expertise with me.

My thanks thus go not only to my superiors at the ETH Zürich, Switzerland, Professors Wolfgang Fichtner, Qiuting Huang, and Rüdiger Vahldieck, but also to many past and present colleagues of mine including Dr. Dölf Aemmer, Professor Helmut Bölcskei, Dr. Heinz Bonnenberg, Dr. Andreas Burg, Felix Bürgin, Professor Mike Ciletti, Dr. Flavio Carbognani, Dr. Andreas Curiger, Stefan Eberli, Dr. Nobert Felber, Dr. Steffen Gappisch, Dr. Ronald Gull, Dr. Simon Häne, Kurt Henggeler, Dr. Lucas Heusler, Peter Lüthi, Dr. Chiara Martelli, Dieter Müller, Stephan Oetiker, Dr. David Perels, Dr. Robert Rogenmoser, Andreas Romer, Dr. Fritz Rothacher, Dr. Thomas Röwer, Dr. Manfred Stadler, Dr. Andreas Stricker, Christoph Studer, Thomas Thaler, Dr. Markus Thalmann, Jürg Treichler, Dr. Thomas Villiger, Dr. Jürgen Wassner, Dr. Marc Wegmüller, Markus Wenk, Dr. Rumi Zahir, and Dr. Reto Zimmermann. Most of these experts have also reviewed parts of my manuscript and helped to improve its quality. Still, the only person to blame for all errors and other shortcomings that have remained in the text is me.

Next, I would like to express my gratitude towards all of the students who have followed the courses on Digital VLSI Design and Testing jointly given by Dr. Nobert Felber and myself. Not only their comments and questions, but also results and data from many of their projects have found their way into this text. André Meyer and Thomas Peter deserve special credit as they have conducted analyses specifically for the book.

Giving students the opportunity to design microchips, to have them fabricated, and to test physical samples is a rather onerous undertaking that would clearly have been impossible without the continuous funding by the ETH Zürich. We are also indebted to Professor Fichtner for always having encouraged us to turn this vision into a reality and to numerous Europractice partners and industrial companies for access to EDA software, design kits, and low-volume manufacturing services.

The staff of the Microelectronics Design Center at the ETH Zürich and various IT support people at the Integrated Systems Laboratory, including Christoph Balmer, Matthias Brändli, Thomas Kuch, and Christoph Wicki, do or did a superb job in setting up and maintaining the EDA infrastructure and the services indispensable for VLSI design in spite of the frequent landslides caused by rapid technological evolution and by unforeseeable business changes. I am particularly grateful to them for occasionally filling all sorts of gaps in my technical knowledge without making me feel too badly about it.

I am further indebted to Dr. Frank Gürkaynak and Professor Yusuf Leblebici of the EPFL in Lausanne, Switzerland, for inciting me to turn my lecture notes into a textbook and for their advice. In a later phase, Dr. Julie Lancashire, Anna Littlewood, and Dawn Preston of Cambridge University Press had to listen to all my silly requests before they managed to get me acquainted with the realitities of printing and publishing. Umesh Vishwakarma of TeX Support is credited for preparing bespoke style files for the book, Christian Benkeser and Yves Saad for contributing the cover graphics.

Finally, I would like to thank all persons and organizations who have taken the time to answer my reprint requests and who have granted me the right to reproduce illustrations of theirs.

#### Contents

| Ch  | apter 1 Introduction to Microelectronics                                  | 1  |

|-----|---------------------------------------------------------------------------|----|

| 1.1 | Economic impact                                                           | 1  |

|     | Concepts and terminology                                                  | 4  |

|     | 1.2.1 The Guinness book of records point of view                          | 4  |

|     | 1.2.2 The marketing point of view                                         | 5  |

|     | 1.2.3 The fabrication point of view                                       | 6  |

|     | 1.2.4 The design engineer's point of view                                 | 10 |

|     | 1.2.5 The business point of view                                          | 17 |

| 1.3 | Design flow in digital VLSI                                               | 18 |

|     | 1.3.1 The Y-chart, a map of digital electronic systems                    | 18 |

|     | 1.3.2 Major stages in VLSI design                                         | 19 |

|     | 1.3.3 Cell libraries                                                      | 28 |

|     | 1.3.4 Electronic design automation software                               | 29 |

| 1.4 | Field-programmable logic                                                  | 30 |

|     | 1.4.1 Configuration technologies                                          | 30 |

|     | 1.4.2 Organization of hardware resources                                  | 32 |

|     | 1.4.3 Commercial products                                                 | 35 |

| 1.5 | Problems                                                                  | 37 |

| 1.6 | Appendix I: A brief glossary of logic families                            | 38 |

| 1.7 | Appendix II: An illustrated glossary of circuit-related terms             | 40 |

| Ch  | apter 2 From Algorithms to Architectures                                  | 44 |

| 2.1 | The goals of architecture design                                          | 44 |

|     | 2.1.1 Agenda                                                              | 45 |

| 2.2 | The architectural antipodes                                               | 45 |

|     | 2.2.1 What makes an algorithm suitable for a dedicated VLSI architecture? | 50 |

|     | 2.2.2 There is plenty of land between the architectural antipodes         | 53 |

|     | 2.2.3 Assemblies of general-purpose and dedicated processing units        | 54 |

|     | 2.2.4 Coprocessors                                                        | 55 |

|     | 2.2.5 Application-specific instruction set processors                     | 55 |

|     | 2.2.6 Configurable computing                                              | 58 |

|     | 2.2.7 Extendable instruction set processors                               | 59 |

|     | 2.2.8 Digest                                                              | 60 |

| 2.3 | A transform approach to VLSI architecture design                          | 61 |

|     | 2.3.1 There is room for remodelling in the algorithmic domain             | 62 |

|     | 2.3.2 and there is room in the architectural domain                       | 64 |

|     | 2.3.3 Systems engineers and VLSI designers must collaborate               | 64 |

|     | 2.3.4. A graph-based formalism for describing processing algorithms       | 65 |

| CONTENTS | _ xi |

|----------|------|

|          |      |

|      | 2.3.5 The isomorphic architecture                                       | 66  |

|------|-------------------------------------------------------------------------|-----|

|      | 2.3.6 Relative merits of architectural alternatives                     | 67  |

|      | 2.3.7 Computation cycle versus clock period                             | 69  |

| 2.4  | Equivalence transforms for combinational computations                   | 70  |

|      | 2.4.1 Common assumptions                                                | 71  |

|      | 2.4.2 Iterative decomposition                                           | 72  |

|      | 2.4.3 Pipelining                                                        | 75  |

|      | 2.4.4 Replication                                                       | 79  |

|      | 2.4.5 Time sharing                                                      | 81  |

|      | 2.4.6 Associativity transform                                           | 86  |

|      | 2.4.7 Other algebraic transforms                                        | 87  |

|      | 2.4.8 Digest                                                            | 87  |

| 2.5  | Options for temporary storage of data                                   | 89  |

|      | 2.5.1 Data access patterns                                              | 89  |

|      | 2.5.2 Available memory configurations and area occupation               | 89  |

|      | 2.5.3 Storage capacities                                                | 90  |

|      | 2.5.4 Wiring and the costs of going off-chip                            | 91  |

|      | 2.5.5 Latency and timing                                                | 91  |

|      | 2.5.6 Digest                                                            | 92  |

| 2.6  | Equivalence transforms for nonrecursive computations                    | 93  |

|      | 2.6.1 Retiming                                                          | 94  |

|      | 2.6.2 Pipelining revisited                                              | 95  |

|      | 2.6.3 Systolic conversion                                               | 97  |

|      | 2.6.4 Iterative decomposition and time-sharing revisited                | 98  |

|      | 2.6.5 Replication revisited                                             | 98  |

|      | 2.6.6 Digest                                                            | 99  |

| 2.7  | Equivalence transforms for recursive computations                       | 99  |

|      | 2.7.1 The feedback bottleneck                                           | 100 |

|      | 2.7.2 Unfolding of first-order loops                                    | 101 |

|      | 2.7.3 Higher-order loops                                                | 103 |

|      | 2.7.4 Time-variant loops                                                | 105 |

|      | 2.7.5 Nonlinear or general loops                                        | 106 |

|      | 2.7.6 Pipeline interleaving is not an equivalence transform             | 109 |

|      | 2.7.7 Digest                                                            | 111 |

| 2.8  | Generalizations of the transform approach                               | 112 |

|      | 2.8.1 Generalization to other levels of detail                          | 112 |

|      | 2.8.2 Bit-serial architectures                                          | 113 |

|      | 2.8.3 Distributed arithmetic                                            | 116 |

|      | 2.8.4 Generalization to other algebraic structures                      |     |

|      | 2.8.5 Digest                                                            | 118 |

| 2.9  | Conclusions                                                             | 121 |

|      | 2.9.1 Summary                                                           | 122 |

|      | 2.9.2 The grand architectural alternatives from an energy point of view | 122 |

|      | 2.9.3 A guide to evaluating architectural alternatives                  | 124 |

| 2.10 | Problems                                                                | 126 |

|      | ·                                                                       | 128 |

| 2.11 Appendix I: A brief glossary of algebraic structures                | 130 |

|--------------------------------------------------------------------------|-----|

| 2.12 Appendix II: Area and delay figures of VLSI subfunctions            | 133 |

| Chapter 3   Functional Verification                                      | 136 |

| 3.1 How to establish valid functional specifications                     | 137 |

| 3.1.1 Formal specification                                               | 138 |

| 3.1.2 Rapid prototyping                                                  | 138 |

| 3.2 Developing an adequate simulation strategy                           | 139 |

| 3.2.1 What does it take to uncover a design flaw during simulation?      | 139 |

| 3.2.2 Stimulation and response checking must occur automatically         | 140 |

| 3.2.3 Exhaustive verification remains an elusive goal                    | 142 |

| 3.2.4 All partial verification techniques have their pitfalls            | 143 |

| 3.2.5 Collecting test cases from multiple sources helps                  | 150 |

| 3.2.6 Assertion-based verification helps                                 | 150 |

| 3.2.7 Separating test development from circuit design helps              | 151 |

| 3.2.8 Virtual prototypes help to generate expected responses             | 153 |

| 3.3 Reusing the same functional gauge throughout the entire design cycle | 153 |

| 3.3.1 Alternative ways to handle stimuli and expected responses          | 155 |

| 3.3.2 Modular testbench design                                           | 156 |

| 3.3.3 A well-defined schedule for stimuli and responses                  | 156 |

| 3.3.4 Trimming run times by skipping redundant simulation sequences      | 159 |

| 3.3.5 Abstracting to higher-level transactions on higher-level data      | 160 |

| 3.3.6 Absorbing latency variations across multiple circuit models        | 164 |

| 3.4 Conclusions                                                          | 166 |

| 3.5 Problems                                                             | 168 |

| 3.6 Appendix I: Formal approaches to functional verification             | 170 |

| 3.7 Appendix II: Deriving a coherent schedule for simulation and test    | 171 |

| Chapter 4   Modelling Hardware with VHDL                                 | 175 |

| 4.1 Motivation                                                           | 175 |

| 4.1.1 Why hardware synthesis?                                            | 175 |

| 4.1.2 What are the alternatives to VHDL?                                 | 176 |

| 4.1.3 What are the origins and aspirations of the IEEE 1076 standard?    | 176 |

| 4.1.4 Why bother learning hardware description languages?                | 179 |

| 4.1.5 Agenda                                                             | 180 |

| 4.2 Key concepts and constructs of VHDL                                  | 180 |

| 4.2.1 Circuit hierarchy and connectivity                                 | 181 |

| 4.2.2 Concurrent processes and process interaction                       | 185 |

| 4.2.3 A discrete replacement for electrical signals                      | 192 |

| 4.2.4 An event-based concept of time for governing simulation            | 200 |

| 4.2.5 Facilities for model parametrization                               | 211 |

| 4.2.6 Concepts borrowed from programming languages                       | 216 |

| 4.3 Putting VHDL to service for hardware synthesis                       | 223 |

| 4.3.1 Synthesis overview                                                 | 223 |

|     | 4.3.2 Data types                                                          | 224 |

|-----|---------------------------------------------------------------------------|-----|

|     | 4.3.3 Registers, finite state machines, and other sequential subcircuits  | 225 |

|     | 4.3.4 RAMs, ROMs, and other macrocells                                    | 231 |

|     | 4.3.5 Circuits that must be controlled at the netlist level               | 233 |

|     | 4.3.6 Timing constraints                                                  | 234 |

|     | 4.3.7 Limitations and caveats for synthesis                               | 238 |

|     | 4.3.8 How to establish a register transfer-level model step by step       | 238 |

| 4.4 | Putting VHDL to service for hardware simulation                           | 242 |

|     | 4.4.1 Ingredients of digital simulation                                   | 242 |

|     | 4.4.2 Anatomy of a generic testbench                                      | 242 |

|     | 4.4.3 Adapting to a design problem at hand                                | 245 |

|     | 4.4.4 The VITAL modelling standard IEEE 1076.4                            | 245 |

| 4.5 | Conclusions                                                               | 247 |

| 4.6 | Problems                                                                  | 248 |

| 4.7 | Appendix I: Books and Web Pages on VHDL                                   | 250 |

| 4.8 | Appendix II: Related extensions and standards                             | 251 |

|     | 4.8.1 Protected shared variables IEEE 1076a                               | 251 |

|     | 4.8.2 The analog and mixed-signal extension IEEE 1076.1                   | 252 |

|     | 4.8.3 Mathematical packages for real and complex numbers IEEE 1076.2      | 253 |

|     | 4.8.4 The arithmetic packages IEEE 1076.3                                 | 254 |

|     | 4.8.5 A language subset earmarked for synthesis IEEE 1076.6               | 254 |

|     | 4.8.6 The standard delay format (SDF) IEEE 1497                           | 254 |

|     | 4.8.7 A handy compilation of type conversion functions                    | 255 |

| 4.9 | Appendix III: Examples of VHDL models                                     | 256 |

|     | 4.9.1 Combinational circuit models                                        | 256 |

|     | 4.9.2 Mealy, Moore, and Medvedev machines                                 | 261 |

|     | 4.9.3 State reduction and state encoding                                  | 268 |

|     | 4.9.4 Simulation testbenches                                              | 270 |

|     | 4.9.5 Working with VHDL tools from different vendors                      | 285 |

| Ch  | apter 5 The Case for Synchronous Design                                   | 286 |

|     | Introduction                                                              | 286 |

| 5.2 | The grand alternatives for regulating state changes                       | 287 |

|     | 5.2.1 Synchronous clocking                                                | 287 |

|     | 5.2.2 Asynchronous clocking                                               | 288 |

|     | 5.2.3 Self-timed clocking                                                 | 288 |

| 5.3 | Why a rigorous approach to clocking is essential in VLSI                  | 290 |

|     | 5.3.1 The perils of hazards                                               | 290 |

|     | 5.3.2 The pros and cons of synchronous clocking                           | 291 |

|     | 5.3.3 Clock-as-clock-can is not an option in VLSI                         | 293 |

|     | 5.3.4 Fully self-timed clocking is not normally an option either          | 294 |

|     | 5.3.5 Hybrid approaches to system clocking                                | 294 |

| 5.4 | The dos and don'ts of synchronous circuit design                          | 296 |

|     | 5.4.1 First guiding principle: Dissociate signal classes!                 | 296 |

|     | 5.4.2 Second guiding principle: Allow circuits to settle before clocking! | 298 |

|     | 5.4.3 Synchronous design rules at a more detailed level                   | 298 |

|-----|---------------------------------------------------------------------------|-----|

| 5.5 | Conclusions                                                               | 306 |

| 5.6 | Problems                                                                  | 306 |

| 5.7 | Appendix: On identifying signals                                          | 307 |

|     | 5.7.1 Signal class                                                        | 307 |

|     | 5.7.2 Active level                                                        | 308 |

|     | 5.7.3 Signaling waveforms                                                 | 309 |

|     | 5.7.4 Three-state capability                                              | 311 |

|     | 5.7.5 Inputs, outputs, and bidirectional terminals                        | 311 |

|     | 5.7.6 Present state vs. next state                                        | 312 |

|     | 5.7.7 Syntactical conventions                                             | 312 |

|     | 5.7.8 A note on upper- and lower-case letters in VHDL                     | 313 |

|     | 5.7.9 A note on the portability of names across EDA platforms             | 314 |

| Ch  | apter 6 Clocking of Synchronous Circuits                                  | 315 |

| 6.1 | What is the difficulty in clock distribution?                             | 315 |

|     | 6.1.1 Agenda                                                              | 316 |

|     | 6.1.2 Timing quantities related to clock distribution                     | 317 |

| 6.2 | How much skew and jitter does a circuit tolerate?                         | 317 |

|     | 6.2.1 Basics                                                              | 317 |

|     | 6.2.2 Single-edge-triggered one-phase clocking                            | 319 |

|     | 6.2.3 Dual-edge-triggered one-phase clocking                              | 326 |

|     | 6.2.4 Symmetric level-sensitive two-phase clocking                        | 327 |

|     | 6.2.5 Unsymmetric level-sensitive two-phase clocking                      | 331 |

|     | 6.2.6 Single-wire level-sensitive two-phase clocking                      | 334 |

|     | 6.2.7 Level-sensitive one-phase clocking and wave pipelining              | 336 |

| 6.3 | How to keep clock skew within tight bounds                                | 339 |

|     | 6.3.1 Clock waveforms                                                     | 339 |

|     | 6.3.2 Collective clock buffers                                            | 340 |

|     | 6.3.3 Distributed clock buffer trees                                      | 343 |

|     | 6.3.4 Hybrid clock distribution networks                                  | 344 |

|     | 6.3.5 Clock skew analysis                                                 | 345 |

| 6.4 | How to achieve friendly input/output timing                               | 346 |

|     | 6.4.1 Friendly as opposed to unfriendly I/O timing                        | 346 |

|     | 6.4.2 Impact of clock distribution delay on I/O timing                    | 347 |

|     | 6.4.3 Impact of PTV variations on I/O timing                              | 349 |

|     | 6.4.4 Registered inputs and outputs                                       | 350 |

|     | 6.4.5 Adding artificial contamination delay to data inputs                | 350 |

|     | 6.4.6 Driving input registers from an early clock                         | 351 |

|     | 6.4.7 Tapping a domain's clock from the slowest component therein         | 351 |

|     | 6.4.8 "Zero-delay" clock distribution by way of a DLL or PLL              | 352 |

| 6.5 | How to implement clock gating properly                                    | 353 |

|     | 6.5.1 Traditional feedback-type registers with enable                     | 353 |

|     | 6.5.2 A crude and unsafe approach to clock gating                         | 354 |

|     | 6.5.3 A simple clock gating scheme that may work under certain conditions | 355 |

| CON. | ΓENTS |

|------|-------|

|------|-------|

| ٠ | ٠ |

|---|---|

|   | ٦ |

|     | 6.5.4 Safe clock gating schemes                                   | 355 |

|-----|-------------------------------------------------------------------|-----|

| 6.6 | Summary                                                           | 357 |

| 6.7 | Problems                                                          | 361 |

| Cł  | napter 7 Acquisition of Asynchronous Data                         | 364 |

| 7.1 | Motivation                                                        | 364 |

|     | The data consistency problem of vectored acquisition              | 366 |

|     | 7.2.1 Plain bit-parallel synchronization                          | 366 |

|     | 7.2.2 Unit-distance coding                                        | 367 |

|     | 7.2.3 Suppression of crossover patterns                           | 368 |

|     | 7.2.4 Handshaking                                                 | 369 |

|     | 7.2.5 Partial handshaking                                         | 371 |

| 7.3 | The data consistency problem of scalar acquisition                | 373 |

|     | 7.3.1 No synchronization whatsoever                               | 373 |

|     | 7.3.2 Synchronization at multiple places                          | 373 |

|     | 7.3.3 Synchronization at a single place                           | 373 |

|     | 7.3.4 Synchronization from a slow clock                           | 374 |

| 7.4 | Metastable synchronizer behavior                                  | 374 |

|     | 7.4.1 Marginal triggering and how it becomes manifest             | 374 |

|     | 7.4.2 Repercussions on circuit functioning                        | 378 |

|     | 7.4.3 A statistical model for estimating synchronizer reliability | 379 |

|     | 7.4.4 Plesiochronous interfaces                                   | 381 |

|     | 7.4.5 Containment of metastable behavior                          | 381 |

|     | Summary                                                           | 384 |

| 7.6 | Problems                                                          | 384 |

| Ch  | apter 8 Gate- and Transistor-Level Design                         | 386 |

| 8.1 | CMOS logic gates                                                  | 386 |

|     | 8.1.1 The MOSFET as a switch                                      | 387 |

|     | 8.1.2 The inverter                                                | 388 |

|     | 8.1.3 Simple CMOS gates                                           | 396 |

|     | 8.1.4 Composite or complex gates                                  | 399 |

|     | 8.1.5 Gates with high-impedance capabilities                      | 403 |

|     | 8.1.6 Parity gates                                                | 406 |

| 0.0 | 8.1.7 Adder slices                                                | 407 |

| 8.2 | CMOS bistables                                                    | 409 |

|     | 8.2.1 Latches                                                     | 410 |

|     | 8.2.2 Function latches                                            | 412 |

|     | 8.2.3 Single-edge-triggered flip-flops                            | 413 |

|     | 8.2.4 The mother of all flip-flops                                | 415 |

|     | 8.2.5 Dual-edge-triggered flip-flops                              | 417 |

|     | 8.2.6 Digest                                                      | 418 |

| 8.3 | CMOS on-chip memories                                             | 418 |

|     |                                                                   |     |

| ~~ |   |    | h 1- |    |

|----|---|----|------|----|

| CO | N | ıE | IN   | ıs |

xvi

|     | 8.3.1 Static RAM                                            | 418 |

|-----|-------------------------------------------------------------|-----|

|     | 8.3.2 Dynamic RAM                                           | 423 |

|     | 8.3.3 Other differences and commonalities                   | 424 |

| 8.4 | Electrical CMOS contraptions                                | 425 |

|     | 8.4.1 Snapper                                               | 425 |

|     | 8.4.2 Schmitt trigger                                       | 426 |

|     | 8.4.3 Tie-off cells                                         | 427 |

|     | 8.4.4 Filler cell or fillcap                                | 428 |

|     | 8.4.5 Level shifters and input/output buffers               | 429 |

|     | 8.4.6 Digitally adjustable delay lines                      | 429 |

| 8.5 | Pitfalls                                                    | 430 |

|     | 8.5.1 Busses and three-state nodes                          | 430 |

|     | 8.5.2 Transmission gates and other bidirectional components | 434 |

|     | 8.5.3 What do we mean by safe design?                       | 437 |

|     | 8.5.4 Microprocessor interface circuits                     | 438 |

|     | 8.5.5 Mechanical contacts                                   | 440 |

|     | 8.5.6 Conclusions                                           | 440 |

| 8.6 | Problems                                                    | 442 |

| 8.7 | Appendix I: Summary on electrical MOSFET models             | 445 |

|     | 8.7.1 Naming and counting conventions                       | 445 |

|     | 8.7.2 The Sah model                                         | 446 |

|     | 8.7.3 The Shichman-Hodges model                             | 450 |

|     | 8.7.4 The alpha-power-law model                             | 450 |

|     | 8.7.5 Second-order effects                                  | 452 |

|     | 8.7.6 Effects not normally captured by transistor models    | 455 |

|     | 8.7.7 Conclusions                                           | 456 |

| 8.8 | Appendix II: The Bipolar Junction Transistor                | 457 |

| Ch  | antor O Energy Efficiency and Heat Democrat                 |     |

| CII | apter 9   Energy Efficiency and Heat Removal                | 459 |

| 9.1 | What does energy get dissipated for in CMOS circuits?       | 459 |

|     | 9.1.1 Charging and discharging of capacitive loads          | 460 |

|     | 9.1.2 Crossover currents                                    | 465 |

|     | 9.1.3 Resistive loads                                       | 467 |

|     | 9.1.4 Leakage currents                                      | 468 |

|     | 9.1.5 Total energy dissipation                              | 470 |

|     | 9.1.6 CMOS voltage scaling                                  | 471 |

| 9.2 | How to improve energy efficiency                            | 474 |

|     | 9.2.1 General guidelines                                    | 474 |

|     | 9.2.2 How to reduce dynamic dissipation                     | 476 |

|     | 9.2.3 How to counteract leakage                             | 482 |

| 9.3 | Heat flow and heat removal                                  | 488 |

| 9.4 | Appendix I: Contributions to node capacitance               | 490 |

| 9.5 | Appendix II: Unorthodox approaches                          | 491 |

|     | 9.5.1 Subthreshold logic                                    | 491 |

|     | 9.5.2 Voltage-swing-reduction techniques                    | 492 |

| ,    | 9.5.3 Adiabatic logic                                           | 492 |

|------|-----------------------------------------------------------------|-----|

| Cha  | pter 10 Signal Integrity                                        | 495 |

| 10.1 | Introduction                                                    | 495 |

|      | 10.1.1 How does noise enter electronic circuits?                | 495 |

|      | 10.1.2 How does noise affect digital circuits?                  | 496 |

|      | 10.1.3 Agenda                                                   | 499 |

| 10.2 | Crosstalk                                                       | 499 |

|      | Ground bounce and supply droop                                  | 499 |

|      | 10.3.1 Coupling mechanisms due to common series impedances      | 499 |

|      | 10.3.2 Where do large switching currents originate?             | 501 |

|      | 10.3.3 How severe is the impact of ground bounce?               | 501 |

| 10.4 | How to mitigate ground bounce                                   | 504 |

| -01- | 10.4.1 Reduce effective series impedances                       | 505 |

|      | 10.4.2 Separate polluters from potential victims                | 510 |

|      | 10.4.3 Avoid excessive switching currents                       | 513 |

|      | 10.4.4 Safeguard noise margins                                  | 517 |

| 10.5 | Conclusions                                                     | 519 |

| 10.6 | Problems                                                        | 519 |

| 10.7 | Appendix: Derivation of second-order approximation              | 521 |

| Cha  | apter 11 Physical Design                                        | 523 |

| 11.1 | Agenda                                                          | 523 |

| 11.2 | Conducting layers and their characteristics                     | 523 |

|      | 11.2.1 Geometric properties and layout rules                    | 523 |

|      | 11.2.2 Electrical properties                                    | 527 |

|      | 11.2.3 Connecting between layers                                | 527 |

|      | 11.2.4 Typical roles of conducting layers                       | 529 |

| 11.3 | Cell-based back-end design                                      | 531 |

|      | 11.3.1 Floorplanning                                            | 531 |

|      | 11.3.2 Identify major building blocks and clock domains         | 532 |

|      | 11.3.3 Establish a pin budget                                   | 533 |

|      | 11.3.4 Find a relative arrangement of all major building blocks | 534 |

|      | 11.3.5 Plan power, clock, and signal distribution               | 535 |

|      | 11.3.6 Place and route (P&R)                                    | 538 |

|      | 11.3.7 Chip assembly                                            | 539 |

| 11.4 | Packaging                                                       | 540 |

|      | 11.4.1 Wafer sorting                                            | 543 |

|      | 11.4.2 Wafer testing                                            | 543 |

|      | 11.4.3 Backgrinding and singulation                             | 544 |

|      | 11.4.4 Encapsulation                                            | 544 |

|      | 11.4.5 Final testing and binning                                | 544 |

|      | 11.4.6 Bonding diagram and bonding rules                        | 545 |

|      | 11.4.7 Advanced packaging techniques                            | 546 |